# UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

\_\_\_\_\_

Innoscience (Zhuhai) Technology Company, Ltd., and Innoscience America, Inc., Petitioner,

v.

Efficient Power Conversion Corporation, Patent Owner.

Case No. IPR2023-01384 U.S. Patent No. 10,312,335

Declaration of Shauna L. Wiest Regarding Widmann and Uemoto

# I. Introduction

- 1. I have prepared this Declaration in connection with the Innoscience (Petitioner) Petition for *Inter Partes* Review of U.S. Patent No. 10,312,335 which I understand will be filed concurrently with this Declaration.

- 2. I am currently a senior research analyst with the Research & Information Services team at Finnegan, Henderson, Farabow, Garrett & Dunner, LLP located at 3300 Hillview Avenue, Palo Alto, CA 94304.

- 3. I am over eighteen years of age, and I am competent to make this Declaration. I make this Declaration based on my own personal knowledge, and my knowledge of library science practices.

- 4. I earned a Master of Science in Library Science degree from the University of North Carolina at Chapel Hill in 1999, and a Bachelor of Arts in Political Science degree from the University of California at San Diego in 1989. I have worked as a law librarian for over eighteen years. I have been employed in the Research & Information Services Department at Finnegan, Henderson, Farabow, Garrett & Dunner, LLP since 2021. Before that, from 2000-2015, I was employed as a Law Librarian at Stoel Rives LLP, and from 2015-2016, I was employed as a Competitive Intelligence Specialist for Nossaman LLP. I am also an active member of the American Association of Law Libraries.

# II. Standard Library Practices for Receiving, Cataloging, and Making Materials Publicly Available

- 5. I have knowledge of and experience with standard library practices regarding the receipt, cataloging, shelving, and making materials, including serial publications, available to the public. I have knowledge of and experience with the Machine-Readable Cataloging (MARC) system, an industry-wide standard that libraries use to catalog materials.

- 6. The MARC record system was developed during the 1960s to standardize bibliographic catalog records so they could be read by computers and shared among libraries. By the mid-1970s, MARC had become the international standard for cataloging bibliographic materials and is still used today. Many libraries provide public access to their MARC records via the Internet and/or their electronic cataloging systems at the library. In a MARC record, each field provides specific information about the cataloged item, including how materials are held and when they were catalogued and made available to the public.

# III. MARC Record Field Tags

7. The MARC record system uses specific three-digit numeric codes ("field tags") from 001-999 to identify each field in a catalog record. For example, field tag 008 provides the six-digit date the item was received and catalogued (Date entered on file). The first six characters of field tag 008 are always in the

"YYMMDD" format. Descriptions for all of the character positions of field tag 008 are outlined here: https://www.loc.gov/marc/bibliographic/bd008a.html

- 8. MARC field tag 022 provides the International Standard Serial Number (ISSN), a unique identification number assigned to a serial publication. MARC filed tag 260 sets forth the place of publication, name of publisher, and copyright/publication date of the publication. Finally, MARC field tags 9XX provide local holdings information to assist the public in identifying the location of the desired resource.

- 9. Based on standard library practice, when a library receives an item, it stamps (and/or labels) the item with the library name, barcode, often with a date that is within a few days or weeks of receipt. Next, the library will catalog the item within a matter of a few days or weeks of receiving it.

- 10. Generally, after an item is cataloged, the public may access the item by searching the library catalog, browsing the library shelves, and either requesting or electronically accessing the item from the library. Standard library practice is to make the item available to the public within a few days or weeks of cataloging it.

# IV. Serial Publications

11. A serial publication, often known as a "journal" or "periodical," is a resource that is issued in successive parts and has no predetermined conclusion.

These successive parts are commonly referred to as "issues," and each issue is

usually chronologically numbered and dated. The presence of enumeration, years of coverage, frequency, and/or other chronological information also indicates a serial publication.

12. There are significant differences between cataloging finite resources (books/monographs) and continuing resources (serials). For serials, the catalog record provides information about the serial as a whole, including the first or earliest available issue. It also provides information as to holdings – the volumes and issues, with dates, received by the library and made available to the public. In serials cataloging, there are identifying characteristics unique to serials that are slightly different from monographs (books). The issue date for a print serial publication, for example, generally appears on the cover (front or back), the masthead page, the title page (if any), the table of contents page(s), or on the pages of the individual articles contained in the issue. More information regarding the unique aspects of cataloguing serials can be found at this link: https://www.loc.gov/aba/pcc/conser/scctppt/Basic-2014/Basic-Trainee-Mannual.pdf

- V. Public Availability of Widmann (EX 1023)

- Section five of this Declaration relates to the date of public 13. availability for the following reference: D. W. Widmann, "Metallization for integrated circuits using a lift-off technique," in IEEE Journal of Solid-State

Circuits, vol. SC-11, no. 4, pp. 466-471, August 1976. ("Widmann). I understand that Widmann has been submitted as Exhibit 1023 in this proceeding.

- 14. As detailed below, I have reviewed the print reference, public holdings information, and Library of Congress MARC record for *Widmann* to determine the date of public availability for this reference.

- 15. **Appendix A** to this declaration is a true and accurate copy of the print journal cover (including volume binding), title page, table of contents, call number, and Library of Congress Date Stamp for the print issue of IEEE Journal of Solid-State Circuits containing *Widmann* held by the Library of Congress. The date stamp on this issue indicates that *Widmann* was received by the Library of Congress on September 17, 1976.

- 16. **Appendix B** to this declaration is a true and correct copy of the public catalog record for IEEE Journal of Solid-State Circuits containing *Widmann* held by the Library of Congress, which was downloaded from <a href="https://lccn.loc.gov/89657065">https://lccn.loc.gov/89657065</a> on August 31, 2023. The Library of Congress's public catalog record for its copy of IEEE Journal of Solid-State Circuits containing *Widmann* sets forth the publication history and item availability including holdings, call number, and onsite location information for members of the public seeking the print issue of IEEE Journal of Solid-State Circuits containing *Widmann*. The public catalog record (**Appendix B**) indicates that the

print issue of IEEE Journal of Solid-State Circuits containing *Widmann* should be requested in the Newspaper & Current Periodical Reading Room (Madison LM133) within holdings v.1:no.1-v.40:no.6 (1966:Sept.-2005:June) at Call Number TK7871.85 .I23.

- 17. **Appendix C** to this declaration is a true and accurate copy of the Library of Congress MARC record for its holdings of the serial publication IEEE Journal of Solid-State Circuits containing *Widmann*, which was downloaded from https://catalog.loc.gov/vwebv/staffView?searchId=22826&recPointer=0&recCount =25&bibId=11362790 on August 31, 2023.

- 18. The Library of Congress MARC record (**Appendix C**) for the serial publication IEEE Journal of Solid-State Circuits confirms the fixed data elements of MARC field tag 008 as 750901c19669999nyumrp0a0engc. As discussed above, the first six characters "750901" are in typical "**YYMMDD**" format and indicate that the serial publication IEEE Journal of Solid-State Circuits was initially catalogued by the Library of Congress on September 1, 1975. The publication status code "c1966" refers to "continuing resource currently published" indicating that the serial publication IEEE Journal of Solid-State Circuits began publication in 1966 and is a continuing resource currently published.

- 19. MARC record field tag 022 (**Appendix C**) denotes the unique International Standard Serial Number (ISSN) for IEEE Journal of Solid-State

Circuits as 0018-9200. MARC Field tag 260 sets forth the place of publication, publisher, and copyright date as: |a New York, N.Y.: |b Institute of Electrical and Electronics Engineers, |c ©1966-

- 20. Finally, MARC record field tags 991 set forth the local holdings, location, and call number information for the serial publication IEEE Journal of Solid-State Circuits containing *Widmann*. The MARC record (**Appendix C**) sets forth that the serial publication IEEE Journal of Solid-State Circuits containing *Widmann* is held in the Library of Congress General Collection or in the Newspaper & Current Periodical Reading Room (Madison LM133) at Call Number TK7871.85 .I23 beginning with the issue v 1-2:Sept-Dec \* 1966.

- 21. Based on the information in **Appendices A, B and C** it is clear that the issue of Solid-State Circuits containing *Widmann* was received by the Library of Congress on September 17, 1976. Based on standard library practices, *Widmann* would have been processed and catalogued by the Library of Congress within a matter of a few days or weeks of September 17, 1976.

- 22. Accordingly, *Widmann* would have been made available to the public within a few days or weeks of being checked-in and catalogued. The public could have accessed *Widmann* by searching the Library of Congress catalog, requesting the item from a library staff member, or by visiting the Newspaper & Current

Periodical Reading Room (Madison LM133) within a few weeks of September 17, 1976.

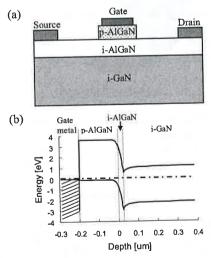

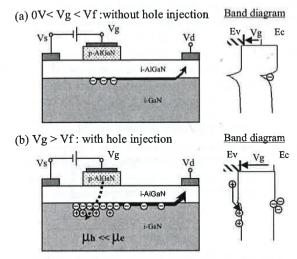

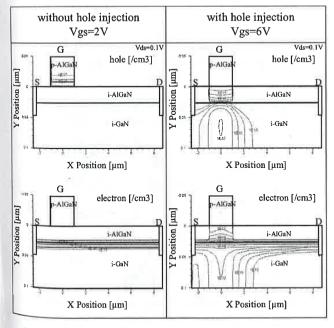

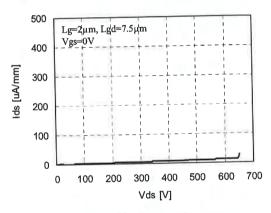

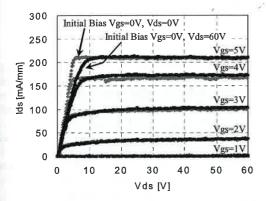

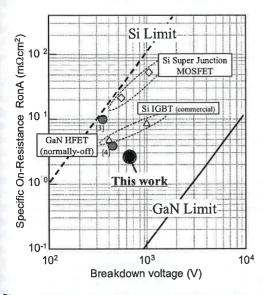

# VI. Public Availability of *Uemoto* (EX 1020)

- 23. Section six of this Declaration relates to the date of public availability for the following reference: Y. Uemoto et al., "A Normally-off AlGaN/GaN Transistor with RonA=2.6mΩcm2 and BVds=640V Using Conductivity Modulation," 2006 International Electron Devices Meeting, December 11-13, 2006, San Francisco, CA, Volume 2, pp. 654-657. ("Uemoto"). I understand that Uemoto has been submitted as Exhibit 1020 in this proceeding.

- 24. As detailed below, I have reviewed the print reference, public holdings information, and Library of Congress MARC record for *Uemoto* to determine the date of public availability for this reference.

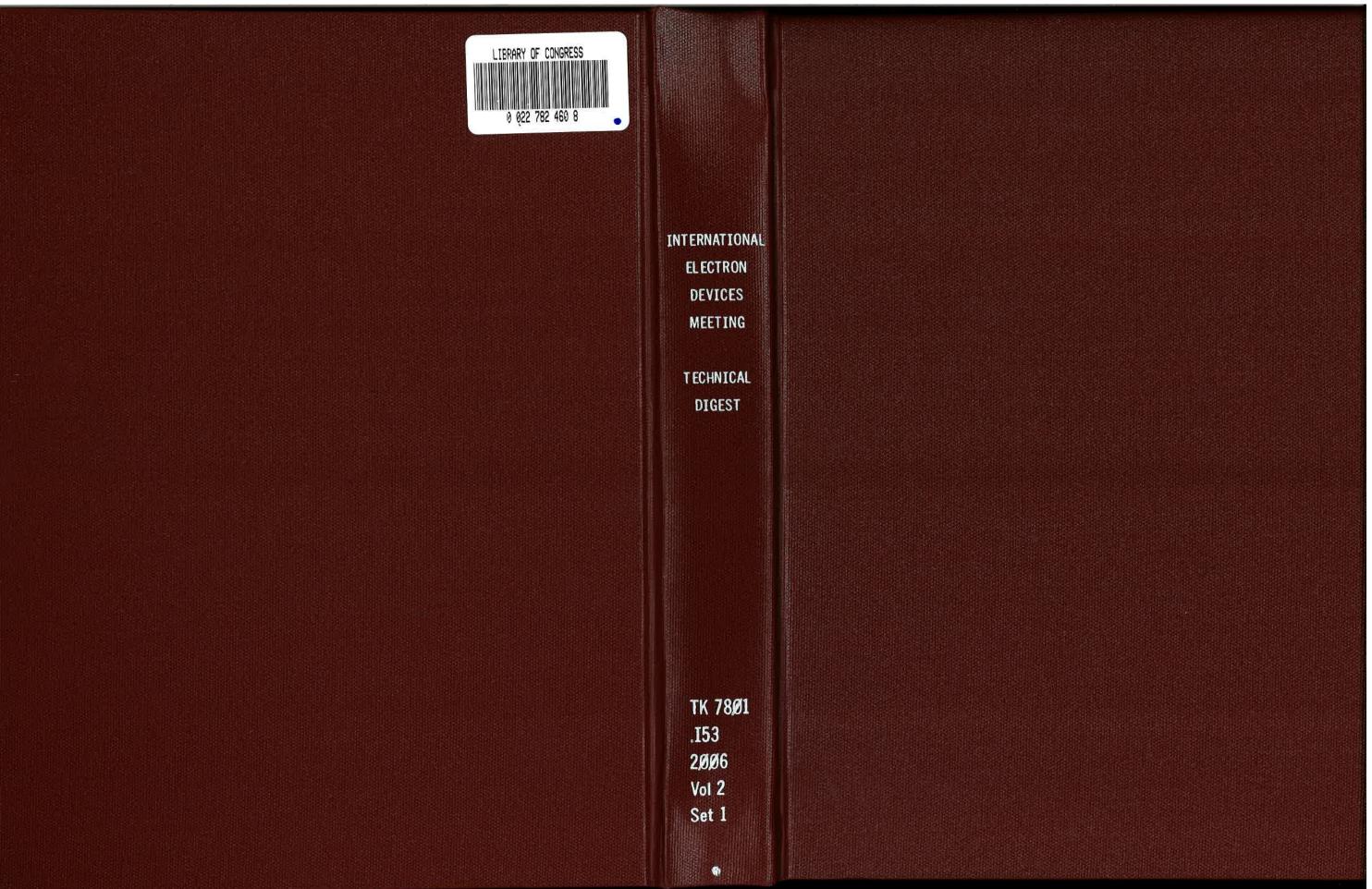

- 25. **Appendix D** to this declaration is a true and accurate copy of the print journal cover (including volume binding), title page, table of contents, call number, and barcode for the print volume of the 2006 International Electron Devices Meeting containing *Uemoto* received and held by the Library of Congress. The call number on the binding spine and title page indicates that *Uemoto* is publicly held at the Library of Congress at TK 7801 .153 2006 Vol. 2 Set 1.

- 26. **Appendix E** to this declaration is a true and correct copy of the public catalog record for the print volume of the 2006 International Electron

Devices Meeting containing *Uemoto* held by the Library of Congress, which was downloaded from https://lccn.loc.gov/81642284 on September 1, 2023. The Library of Congress's public catalog record for its copy of the 2006 International Electron Devices Meeting containing *Uemoto* sets forth the publication history, description, and item availability including holdings, call number, and onsite location information for members of the public seeking the print volume of the 2006 International Electron Devices Meeting containing *Uemoto*. The public catalog record (Appendix E) indicates that the Library of Congress maintains holdings for the International Electron Devices Meeting for 1973-1975, 1977-2000, 2002-2003, 2005-2006 (both 2006 volumes), 2009-2010 and 2012. The public catalog record (Appendix E) also shows that the print volume of the 2006 International Electron Devices Meeting containing *Uemoto* should be requested in the Jefferson or Adams Building Reading Rooms within holdings 2006, v. 2 at Call Number TK7801 .I53.

27. **Appendix F** to this declaration is a true and accurate copy of the Library of Congress MARC record for its holdings of the serial publication "International Electron Devices Meeting" containing *Uemoto*, which was downloaded from

https://catalog.loc.gov/vwebv/staffView?searchId=20290&recPointer=0&recCount=25&bibId=11248470 on September 1, 2023.

- 28. The Library of Congress MARC record (**Appendix F**) for the serial publication "International Electron Devices Meeting" confirms the fixed data elements of MARC field tag 008 as 780413c19739999nyuar1a0eng. As discussed above, the first six characters "780413" are in typical "**YYMMDD**" format and indicate that the serial publication "International Electron Devices Meeting" was firs catalogued by the Library of Congress on April 13, 1978. The publication status code "c1973" refers to "continuing resource currently published" showing that the serial publication "International Electron Devices Meeting" began publication in 1973 and is a continuing resource currently published.

- 29. MARC record field tag 022 (**Appendix F**) denotes the unique International Standard Serial Number (ISSN) for International Electron Devices Meeting as 0163-1918. MARC Field tag 260 sets forth the place of publication, publisher, and copyright date as: |**a** New York, N.Y.: |**b** Institute of Electrical and Electronics Engineers, |**c** 1973-

- 30. Finally, MARC record field tags 9XX set forth the holdings policies, location, and call number information for the serial publication "International Electron Devices Meeting" containing *Uemoto*. The MARC record (**Appendix F**) states that one copy of all issues received for International Electron Devices Meeting are to be kept permanently. **Appendix F** also sets forth the public holdings for "International Electron Devices Meeting" as held in the Library of

Congress General Collection in the Jefferson or Adams Building Reading Rooms at Call Number TK7801 .I53 beginning with receipts beginning in 1973.

- 31. Based on the information in **Appendices D, E and F** it is clear that the volume of "International Electron Devices Meeting" containing *Uemoto* would have been received by the Library of Congress during December 2006. Based on standard library practices, *Uemoto* would have been processed and catalogued by the Library of Congress within a matter of a few days or weeks of December 2006.

- 32. Accordingly, *Uemoto* would have been made available to the public within a few days or weeks of being checked-in and catalogued. The public could have accessed *Uemoto* by searching the Library of Congress catalog and/or requesting the item from a library staff member, or by visiting the Library of Congress Jefferson or Adams Building Reading Rooms during January 2007.

# VII. Conclusion

33. In signing this Declaration, I understand it will be filed as evidence in a contested case before the Patent Trial and Appeal Board of the United States Patent and Trademark Office. I understand I may be subject to cross-examination in this case and that cross-examination will take place within the United States. If cross-examination is required of me, I will appear for cross-examination within the United States during the time allotted for cross-examination.

34. I declare that all statements made herein of my knowledge are true, that all statements made on information and belief are believed to be true, and that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Executed on September 5, 2023.

Shauna L. Wiest

Shauna L. Wiest

# **APPENDIX A**

# (A).

# IEEE JOURNAL OF

# SOLID-STATE CIRCUITS

PUBLICATION OF THE IEEE SOLID-STATE CIRCUITS COUNCIL

# SPECIAL ISSUE ON TECHNOLOGY AND PROCESSING FOR INTEGRATED CIRCUITS

FOREWORD B. L. Gregory SPECIAL PAPERS R. S. Ronen, M. R. Splinter, High-Voltage SOS/MOS Devices and Circuit Elements: Design, and R. E. Tremain, Jr. Fabrication, and Performance Optimum Load Device for DMOS Integrated Circuits . . H. C. Lin, J. L. Halsor, and H. F. Benz 443 T. Masuhara and R. S. Muller Complementary DMOS Process for LSI .... 453 W. R. Dawes, G. F. Derbenwick, Process Technology for Radiation-Hardened CMOS Integrated Circuits and B. L. Gregory D. W. Widmann Metallization for Integrated Circuits Using a Lift-Off Technique...... I. Yoshida, M. Kubo, and S. Ochi A High Power MOSFET with a Vertical Drain Electrode and a Meshed Processing Technology and AC/DC Characteristics of Linear J. L. Saltich, W. L. George, Compatible PL and J. G. Soderberg 478 W. M. Gegg, J. L. Saltich, R. M. Roop, Ion-Implanted Super Gain Transistors and W. L. George J. Graul, A. Glasl, and H. Murrmann High-Performance Transistors with Arsenic-Implanted Polysil Emitters . K. C. Saraswat and J. D. Meindl A New Bipolar Process—Borsenic Laser Coding of Bipolar Read-Only Memories J. C. North and W. W. Weick 500 F. Barson Emitter-Collector Shorts in Bipolar Devices A Vertical Channel JFET Fabricated Using Silicon Planar Technology O. Ozawa, H. Iwasaki, and K. Muramoto REGULAR PAPERS R. A. Heald and D. A. Hodges Multilevel Random-Access Memory Using One-Transistor Per Cell J. R. Gaskill, Jr., J. H. Flint, Modular Single-Stage Universal Logic Gate R. G. Meyer, L. J. Michael and L. R. Weill J. R. Gaskill, Jr. J. H. Flint, LSI Multiplier Using High Speed ULG R. G. Meyer, L. J. Micheel, and L. R. Weill REGULAR CORRESPONDENCE P. E. Allen and W. J. Parrish High Frequency Response of Inverting Integrators 545 Antiblooming: A New Approach for Linear Imagers M. Mauthe and H.-J. Pfleiderer K. Nemeth On the Analysis of Nonlinear Resistive Networks Considering A Low-Pass Biquad Derived Filter Realization the Effect of Temperature . 550 J. H. Brodie Measurement of  $V_{CEIRE}$  of RF Power Transistors and of Waveform N. O. Sokal Details Near Voness Unifying the Concepts of Offset Voltage and Common-Mode R. C. Jaeger Rejection Ratio LIST OF UPCOMING SPECIAL ISSUES OF IEEE J-SC ...... Outside Back Cover

# Upcoming Special Issues of the IEEE Journal of Solid-State Circuits

The following are upcoming Special Issues of the IEEE JOURNAL OF SOLID-STATE CIR-CUITS. Prospective authors should contact the appropriate Guest Editor or the Editor of the JOURNAL for details. In general, the deadline for submission of manuscripts is six to seven months in advance of the publication date.

### October 1976

Semiconductor Memory and Logic B. T. Murphy, Guest Editor for Logic Bell Labs. 600 Mountain Ave. Murray Hill, NJ 07974

December 1976

Linear and Analog Circuits

G. L. Baldwin, Co-Guest Editor

Bell Labs.

Room 4D-625

Holmdel, NJ 07733

April 1977 Integrated Injection Logic (I<sup>2</sup>L/MTL) C. G. Thornton, Co-Guest Editor U.S. Army Electronics Command Fort Monmouth, NJ 07703 L. L. Vadasz, Guest Editor for Memory Intel Corp. 3065 Bowers Ave. Santa Clara, CA 95051

R. G. Meyer, Co-Guest Editor Elec. Eng. and Comput. Sci., Cory Hall Univ. of California Berkeley, CA 94720

N. C. de Troye, Co-Guest Editor Philips Res. Labs. Eindhoven, The Netherlands

# IEEE JOURNAL OF

# SEP 1 7 1976

# SOLID-STATE CIRCUITS

AUGUST 1976 VOLUME SC-11 NUMBER 4

A PUBLICATION OF THE IEEE SOLID-STATE CIRCUITS COUNCIL

#### SPECIAL ISSUE ON TECHNOLOGY AND PROCESSING FOR INTEGRATED CIRCUITS **FOREWORD** Special Issue on Technology and Processing for Integrated Circuits B. L. Gregory 430 SPECIAL PAPERS R. S. Ronen, M. R. Splinter, High-Voltage SOS/MOS Devices and Circuit Elements; Design, and R. E. Tremain, Jr. Fabrication, and Performance ..... 431 H. C. Lin, J. L. Halsor, and H. F. Benz Optimum Load Device for DMOS Integrated Circuits ..... T. Masuhara and R. S. Muller Complementary DMOS Process for LSI 453 W. R. Dawes, G. F. Derbenwick, Process Technology for Radiation-Hardened CMOS Integrated Circuits 459 and B. L. Gregory D. W. Widmann Metallization for Integrated Circuits Using a Lift-Off Technique..... 466 I. Yoshida, M. Kubo, and S. Ochi A High Power MOSFET with a Vertical Drain Electrode and a Meshed Gate Structure ..... 472 J. L. Saltich, W. L. George, Processing Technology and AC/DC Characteristics of Linear and J. G. Soderberg Compatible I<sup>2</sup>L 478 W. M. Gegg, J. L. Saltich, R. M. Roop, Ion-Implanted Super Gain Transistors ..... 485 and W. L. George J. Graul, A. Glasl, and H. Murrmann High-Performance Transistors with Arsenic-Implanted Polysil Emitters .... 491 K. C. Saraswat and J. D. Meindl A New Bipolar Process—Borsenic ..... J. C. North and W. W. Weick Laser Coding of Bipolar Read-Only Memories ..... 500 Emitter-Collector Shorts in Bipolar Devices ..... F. Barson 505 O. Ozawa, H. Iwasaki, and K. Muramoto A Vertical Channel JFET Fabricated Using Silicon Planar Technology ...... 511 **REGULAR PAPERS** R. A. Heald and D. A. Hodges Multilevel Random-Access Memory Using One-Transistor Per Cell 519 J. R. Gaskill, Jr., J. H. Flint, Modular Single-Stage Universal Logic Gate ..... 529 R. G. Meyer, L. J. Micheel, and L. R. Weill J. R. Gaskill, Jr., J. H. Flint, LSI Multiplier Using High Speed ULG R. G. Meyer, L. J. Micheel. and L. R. Weill REGULAR CORRESPONDENCE P. E. Allen and W. J. Parrish High Frequency Response of Inverting Integrators ..... 545 M. Mauthe and H.-J. Pfleiderer Antiblooming: A New Approach for Linear Imagers ..... K. Nemeth On the Analysis of Nonlinear Resistive Networks Considering 550 J. H. Brodie A Low-Pass Biquad Derived Filter Realization ..... 552 Measurement of $V_{CE(sat)}$ of RF Power Transistors and of Waveform N. O. Sokal Details Near $V_{CE(sat)}$ ..... 555 R. C. Jaeger Unifying the Concepts of Offset Voltage and Common-Mode Rejection Ratio 557 LIST OF UPCOMING SPECIAL ISSUES OF IEEE J-SC ......

# Metallization for Integrated Circuits Using a Lift-Off Technique

DIETRICH W. WIDMANN

Abstract—A special lift-off technique for realizing small metal interconnection geometries for integrated circuits is described. 0.6-\(\mu\mathrm{m}\) gaps between metal conductors can be obtained even at 0.8-\(\mu\mathrm{m}\) metal layer thickness. The slopes of the conductors are tapered. Etching problems inherent in alloy films or sandwiched layers such as Al/Si or Al/Cu/Si are avoided by the technique proposed. SEM micrographs of Al/Si conductor patterns are presented.

### INTRODUCTION

THE increasing packing density of integrated circuits requires small conductor linewidths and small spaces between conductors.

The interconnection pattern can be formed by conventional chemical etching techniques. However, chemical etching has several drawbacks. First, after delineation of alloy films such as Al/Si or Al/Si/Cu, silicon residues may remain in the field between the conductors [1]. Second, the cross section of the conductors may be considerably reduced by etchant penetration at steep oxide steps [1]. Third, due to the lateral etch attack, the widths of the conductors are reduced, and the spaces between adjacent conductors are increased (Fig. 1). The undercutting  $\Delta x$  per edge (see Fig. 1) might be in the order of the conductor thickness. As long as the desired spacing between adjacent conductors is large enough, i.e., larger than about 3 µm for 1-µm conductor thickness and 1-µm minimum photoresist dimension, the undercutting effect can be compensated by proper dimensioning the corresponding geometries on the photomask. However, if spaces of about 1 µm are required between 1-µm thick metal conductors, the compensation procedure fails.

The edge contours of conductors delineated by wet chemical etching are nearly conical [2], the upper portion of the edges being steep or even overhanging. Edge contours of this kind may lead to poor coverage of such edges by subsequently deposited layers such as passivation and metal layers.

Alternative methods which might be used instead of chemical etching are sputter or ion beam etching, plasma etching, selective plating, selective anodization, and lift-off techniques. This paper reports on results obtained with a lift-off technique, which is suitable for the metallization of integrated circuits with high packing density.

## LIFT-OFF TECHNIQUES

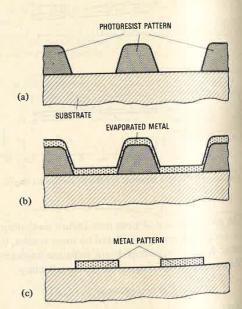

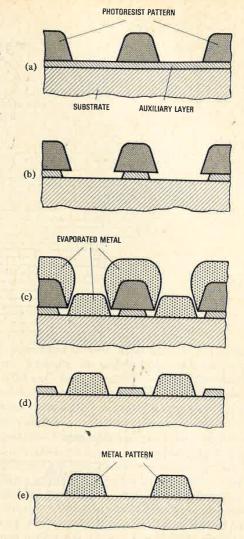

The lift-off technique for metal pattern formation is shown schematically in Fig. 2. This technique has been known for

Manuscript received February 17, 1976; revised April 16, 1976. This work was supported by the Technical Program of the Federal Department of Research and Technology of the Federal Republic of Germany. The author is with the Research Laboratories, Siemens AG, Munich,

Germany.

PHOTORESIST PATTERN

METAL

PATTERN

SUBSTRATE

Fig. 1. Schematic illustration of a typical cross section of metal conductors after chemical etching. The undercutting at the bottom of the conductors is  $\Delta x$ .

Fig. 2. Schematic illustration of metal pattern definition using the original lift-off technique. (a) Photoresist pattern definition. (b) Metal evaporation. (c) Photoresist stripping, thereby lifting off the overlying metal. The spaces between the metal features are equal to the corresponding photoresist linewidths, as measured at the bottom of the photoresist bars.

many years. For instance, it was used in 1966 by Steller [3] for the fabrication of chromium masks.

The process in Fig. 2 looks very simple. However, there are severe limitations concerning the thickness and the brittleness of the metal layer. The lifting mechanism works reliably only if the metal thickness at the bottom of the photoresist bars thin enough, i.e., some 100 Å, and if the metal is brittle so that it cracks readily at the photoresist edges [4]. For ductie

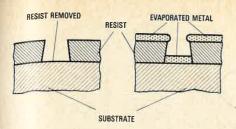

Metal patterning by a lift-off technique using slightly overhanging sidewalls of electron resist (after Hatzakis [7]).

metals, such as aluminum, the metal layer deposited on the photoresist should be completely separated from the other portions of the metal layer deposited on the substrate. This could be accomplished, for instance, by realizing vertical or slightly overhanging photoresist side walls, and by directing the evaporated metal atoms normal to the substrate surface [5]. The metal layer thickness should not exceed about 2/3 of the resist thickness [6], in order to assure complete separation of the two portions of the metal layer. Hatzakis [7] has demonstrated that properly exposed and developed electron resist layers exhibit overhanging edges suitable for lift-off patterning (Fig. 3). Yu et al. [8] used this technique for the fabfication of an 8 kbit memory of high density. Photoresist edges might also be realized with overhanging portions, for instance, due to interference effects during exposure of the photoresist [9] or due to poor adherence of the photoresist to the substrate. However, it is not very attractive to utilize these effects for lift-off metallization because they are difficult to reproduce.

The use of auxiliary layers is another possibility to realize werhanging edges. Hu [10] used an electrolytically plated copper pattern, and Grebe et al. [11] have proposed a lift-off process in which overhanging edges are realized by two photoresist layers and an auxiliary metal layer between the photoresist layers. We studied another approach which is described in the following sections. The principle of this technique is unilar to the process demonstrated by Browne and Perkins [12]. The technique uses the effect of an undercut auxiliary wer. There are no limitations concerning the shape of the sidewall contours of the resist, and metal atoms are allowed to impinge on the substrate surface at various angles of incidence, is the case for instance in vacuum systems with planetary totation of the substrates. Fine metal lines and spaces can be with tapered sidewalls of the conductors, even if the metal layer thickness is on the order of 1 μm, which is the curtally used thickness for integrated circuits.

# LIFT-OFF TECHNIQUE USING AN AUXILIARY LAYER

The lift-off process which we have studied is shown schematically in Fig. 4. First, a thin auxiliary layer is deposited on the substrate. With the aid of conventional photolithography regions which shall be free of metallization are masked photoresist [Fig. 4(a)]. The auxiliary layer is etched [Fig. 4(b)]. Due to undercutting the photoresist bars are overthe desired metallization layer is evaporated [Fig. 4(c)] by

Fig. 4. Schematic illustration of the investigated lift-off process using an auxiliary layer. (a) Deposition of a thin auxiliary layer followed by photoresist patterning. (b) Etching of the free portions of the auxiliary layer. (c) Metal evaporation. (d) Metal lift-off. (e) Removal of the auxiliary layer.

moving the substrates in the vacuum chamber such that the evaporated metal atoms are impinging on the substrate surface at varying angles. The metal regions deposited on the photoresist pattern are lifted off by dissolving the photoresist in a suitable stripper [Fig. 4(d)]. It is important to note that in the undercut regions the bottom of the photoresist bars is always completely free of metal coverage even if the metal atoms arrive at angles near 90°. The stripper can thus reach the photoresist after having penetrated the microcracks. Finally, the auxiliary layer must be removed selectively [Fig. 4(e)]. The resulting metallization pattern is inverse compared to the original photoresist pattern.

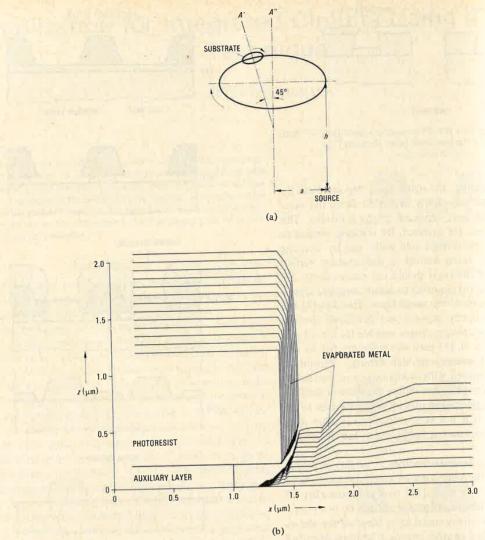

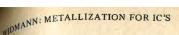

## EVAPORATION MODEL

As previously pointed out, the lift-off mechanism works reliably only as long as there is no continuity between the ma-

Fig. 5. Computer simulation of the metal layer buildup in the vicinity of undercut photoresist edges assuming no diffusion of the metal atoms after deposition. (a) Assumed geometry and substrate motion in the evaporation apparatus. The substrates are rotating around their own axis A' and simultaneously around the axis A". The number of rotations during the evaporation cycle is assumed to be large. For the angular characteristic of the evaporation rate of the source, a cosine law is assumed. (b) Calculated metal configuration in the center of the substrate with the following assumptions: Auxiliary layer thickness 0.2 μm; photoresist thickness 1.0 μm; vertical photoresist sidewall; undercutting under the photoresist edge 0.4 μm; evaporated metal film thickness 0.8 μm.

terial deposited on the substrate and that deposited on top of the photoresist. In order to study the film profiles at the photoresist edges during evaporation, the metal film growth was simulated using a step-by-step construction similar to that proposed by Blech et al. [13]. It is assumed that the metal atoms have zero diffusivity after deposition, an assumption which is approximately valid for substrate temperatures near room temperature.

Fig. 5(b) and (c) show the calculated metal film profiles for a distinct evaporation geometry given in Fig. 5(a). Due to the assumed planetary rotation of the substrates, the angular distribution of the incident atoms in the center of the substrates is symmetrical with respect to the substrate axis. The evap-

orated film profiles are thus the same for any orientation of the photoresist geometries. If the substrate diameter is small compared to the substrate-to-source distance, the same is approximately valid for the photoresist geometries at the peripherry of the substrate.

In Fig. 5(b) vertical photoresist sidewalls are assumed. The main result of the calculation is that a microcrack of about 200 Å in width remains between the two portions of the metal film, although the metal layer thickness is four times the auxiliary layer thickness. The maximum slope angle of the profile of the remaining metal pattern is about 70°. The position of the bottom edge of the metal film on the substrate is not exactly identical with the position of the photoresist edge.

Fig. 5 (continued). (c) Calculation for a 45° slope angle of the photoresist sidewall.

the maximum angle of incidence of the evaporated atoms is 45°, the bottom edge of the metal film is apart from the photoesist edge by an amount which corresponds to the thickness of the auxiliary layer. It should be noted that the calculation shown in Fig. 5(b) must be modified if the width of the conductor is comparable to or smaller than the thickness of the photoresist.

Fig. 5(c) shows the calculation for a photoresist sidewall exhibiting an angle of 45° with respect to the substrate surface. In this case the metal film on the substrate is separated from that deposited on top of the photoresist only if the metal layer thickness is smaller than about twice the auxiliary layer thickness. Our calculations have shown that the photoresist sidewalls should have slope angles of more than about 60° in order to realize complete separation of the two portions of the metal film if the thickness of the metal film is four times the auxiliary layer thickness.

### WAFER PREPARATION

The silicon wafers, 2 in in diameter, were prepared according the processing sequence of the conventional n-channel the processing sequence of the conventional n-channel stall-gate metal-oxide-semiconductor (MOS) technology. The thicknesses of the gate oxide and the field oxide are an and 0.6  $\mu$ m, respectively. The field oxide is covered a 0.1- $\mu$ m thick phosphorus silicate glass (PSG) layer. The phosphorus diffusion using a POCl<sub>3</sub> source, or by ion implication of arsenic.

the metal interconnection pattern was defined according to schematical illustration in Fig. 4. A 0.2-\mu thick chroman layer was evaporated as the auxiliary layer. The wafers coated with a 1-\mu thick Shipley AZ 1350 H photoresist drying was performed at 65°C for min followed by alignment and exposure in a contact printmachine. After development of the resist, the chromium

pattern was etched at room temperature in a cerium sulfate solution. Typically, the undercutting under the photoresist edges is 0.3 µm. After a dip etch in diluted hydrofluoric acid followed by rinsing in deionized water, a 0.8-µm thick aluminum layer containing 1.7 percent of silicon was evaporated on the wafers at room temperature using an electron beam gun as the evaporation source. During evaporation the wafers were rotated in a similar manner as that illustrated in Fig. 5(a). The only difference was that the wafer shown in Fig. 5(a) was replaced by a rotating plate loaded by five wafers. Three such rotating plates were mounted in the vacuum chamber. After metal deposition, the wafers were dipped in an ultrasonic bath containing a photoresist stripper. The remaining auxiliary chromium pattern was removed selectively by plasma etching in an oxygen ambient. Annealing was performed in forming gas at 450°-500°C for 30 min.

### EXPERIMENTAL RESULTS

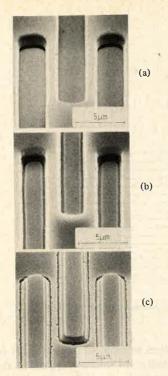

The SEM micrographs in Fig. 6 show three intermediate stages of the lift-off process. Fig. 6(a) corresponds to the stage illustrated schematically in Fig. 4(b), i.e., after etching of the chromium pattern. The overhang of the photoresist edges is clearly visible. The sidewalls of the photoresist pattern exhibit a slope angle of about 75° with respect to the wafer surface. This indicates that in this area of the wafer there was no intimate contact between mask and wafer during exposure of the photoresist. Fig. 6(b) shows the same detail after metal evaporation, and Fig. 6(c) after the lift-off process, corresponding to Fig. 4(c) and (d), respectively. A small gap of about 0.1 µm is left between the auxiliary metal pattern and the desired Al/Si pattern. The spaces between adjacent Al/Si bars are 0.85 µm, i.e., 0.4 µm smaller than the corresponding photoresist stripes in Fig. 6(a) which are 1.25-µm wide, in accordance with the estimation in the previous section. The average slope angle of the Al/Si sidewalls is about 50°.

Fig. 6. SEM micrographs showing the same detail after three intermediate stages of the lift-off process. (a) After etching of the chromium pattern. (b) After evaporation of Al + 1.7 percent Si. (c) After the lift-off process. In the spaces between the Al/Si stripes the auxiliary chromium pattern is visible. Thicknesses: 0.2 μm Cr, 1.0 μm AZ 1350 H photoresist, 0.8 μm Al/Si.

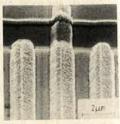

Fig. 7. SEM micrograph of a small area of a wafer surface after incomplete lift-off. A portion of the metal deposited on top of the photoresist is left on the sample while the photoresist is already removed. The discontinuities in the metal film at the bottom points of the metal bridge are clearly visible.

The smooth edge contour of the Al/Si bars confirms that no continuity had existed between the remaining metal pattern and the metal film deposited on top of the photoresist. With the SEM micrograph of Fig. 7 we have tried to make the microcrack at the photoresist edges visible. The lift-off process was performed such that lift-off was incomplete so that portions of the metal deposited on top of the photoresist were remaining on the sample while the photoresist was already dissolved.

Figs. 8-10 are SEM micrographs showing details of charge-

Fig. 8. SEM micrograph showing some of the electrodes of a linear CCD sensor. The average width of the gaps between the electrodes is  $1 \mu m$ . The thickness of the Al/Si electrodes is  $0.8 \mu m$ .

Fig. 9. SEM micrograph showing some of the electrodes of a two-dimensional CCD sensor. The gaps between the electrodes are 0.6-μm wide. The thickness of the Al/Si electrodes which are running over 0.5-μm high oxide steps is 0.8 μm.

Fig. 10. SEM micrograph showing three electrodes of a linear CCD sensor. The widths of the electrodes and the spaces between the electrodes are 1.7  $\mu$ m and 0.8  $\mu$ m, respectively. The electrode in the center of the picture is running over a PSG step which is too steep so that the step coverage is poor. The thickness of the Al/Si electrodes is 0.8  $\mu$ m.

coupled devices (CCD's) whose Al/Si electrodes and interconnections were formed by the lift-off technique described. CCD sensors organized by the frame transfer principle with a total electrode length of 1.35 meters and an electrode spacing of 1.2 µm could be fabricated without defects in the metallization. It should be noted that the contours of the Al/Si sidewalls pointing to the right side of the micrographs in Figs. 8-10 are not symmetrical to those pointing to the left side. This is due to the fact that the rotation of the wafers during evaporation was not an ideal planetary rotation.

For semiconductor devices, it is very important that the metprocess has no detrimental effect on the electrical characteristics of the devices. We have performed capacitancemeasurements of MOS structures before and after a temperature treatment (10 min at 200°C and 2 · 106 V · The density of surface states and mobile charges can be kept below 5 · 10<sup>10</sup> cm<sup>-2</sup>.

### CONCLUSIONS

the lift-off technique described is compatible with MOS technology. Spaces of 1-µm width and even smaller between metal conductors can be fabricated with a metal film thickness of about 1 µm. The sidewalls of the conductors are smoother han those fabricated by conventional etching. Tapering of the sidewalls is achieved by evaporating the metal film such that the metal atoms are directed on the substrates at various ngles of incidence. Co-evaporation from different sources as as subsequent evaporation of different materials is posble without the need for etching the resulting multicomnament layers. The slope angle of the photoresist sidewalls is got very critical. We have successfully used contact printing and projection printing for photoresist exposure. Due to the nonnormal incidence of the metal atoms during evaporation. the linewidths of the conductors, as measured at the bottom of the conductors, are larger than the widths of the corremondent spaces of the photoresist pattern. The linewidth difmence is about double the auxiliary layer thickness, i.e., mout 0.4 µm. This effect is opposite to the undercutting efket inherent in chemical etching which tends to reduce the conductor linewidths.

Iwo important drawbacks of the lift-off technique described must be mentioned. Compared to conventional etching more process steps are required and the substrate temperature must kept below about 100°C during evaporation. This means hat the steps over which the conductors are running must not too steep in order to obtain sufficient step coverage [13]. Also, adhesion of the metal film and electromigration resistime [14] may be reduced compared to metal films evap-Mated on substrates kept at 200°-400°C during evaporation.

### ACKNOWLEDGMENT

The author wishes to thank all the co-workers in the laboramy for their contribution to this work, and Dr. K.-U. Stein d Dr. M. Zerbst for stimulating the work.

### REFERENCES

A. J. Learn, "Aluminum alloy film deposition and characterization," Thin Solid Films, vol. 20, pp. 261-279, Feb. 1974.

- [2] J. L. Vossen, G. L. Schnable, and W. Kern, "Processes for multilevel metallization," J. Vac. Sci. Technol., vol. 11, pp. 60-70, Jan.-Feb. 1974.

- [3] M. K. J. Stelter, "Chrome masks-The ideal master for photoprocessing," SPC and Solid-State Technol., vol. 9, pp. 60-63, 1966.

- [4] S. Middelhoek, "Metallization processes in fabrication of Schottky-barrier FET's," IBM J. Res. Develop., vol. 14, pp. 117-124, Mar.

- [5] H. I. Smith, F. J. Bachner, and N. Efremow, "A high yield photolithographic technique for surface wave devices," J. Electrochem.

- Soc., vol. 118, pp. 821-825, May 1971.

[6] H. I. Smith, "Fabrication techniques for surface-acoustic-wave and thin-film optical devices," Proc. IEEE, vol. 62, pp. 1361-1387, Oct. 1974.

- [7] M. Hatzakis, "Electron resists for microcircuits and mask produc-

- [8] H. N. Yu, R. H. Dennard, T. H. P. Chang, C. M. Osburn, V. Dilonardo, and H. E. Luhn, "Fabrication of a miniature 8K-bit memory chip using electron-beam exposure," J. Vac. Sci. Technol., vol. 12, pp. 1297-1300, Nov.-Dec. 1975.

- [9] F. H. Dill, A. R. Neureuther, J. A. Tuttle, and E. J. Walker, "Modeling projection printing of positive photoresists," IEEE Trans. Electron Devices (Special Issue on Pattern Generation and Microlithography), vol. ED-22, pp. 456-464, July 1975.

- [10] K. C. Hu, "A new technique of patterning evaporated metallic films," in Proc. Nat. Electron. Packaging and Production Conf., Jan.-Feb. 1967, pp. 541-548.

- [11] K. Grebe, I. Ames, and A. Ginzberg, "Masking of deposited thin films by means of an aluminum-photoresist composite," J. Vac. Sci. Technol., vol. 11, pp. 458-460, 1974.

- [12] V. A. Browne and K. D. Perkins, "A nonoverlapping gate chargecoupling technology for serial memory and signal processing applications," IEEE J. Solid-State Circuits (Special Issue on Charge-Transfer Devices), vol. SC-11, pp. 203-207, Feb. 1976.

- [13] I. A. Blech, J. F. Campbell, and W. H. Shepherd, "Discontinuities in evaporated aluminum interconnections," in Proc. 8th Reliability Symp., Las Vegas, NV, 1970, pp. 144-157.

- [14] A. J. Learn, "Electromigration effects in aluminum alloy metallization," J. Electron. Materials, vol. 3, pp. 531-552, 1974.

Dietrich W. Widmann received the Dipl. Phys. and Dr. Ing. degrees from the Technical University of Stuttgart, Stuttgart, Germany, in 1962 and 1965, respectively.

In 1965 he joined the Siemens AG, Munich, Germany, where he has been engaged in development of bipolar integrated circuit technology. Since 1971 he has been working on the technology of LSI MOS integrated circuits. His research activities are in the areas of photolithography, metallization, and passivation for

integrated circuits with micron and submicron features. Dr. Widmann is a member of the German Physical Society.

# **APPENDIX B**

# 1. IEEE journal of solid-state circuits.

**LCCN** 89657065

Type of material Periodical or Newspaper

Main title IEEE journal of solid-state circuits.

Published/Created New York, N.Y.: Institute of Electronics Engineers, ©1966-

Publication historyVol. SC-1, no. 1 (Sept. 1966)-Descriptionvolumes : illustrations ; 28 cm

Current frequencyMonthly, 1991-Former frequencyQuarterly, 1966-

Bimonthly, <1986->

ISSN

0018-9200

Linking ISSN

0018-9200

LC classification

TK7871.85 .123

Variant title Institute of Electrical and Electronics Engineers journal of solid state circuits

Portion of title Journal of solid-state circuits

Serial key title IEEE journal of solid-state circuits

Abbreviated title IEEE j. solid-state circuits

Related names IEEE Solid-State Circuits Council, issuing body.

IEEE Solid-State Circuits Society, issuing body.

**LC Subjects** Semiconductors--Periodicals.

Integrated circuits--Periodicals.

Solid state electronics--Periodicals.

Other Subjects Integrated circuits.

Semiconductors.

Solid state electronics.

Form/Genre Periodicals.

Periodicals.

Notes Issued by the IEEE Solid-State Circuits Council; by: IEEE Solid-State Circuits Society, 1997-

Indexed selectively by Chemical abstracts 0009-2258 1966-1982

Additional formats Also issued on CD-ROM.

Online version: IEEE journal of solid-state circuits 1558-173X (DLC) 2005214279

(OCoLC)44608277

CODEN IJSCBC

Postal reg no. 925080 USPS

Other system no. (OCoLC)ocm01589745

Invalid LCCN sn 78000342

Additional Links http://ieeexplore.ieee.org/servlet/opac?punumber=4

Content type text

Media type unmediated Carrier type volume

Source of description Latest issue consulted: Vol. 51, no. 12 (Dec. 2016) (surrogate).

**CALL NUMBER** TK7871.85 .123

Set 1

Request in Jefferson or Adams Building Reading Rooms

Older receipts v.1:no.1-v.40:no.6 (1966:Sept.-2005:June), v.40:no.9-v.43:no.3 (2005:Sept.-2008:Mar.),

v.43:no.6-v.44:no.5 (2008:June-2009:May), v.44:no.7-v.56:no.12 (2009:July-2021:Dec.) v.1:no.1-v.40:no.6 (1966:Sept.-2005:June), v.40:no.9-v.43:no.3 (2005:Sept.-2008:Mar.), v.43:no.6-v.44:no.5 (2008:June-2009:May), v.44:no.7-v.56:no.12 (2009:July-2021:Dec.)

CALL NUMBER TK7871.85 .123

Copy 1

Unbound issues

Request in Newspaper & Current Periodical Reading Room (Madison LM133)

Latest receipts v. 58, no. 8 (2023 Aug.)

v. 58, no. 7 (2023 July) v. 58, no. 6 (2023 June) v. 58, no. 5 (2023 May) v. 58, no. 4 (2023 Apr.) v. 58, no. 3 (2023 Mar.)

v. 58, no. 2 (2023 Feb.) v. 58, no. 1 (2023 Jan.) v. 57, no. 12 (2022 Dec.)

v. 57, no. 11 (2022 Nov.) v. 57, no. 10 (2022 Oct.) v. 57, no. 9 (2022 Sept.) v. 57, no. 8 (2022 Aug.) v. 57, no. 7 (2022 July) v. 57, no. 6 (2022 June)

v. 57, no. 5 (2022 May) v. 57, no. 4 (2022 Apr.) v. 57, no. 3 (2022 Mar.)

v. 57, no. 2 (2022 Feb.) v. 57, no. 1 (2022 Jan.) v. 44, no. 6 (2009 June)

LC CATALOG Library of Congress 101 Independence Ave., SE Washington, DC 20540

Questions? Ask a Librarian:

https://ask.loc.gov/

# **APPENDIX C**

# LIBRARY CATALOG

Search Navigation ▼

1 of 3

PERIODICAL OR NEWSPAPER

# IEEE journal of solid-state circuits

| Full Record | MARC Tags                                                                                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                                                                                                                                                                                                                                                         |

| 000         | 05020cas a2200973 a 4500                                                                                                                                                                                                                                                |

| 001         | 11362790                                                                                                                                                                                                                                                                |

| 005         | 20211217065645.0                                                                                                                                                                                                                                                        |

| 800         | 750901c19669999nyumr p 0 a0eng c                                                                                                                                                                                                                                        |

| 010         | <b>a</b> 89657065   <b>z</b> sn 78000342                                                                                                                                                                                                                                |

| 022         | <b>a</b> 0018-9200   <b>I</b> 0018-9200   <b>2</b> 1                                                                                                                                                                                                                    |

| 030         | a IJSCBC                                                                                                                                                                                                                                                                |

| 032         | <b>a</b> 925080   <b>b</b> USPS                                                                                                                                                                                                                                         |

| 035         | <b>a</b> (OCoLC)ocm01589745                                                                                                                                                                                                                                             |

| 040         | a MUL  b eng  c MUL  d NSD  d YUS  d HUL  d SER  d NSD  d OCL  d AIP  d NST  d NSD   d DLC  d NST  d DLC  d NST  d IUL  d WAU  d MYG  d CUS  d MYG  d OCL  d SYS  d IEEE X  d OCLCQ  d NSD  d LVB  d CIT  d OCLCQ  d OCLCF  d CUS  d IUL  d UMC  d OCLCQ   d UMC  d CGU |

| 042         | a nsdp  a pcc                                                                                                                                                                                                                                                           |

| 050         | 00   <b>a</b> TK7871.85   <b>b</b> .123                                                                                                                                                                                                                                 |

| 210         | 0_  a  EEE j. solid-state circuits                                                                                                                                                                                                                                      |

| 222         | _0  a  EEE journal of solid-state circuits                                                                                                                                                                                                                              |

| 245         | 00  a  EEE journal of solid-state circuits.                                                                                                                                                                                                                             |

| 246         | 3_  a Institute of Electrical and Electronics Engineers journal of solid state circuits                                                                                                                                                                                 |

| 246         | 30  a Journal of solid-state circuits                                                                                                                                                                                                                                   |

| 260         | a New York, N.Y. :  b Institute of Electrical and Electronics Engineers,  c ©1966-                                                                                                                                                                                      |

| 300         | <b>a</b> volumes :   <b>b</b> illustrations ;   <b>c</b> 28 cm                                                                                                                                                                                                          |

| 310         | <b>a</b> Monthly,   <b>b</b> 1991-                                                                                                                                                                                                                                      |

| 321         | <b>a</b> Quarterly,   <b>b</b> 1966-                                                                                                                                                                                                                                    |

| IVI | Lo catalog item memation (with a lage)                                                                                            |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|

|     | <b>a</b> Bimonthly,   <b>b</b> <1986->                                                                                            |

| _   | a text  b txt  2 rdacontent                                                                                                       |

| _   | a unmediated  b n  2 rdamedia                                                                                                     |

| _   | a volume  b nc  2 rdacarrier                                                                                                      |

| 0_  | a Vol. SC-1, no. 1 (Sept. 1966)-                                                                                                  |

| 2_  | <b>a</b> Chemical abstracts   <b>x</b> 0009-2258   <b>b</b> 1966-1982                                                             |

|     | a Also issued on CD-ROM.                                                                                                          |

| _   | a Issued by the IEEE Solid-State Circuits Council; by: IEEE Solid-State Circuits Society, 1997-                                   |

|     | a Latest issue consulted: Vol. 51, no. 12 (Dec. 2016) (surrogate).                                                                |

|     | a SERBIB/SERLOC merged record                                                                                                     |

| _0  | a Semiconductors  v Periodicals.                                                                                                  |

| _0  | a Integrated circuits  v Periodicals.                                                                                             |

| _0  | a Solid state electronics  v Periodicals.                                                                                         |

| _6  | <b>a</b> Électronique de l'état solide   <b>v</b> Périodiques.                                                                    |

| _6  | a Circuits électroniques  v Périodiques.                                                                                          |

| _7  | a Integrated circuits.  2 fast  0 (OCoLC)fst00975535                                                                              |

| _7  | a Semiconductors.  2 fast  0 (OCoLC)fst01112198                                                                                   |

| _7  | a Solid state electronics.  2 fast  0 (OCoLC)fst01125449                                                                          |

| _7  | <b>a</b> Periodicals.   <b>2</b> fast   <b>0</b> (OCoLC)fst01411641                                                               |

| _7  | a Periodicals.  2 lcgft                                                                                                           |

| 2_  | a IEEE Solid-State Circuits Council,  e issuing body.                                                                             |

| 2_  | a IEEE Solid-State Circuits Society,  e issuing body.                                                                             |

| 80  | i Online version:  t   IEEE   journal   of solid-state   circuits   x 1558-173X   w (DLC)   2005214279   w (OCoLC) 44608277       |

| 41  | u http://ieeexplore.ieee.org/servlet/opac?punumber=4                                                                              |

| 33  | <b>8</b> 1   <b>a</b> v.   <b>b</b> no.   <b>u</b> 6   <b>v</b> r   <b>i</b> (year)   <b>j</b> (month)   <b>w</b> b   <b>x</b> 02 |

| 40  | <b>8</b> 1   <b>a</b> <5>-   <b>i</b> <1970>-   <b>x</b> provisional                                                              |

|     | a IEEE journal of solid-state circuits.  i 89-657065                                                                              |

| _   | a 7  b cbc  c serials  d 3  e ncip  f 19  g n-oclcserc                                                                            |

|     | a Keep 1                                                                                                                          |

|     | d 20020725  s Group Registration                                                                                                  |

|     | a srvf                                                                                                                            |

|     | <b>e</b> eserial 200406                                                                                                           |

|     | <b>b</b> c-GenColl   <b>h</b> TK7871.85   <b>i</b> .I23   <b>w</b> SERIALS                                                        |

| _   | b c-GenColl  h TK7871.85  i .123  p 00050772172  t Copy 1  v 1-2:Sept-Dec * 1966  w CCF                                           |

|     | b c-GenColl  h TK7871.85  i .123  p 00032911122  t Copy 1  v 28:1993 * 1993  w CCF                                                |

|     | b c-GenColl  h TK7871.85  i .123  p 00032910786  t Copy 1  v 29:1994 * 1994  w CCF                                                |

|     | 2_<br><br>-0<br>-0<br>-0<br>-6<br>-6<br>-7<br>-7<br>-7<br>-7<br>-7<br>-7<br>2_<br>08<br>41<br>33                                  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00039961751  t Copy 1  v 30 * 1995  w CCF                                                                |  |  |  |

|----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 991      |                            | <b>b</b> c-GenColl   <b>h</b> TK7871.85   <b>i</b> .l23   <b>p</b> 00057703611   <b>t</b> Copy 1   <b>v</b> 31 May-Aug * 1996   <b>w</b> CCF |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .l23  p 00057703933  t Copy 1  v 31 Sept-Dec * 1996  w CCF                                                       |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00057703982  t Copy 1  v 31 1996 * 1996  w CCF                                                           |  |  |  |

| 991      |                            | <b>b</b> c-GenColl   <b>h</b> TK7871.85   <b>i</b> .l23   <b>p</b> 00058114704   <b>t</b> Copy 1   <b>v</b> 32 * 1997 Jan-Jun   <b>w</b> CCF |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i . 23  p 00058114674  t Copy 1  v 32 * 1997 Jul-Dec  w CCF                                                        |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00023487901  t Copy 1  v 4-5 1969-70 * 8888  w CCF                                                       |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00023488243  t Copy 1  v 10 * 1975  w CCF                                                                |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027986900  t Copy 1  v 13 1978 * 8888  w CCF                                                           |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027986894  t Copy 1  v 15 1980 * 8888  w CCF                                                           |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00001496475  t Copy 1  v 17:1-5 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00001496451  t Copy 1  v 18:1-6 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027962932  t Copy 1  v 20:1-6 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027962920  t Copy 1  v 21:1-6 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027962919  t Copy 1  v 22:1-6 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00001496463  t Copy 1  v 23:1-5 * 1988  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027948844  t Copy 1  v 24:1-6 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027948832  t Copy 1  v 25:1-3 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027948820  t Copy 1  v 25:4-6 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027948819  t Copy 1  v 26:1-6 * 1991  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 0000149644A  t Copy 1  v 27:1-6 * 8888  w CCF                                                            |  |  |  |

| 991      |                            | b c-GenColl  h TK7871.85  i .123  p 00027948996  t Copy 1  v 27:7-12 * 8888  w CCF                                                           |  |  |  |

| 992      |                            | b SER  w SERLOC                                                                                                                              |  |  |  |

|          |                            |                                                                                                                                              |  |  |  |

| Requ     | quest this Item LC Find It |                                                                                                                                              |  |  |  |

| <u> </u> |                            |                                                                                                                                              |  |  |  |

Item Availability >

CALL NUMBER TK7871.85 .I23

Set 1

Request in Jefferson or Adams Building Reading Rooms

Status Not Charged

Older receipts v.1:no.1-v.40:no.6 (1966:Sept.-2005:June), v.40:no.9-v.43:no.3

(2005:Sept.-2008:Mar.), v.43:no.6-v.44:no.5 (2008:June-2009:May),

v.44:no.7-v.56:no.12 (2009:July-2021:Dec.)

| CALL NUMBER     | TK7871.85 .I23                                              |

|-----------------|-------------------------------------------------------------|

|                 | Copy 1                                                      |

|                 | Unbound issues                                              |

| Request in      | Newspaper & Current Periodical Reading Room (Madison LM133) |

| Status          | Not Charged                                                 |

| Latest receipts | v. 58, no. 8 (2023 Aug.)                                    |

|                 | v. 58, no. 7 (2023 July)                                    |

|                 | v. 58, no. 6 (2023 June)                                    |

|                 | v. 58, no. 5 (2023 May)                                     |

|                 | v. 58, no. 4 (2023 Apr.)                                    |

|                 | v. 58, no. 3 (2023 Mar.)                                    |

|                 | v. 58, no. 2 (2023 Feb.)                                    |

|                 | v. 58, no. 1 (2023 Jan.)                                    |

|                 | v. 57, no. 12 (2022 Dec.)                                   |

|                 | v. 57, no. 11 (2022 Nov.)                                   |

|                 | v. 57, no. 10 (2022 Oct.)                                   |

|                 | v. 57, no. 9 (2022 Sept.)                                   |

|                 | v. 57, no. 8 (2022 Aug.)                                    |

|                 | v. 57, no. 7 (2022 July)                                    |

|                 | v. 57, no. 6 (2022 June)                                    |

|                 | v. 57, no. 5 (2022 May)                                     |

|                 | v. 57, no. 4 (2022 Apr.)                                    |

|                 | v. 57, no. 3 (2022 Mar.)                                    |

|                 | v. 57, no. 2 (2022 Feb.)                                    |

|                 | v. 57, no. 1 (2022 Jan.)                                    |

|                 | v. 44, no. 6 (2009 June)                                    |

# **APPENDIX D**

LC COPYRIGHT

0 022 782 460 8

Page 36 of 65

TK 7801 . 153

## **6 International Electron** vevices Meeting

San Franciso, CA December 11-13, 2006

Volume 2 of 2

**IEEE Catalog Number:**

**ISBN**

06CH37807 1-4244-0438-X

# 2006 International Electron Devices Meeting.

Technical digest.

San Francisco, CA December 11-13, 2006

Volume 2 of 2

**IEEE Catalog Number:**

ISBN:

06CH37807 1-4244-0438-X

#### Copyright © 2006 by The Institute of Electrical and Electronics Engineers, Inc. All Rights Reserved

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923.

For other copying, reprint or republications permission, write to IEEE Copyrights Manager, IEEE Operations Center, 445 Hoes Lane, Piscataway, New Jersey USA 08854. All rights reserved.

IEEE Catalog Number:

06CH37807

ISBN:

1-4244-0438-X

Library of Congress:

81-642284

#### Additional Copies of This Publication Are Available from:

**IEEE Service Center** 445 Hoes Lane Piscataway, NJ 08854 **IEEE Service Center** 445 Hoes Lane

Piscataway, NJ 08854

(800) 678-IEEE (732) 981-1393

Fax:

Phone:

(732) 981-9667

E-mail:

customer-service@ieee.org

| Universal Relationship between Low-Field Mobility and High-Field Carrier Velocity in High-k and SiO2  Gate Dielectric MOSFETs.                                                                                                                       | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Masumi Saitoh, Ken Uchida                                                                                                                                                                                                                            |     |

| High Performing pMOSFETs on Si(110) for Application to Hybrid Orientation                                                                                                                                                                            |     |

| Technologies - Comparison of HfO2 and HfSiON                                                                                                                                                                                                         | 5   |

| Siddarth A. Krishnan , H. Rusty Harris, Paul D. Kirsch, Cristiano Krug, Manuel Quevedo-Lopez, Chadwin Young, Byoung Hun Lee, Rino Choi, Naser Chowdhury, Sagar Suthram, Scott Thompson, Gennadi Bersuker, Rajarao Jammy                              |     |

| Ni-based FUSI gates: CMOS Integration for 45nm node and beyond                                                                                                                                                                                       |     |

| Practical Vth Control Methods for Ni-FUSI/HfSiON MOSFETs on SOI Substrates<br>Koichi Terashima, Kenzo Manabe, Kensuke Takahashi, Koji Watanabe, Takashi Ogura,<br>Motofumi Saitoh, Makiko Oshida, Nobuyuki Ikarashi, Toru Tatsumi, Hirohito Watanabe | 13  |

| Effect of Fluorine Incorporation on 1/f Noise of HfSiON FETs for Future Mixed-Signal CMOS                                                                                                                                                            | 17  |

| Suppression of Poly-Gate-Induced Fluctuations in Carrier Profiles of Sub-50nm MOSFETs                                                                                                                                                                | 21  |

| A large-area flexible wireless power transmission sheet using printed plastic MEMS switches and organic field-effect transistors                                                                                                                     | 25  |

| Tsuyoshi Sekitani, Makoto Takamiya, Yoshiaki Noguchi, Shintaro Nakano, Yusaku Kato, Kazuki Hizu, Hiroshi<br>Kawaguchi, Takayasu Sakurai, Takao Someya                                                                                                |     |

| Self-aligned printing of high-performance polymer thin-film transistors                                                                                                                                                                              | 29  |

| How to Achieve High Mobility Thin Film Transistors by Direct Deposition of Silicon Using 13.56 MHz RF PECVD?                                                                                                                                         | 33  |

| CH. Lee, A. Sazonov, J. Robertson, A. Nathan, M.R. Esmaeili-Rad, P. Servati, W.I. Milne                                                                                                                                                              |     |

| Promising a-Si:H TFTs with High Mechanical Reliability for Flexible Display                                                                                                                                                                          | 37  |

| High Stability, Low Leakage Nanocrystalline Silicon Bottom Gate Thin Film Transistors for AMOLED Displays                                                                                                                                            | .41 |

| Mohammad R. Esmaeili-Rad, Andrei Sazonov, Arokia Nathan                                                                                                                                                                                              |     |

| Highly Stable Ga2O3-In2O3-ZnO TFT for Active-Matrix Organic Light-Emitting Diode Display                                                                                                                                                             | 15  |

| Application                                                                                                                                                                                                                                          | 43  |

| Stacked low-power field-programmable antifuse memories for RFID on plastic                                                                                                                                                                           | 49  |

| An Accurate Lifetime Analysis Methodology Incorporating Governing NBTI Mechanisms in High-k/SiO2                                                                                                                                                     | £2  |

| Gate Stacks                                                                                                                                                                                                                                          | 33  |

| Fundamental understanding and optimization of PBTI in nFETs with SiO2/HfO2 gate stack  E. Cartier, B. P. Linder, V. Narayanan, V. K. Paruchuri                                                                                                       | 57  |

| New Observations on the Uniaxial and Biaxial Strain-Induced Hot Carrier and NBTI Reliabilities for 65nm Node CMOS Devices and Beyond                                                            | 61           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Steve S. Chung, D. C. Huang, Y. J. Tsai, C. S. Lai, C. H. Tsai, P. W. Liu, Y. H. Lin, C. T. Tsai, G. H. Ma, S. C. Chien, S. W. Sun                                                              |              |

| Gate Leakage vs. NBTI in Plasma Nitrided Oxides: Characterization, Physical Principles, and Optimization                                                                                        | 65           |

| A.E. Islam, G. Gupta, S. Mahapatra, A.T. Krishnan, K. Ahmed, F. Nouri, A. Oates, M.A. Alam                                                                                                      |              |

| Characterization and Physical Origin of Fast Vth Transient in NBTI of pMOSFETs with SiON Dielectric                                                                                             | 69           |

| AC NBTI studied in the 1 Hz – 2 GHz range on dedicated on-chip CMOS circuits                                                                                                                    | 73           |

| SRAM Cell Static Noise Margin and VMIN Sensitivity to Transistor Degradation                                                                                                                    | . <b></b> 77 |

| Prediction and Control of NBTI - Induced SRAM Vccmin Drift                                                                                                                                      | 81           |

| J.C. Lin, A.S. Oates, H.C. Tseng, Y.P. Liao, T.H. Chung, K.C. Huang, P. Y. Tong, S.H. Yau, Y.F. Wang                                                                                            |              |

| Plasma Co-polymerization Technology with Molecular-level Structure Tightening in filn-situfl SiOCH                                                                                              | 0.           |

| Stacks for 32nm-node Cu Interconnects                                                                                                                                                           | 85           |