**Case No:** IPR2023-01382

**Patent No.** 9,748,347

Case No: IPR2023-01384

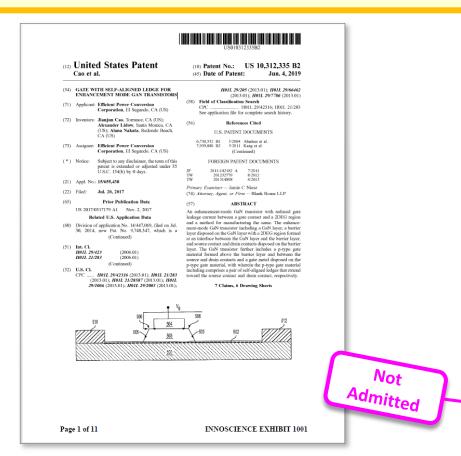

**Patent No.** 10,312,335

# **Petitioner's Demonstrative Exhibits**

Innoscience (Zhuhai) Technology Company, Ltd., and Innoscience America, Inc.

v. Efficient Power Conversion Corporation

January 7, 2024

# Table of Contents

| Petition                                                                                       | Slides  |

|------------------------------------------------------------------------------------------------|---------|

| Overview of the '347 and '335 Patents and the Admitted Prior Art                               | 3-16    |

| Claim Construction                                                                             | 17-28   |

| '335 Patent Invalidity Grounds                                                                 | 29-107  |

| '335 Patent Ground 1: Saxler renders obvious claims 1-7                                        | 37-82   |

| '335 Patent Ground 2: Saxler-Yoshida renders obvious claims 1-7                                | 83-85   |

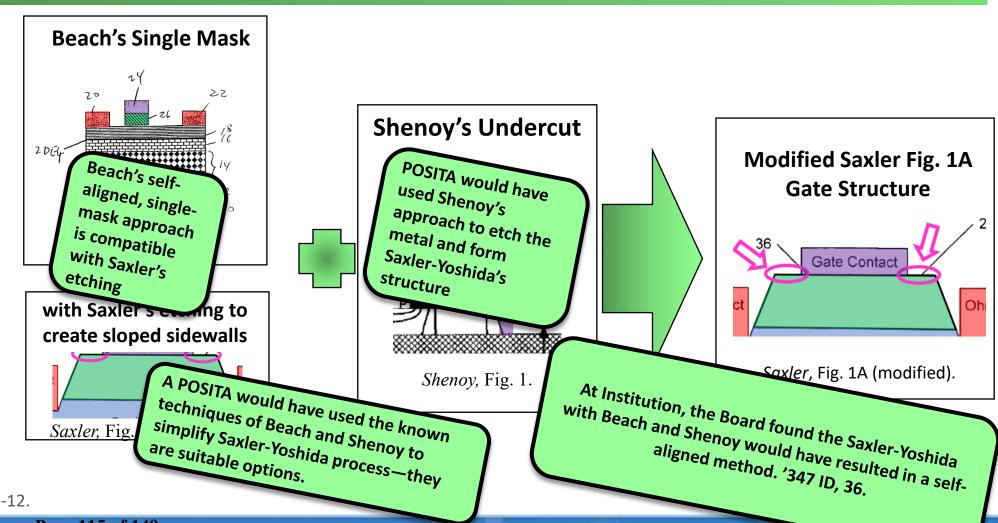

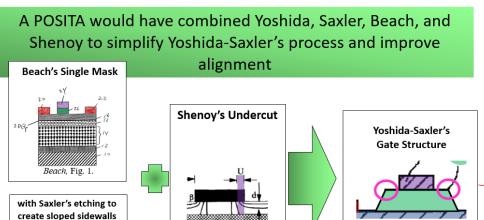

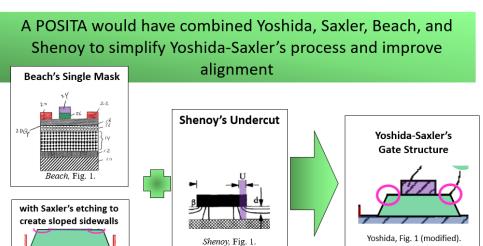

| '335 Patent Ground 3: Saxler-Yoshida in view of Beach and Shenoy renders obvious claims 2, 5-7 | 86      |

| '335 Patent Ground 4: Yoshida renders obvious claims 1-7                                       | 87-101  |

| '335 Patent Ground 5: Yoshida-Saxler renders obvious claims 1-7                                | 102-105 |

| '335 Patent Ground 6: Yoshida-Saxler in view of Beach and Shenoy renders obvious claims 2, 5-7 | 106     |

| '347 Patent Invalidity Grounds                                                                 | 107-148 |

| '347 Patent Grounds 1-2: Saxler (+Yoshida) renders obvious Claims 1-3                          | 112-121 |

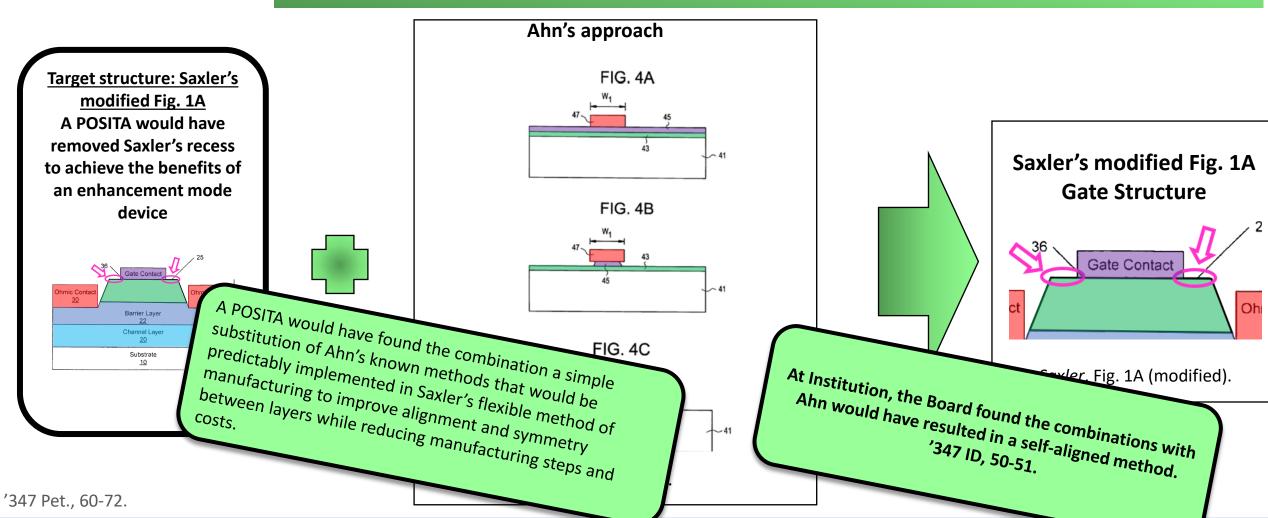

| '347 Patent Ground 3: Saxler and Ahn Render Obvious Claims 1-3                                 | 122-129 |

| '347 Patent Ground 4: Yoshida-Saxler in view of Beach and Shenoy renders obvious claims 1-3    | 130-138 |

| '347 Patent Ground 5: Yoshida and Ahn Render Obvious Claims 1-3                                | 139-148 |

# Overview of the '347 and '335 Patents and the Admitted Prior Art

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE Page 3 of 149

# The '347 and '335 patents

#### '347 patent claim 1: Method

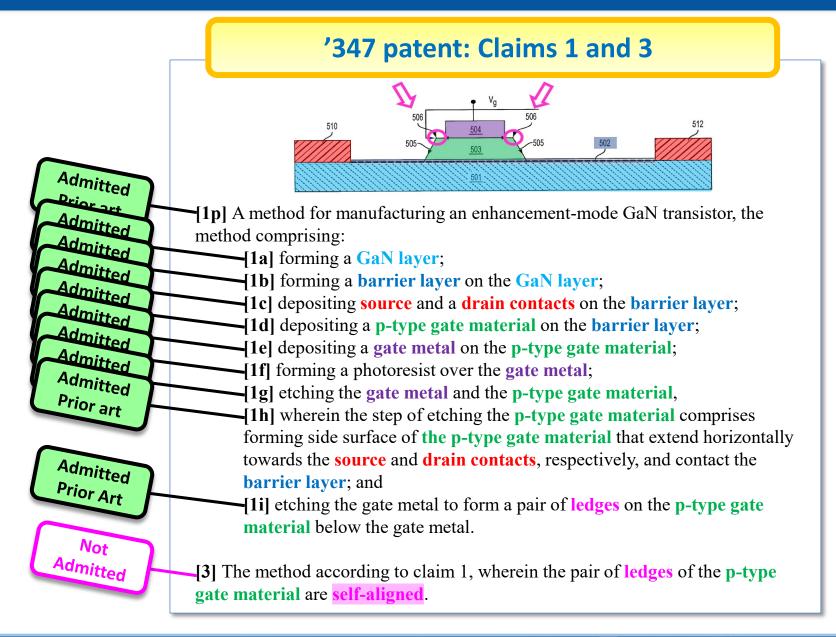

[1p] A method for manufacturing an enhancement-mode GaN transistor, the method comprising:

[1a] forming a GaN layer;

[1b] forming a barrier layer on the GaN layer;

[1c] depositing source and a drain contacts on the barrier layer;

[1d] depositing a p-type gate material on the barrier layer;

[1e] depositing a gate metal on the p-type gate material;

[1f] forming a photoresist over the gate metal;

[1g] etching the gate metal and the p-type gate material,

[1h] wherein the step of etching the p-type gate material comprises forming side surface of the p-type gate material that extend horizontally towards the source and drain contacts, respectively, and contact the barrier layer; and

[1i] etching the gate metal to form a pair of ledges on the p-type gate material below the gate metal..

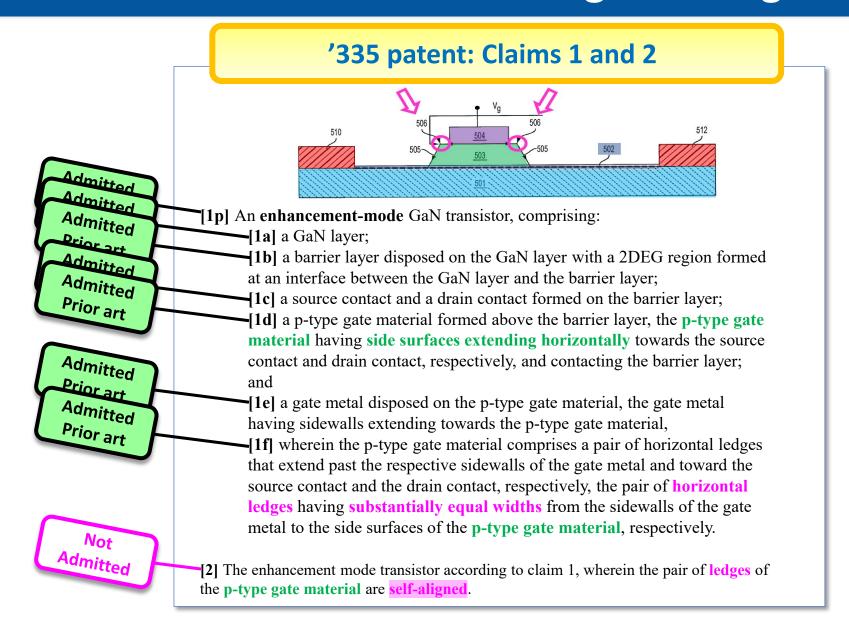

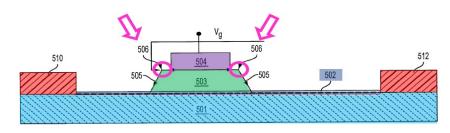

### '335 patent claim 1: Device

[1p] An enhancement-mode GaN transistor, comprising:

[1a] a GaN layer;

[1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;

[1c] a source contact and a drain contact formed on the barrier layer;

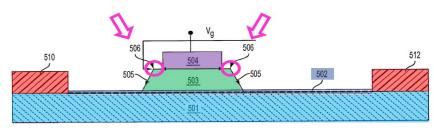

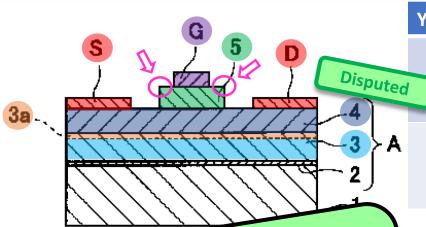

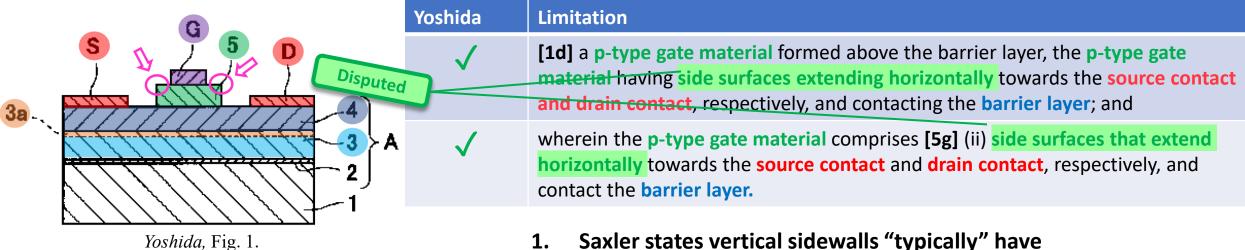

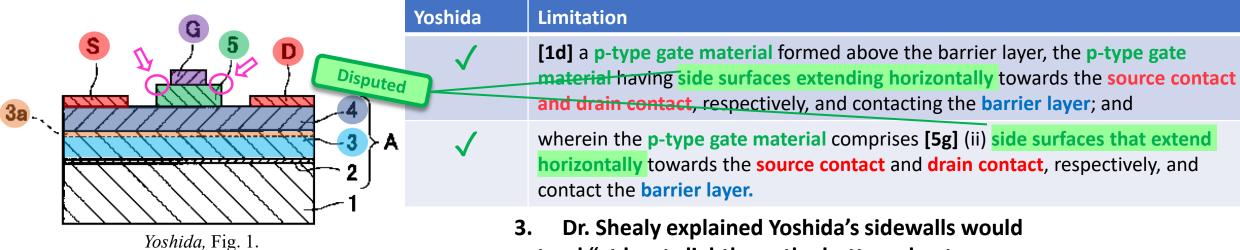

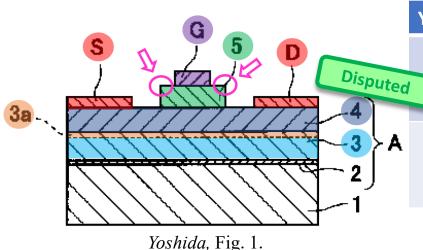

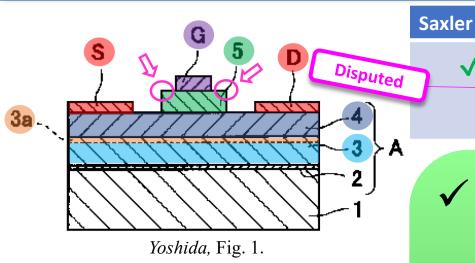

[1d] a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and

[1e] a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,

[1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively.

A pair of self-aligned ledges on p-type gate material is the *only* claimed feature of that is not admitted prior art

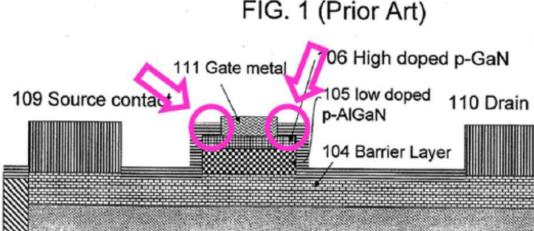

## Admitted Prior Art: '335 and '347 Patent

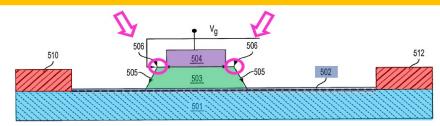

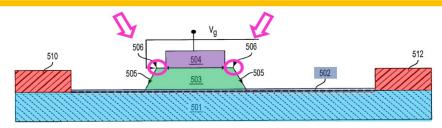

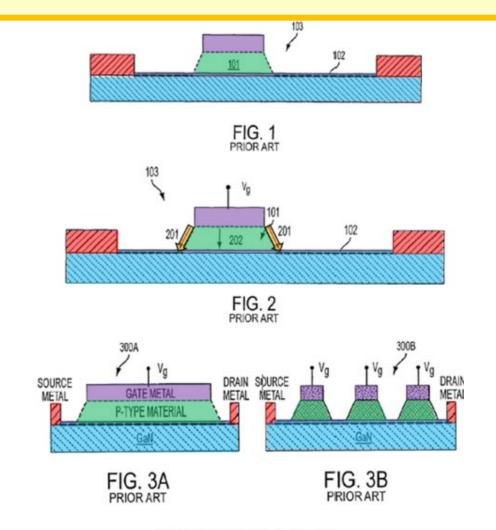

Ex. 1001, Figs. 1-2, 3A-3B.

A pair of self-aligned ledges on p-type gate material is the *only* claimed feature of that is not admitted prior art

Admitted Prior Art: '335 and '347 Patent

Priority Application Lidow (Ex. 1011) shows prior art ledges of equal width but does not describe that they are self-aligned

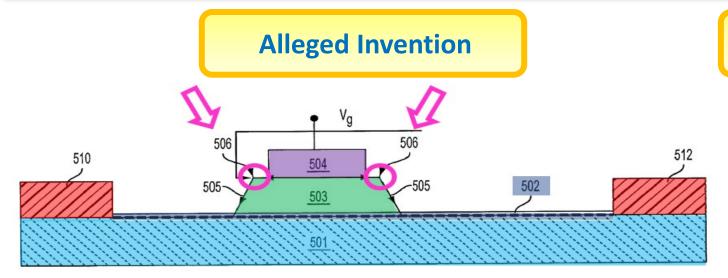

# Admitted Prior Art Has All But Self-Aligned Ledges

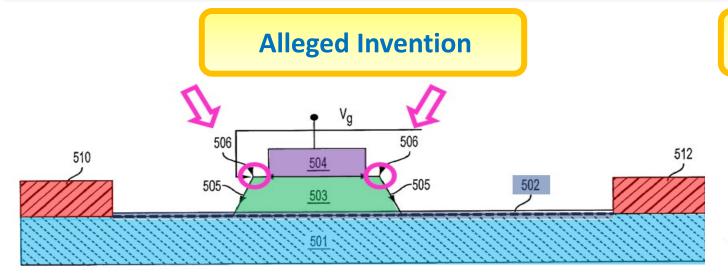

#### **Alleged Invention**

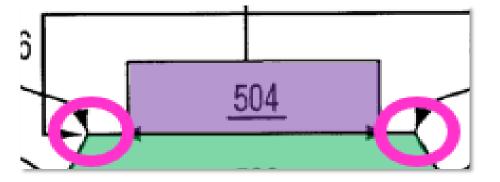

A pair of self-aligned ledges on p-type gate material is the *only* claimed feature of that is not admitted prior art

**MInnoscience**

# Admitted Prior Art Has All But Self-Aligned Ledges

'347 Pet., 8-12.

# Admitted Prior Art Has All But Self-Aligned Ledges

'335 Pet., 8-13.

#### Before April 8, 2009, the following were known:

- ✓ [1.a] Forming a GaN layer;

- ✓ [1.b] Forming a barrier layer on ✓ [1.h] Etching the p-type gate the GaN layer; material to form side surface

- ✓ [1.c] Depositing source and drain contacts on the barrier layer;

- √ [1.d] Depositing a p-type gate material on the barrier layer;

- ✓ [1.e] Depositing a gate metal on the p-type gate material;

- √ [1.f] Forming a photoresist over the gate metal;

- √ [1.g] Etching the gate metal, and;

- ✓ [1.h] Etching the p-type gate material to form side surfaces that slope towards the source and drain contacts;

- ✓ [2.a] 1.a-1.g (agove)

- ✓ [2.b] etching the p-type gate material; and

- √ [2.c] including a pair of ledges on the p-type gate material below the gate metal;

- √ [3] self-aligned gate structures

- All facts thus admitted. '347 Reply, 2; AVX

Corp. v. Presidio Components, Inc., IPR201800292, Paper No. 16 at 9 (P.T.A.B. May 15,

2019).

- Patent Owner sidestepped the merits by asking the Board to "ignore[]" the statement because it did not cite the record. '347 POR, 10.

- A Statement "preferably" cites the record, but the law does not require citations. 37 C.F.R. § 42.22(c).

- The Petition repeatedly showed the patent admitted these facts. '347 Pet., 8-11, 18; '347 Shealy, [044]-[046].

#### Before April 8, 2009, the following were known:

- ✓ [1.a] A GaN layer;

- ✓ [1.b] An AlGaN barrier layer disposed on the GaN layer;

- √ [1.c] Source and drain electrodes disposed on the AlGaN barrier layer;

- √ [1.d] A gate structure disposed on the barrier layer between source and drain electrodes;

- √ [1.e] A gate structure with a ptype GaN layer with sloped sidewalls that extend horizontally towards the source and drain electrodes;

- √ [1.f] A gate structure with an overlying gate metal;

- ✓ [2] Self-aligned gate structures.

- All facts thus admitted. '335 Reply, 2; AVX

Corp. v. Presidio Components, Inc., IPR201800292, Paper No. 16 at 9 (P.T.A.B. May 15,

2019).

- Patent Owner sidestepped the merits by asking the Board to "ignore[]" the statement because it did not cite the record. '335 POR, 8.

- A Statement "preferably" cites the record, but the law does not require citations. 37 C.F.R. § 42.22(c).

- The Petition repeatedly showed the patent admitted these facts. '335 Pet., 8-9, 17-18; '335 Shealy [044]-[046].

A pair of self-aligned ledges on p-type gate material is the *only* feature of the claimed enhancement mode GaN transistor that is not admitted prior art

[1p] An enhancement-mode GaN transistor, comprising:

[1a] a GaN layer;

[1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;

[1c] a source contact and a drain contact formed on the barrier layer;

[1d] a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and

[1e] a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,

[1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively.

[2] The enhancement mode transistor according to claim 1, wherein the pair of ledges of the p-type gate material are self-aligned.

'335 Patent, Cover; '335 Pet., 1-2, 8-13.

Forming a pair of self-aligned ledges on p-type gate material is the *only* feature of the claimed method that is not admitted prior art

[1p] A method for manufacturing an enhancement-mode GaN transistor, the method comprising:

- [1a] forming a GaN layer;

- [1b] forming a barrier layer on the GaN layer;

- [1c] depositing source and a drain contacts on the barrier layer;

- [1d] depositing a p-type gate material on the barrier layer;

- [1e] depositing a gate metal on the p-type gate material;

- [1f] forming a photoresist over the gate metal;

- [1g] etching the gate metal and the p-type gate material,

- [1h] wherein the step of etching the p-type gate material comprises forming side surface of the p-type gate material that extend horizontally towards the source and drain contacts, respectively, and contact the barrier layer; and

- [1i] etching the gate metal to form a pair of ledges on the p-type gate material below the gate metal.

[3] The method according to claim 1, wherein the pair of ledges of the p-type gate material are self-aligned.

EX. 1001, Cover; '347 Pet., 1-2.

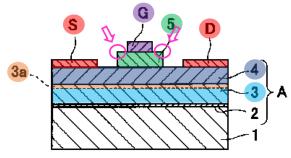

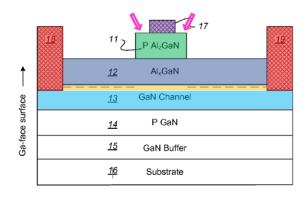

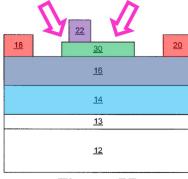

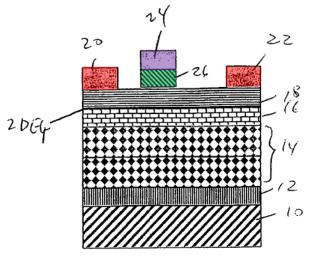

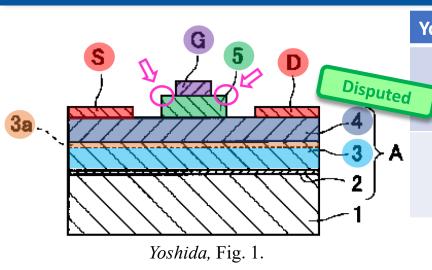

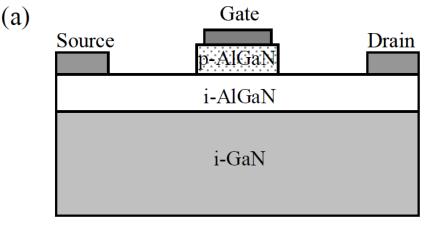

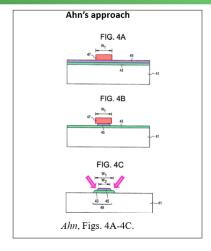

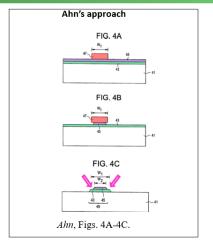

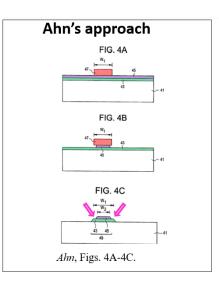

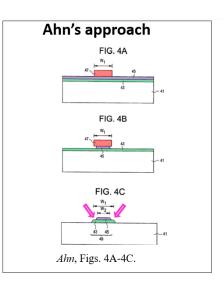

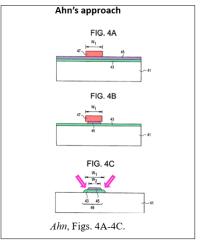

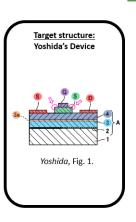

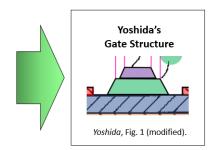

# The alleged new feature was well known

Horizontal ledges on p-type gate material were well known as of April 8, 2009

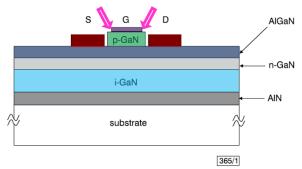

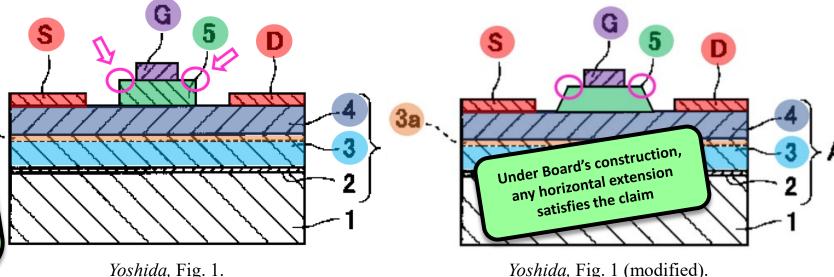

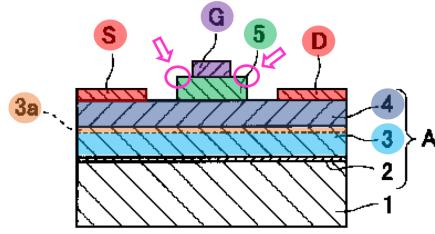

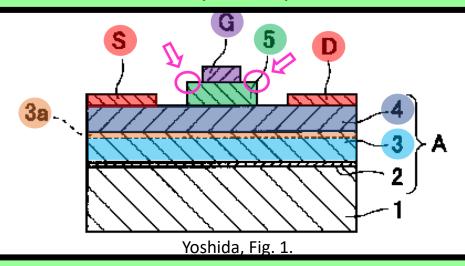

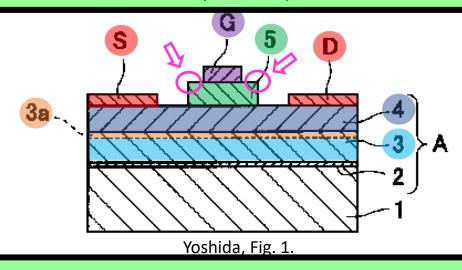

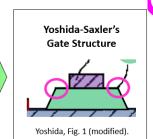

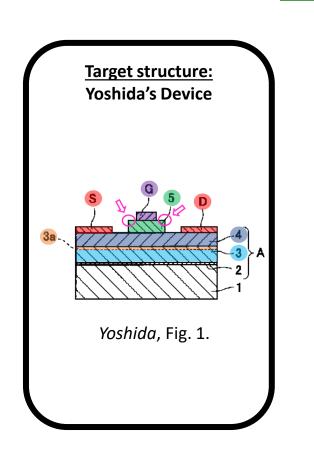

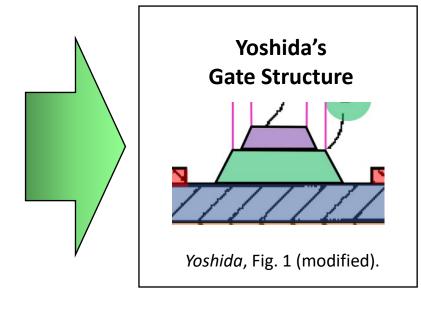

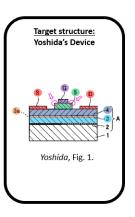

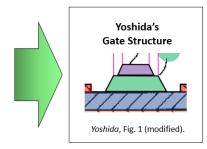

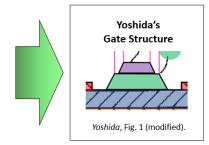

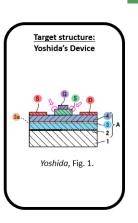

Ex. 1005 (Yoshida) (1999)

Ex. 1017 (Suh) (2009).

Ex. 1007 (Saxler) (2006)

Fig. 1 Schematic diagram of structure of pn junction regrown gate HFET

Ex. 1018 (*Hu*) (2000)

Figure 5B

Ex. 1015 (Smith) (2002).

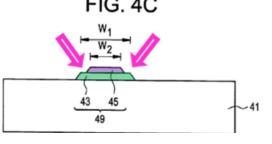

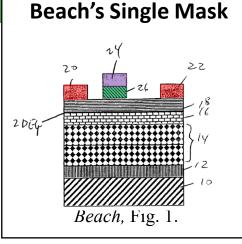

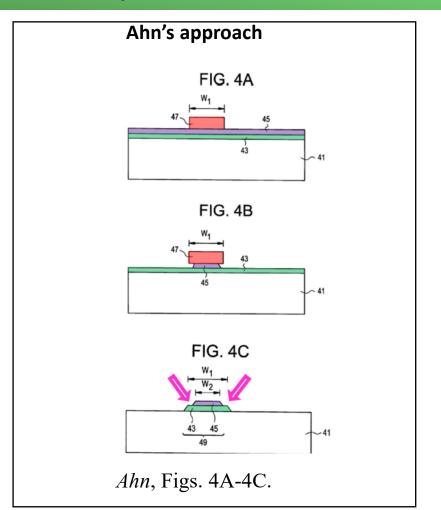

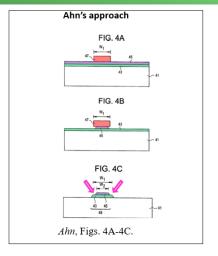

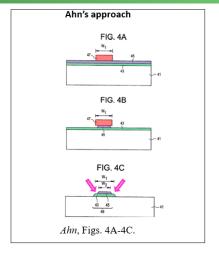

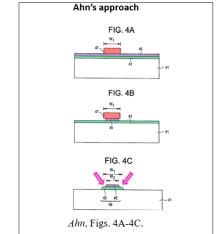

**Self-Aligned** gate structures using a single mask were well known as of April 8, 2009

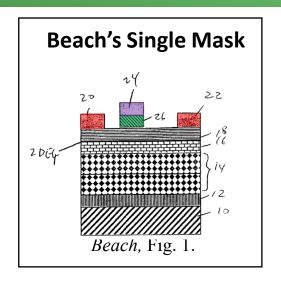

Beach, Fig. 1.

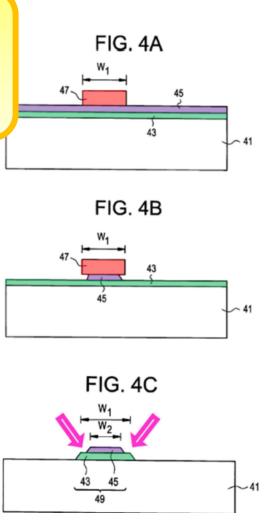

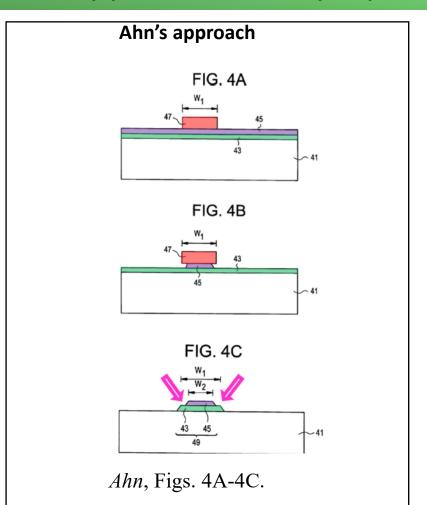

Ahn, Figs. 4A-4C.

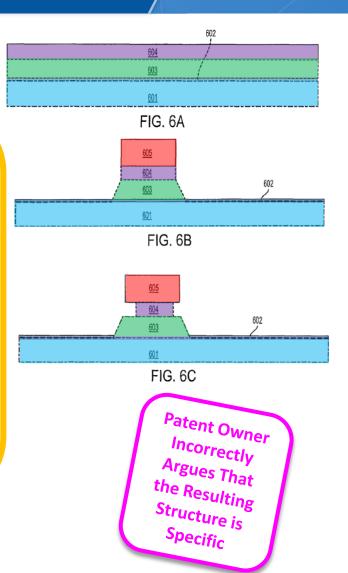

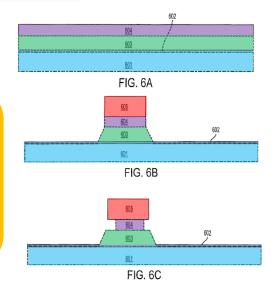

'335 and '347 Patents, Figs. 6A-6C

FIG. 6C

'335 Pet., 6-7, 11-12, 57-58, 60-63; '347 Pet., 6-7, 11-12, 26-35, 60-62; Beach, [0040], [0045], [0054], Fig. 1; Smith, [0041]-[0044] Fig. 5B; Ahn, 4:52-49, 5:55-62, 6:27-37, 7:15-46, Figs. 4A-4C; '347 Shealy, [094].

# Claim Construction

## **Two Terms Construed in the Petitions**

1) '335 and '347 Patents: "side surfaces" limitations

<u>'335 Patent claims 1 and 5</u>: "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer"

<u>'347 Patent claim 1:</u> "forming side surfaces of the p-type gate material that extend horizontally towards the source and drain contacts, respectively, and contact the barrier layer"

2) '335 Patent: "self-aligned" limitations

'335 Patent, claims 2 and 5: "self-aligned" ledges

2. The prior art need not teach "selfaligned" because it is a product-by process limitation. 1. No construction is needed to resolve the dispute--any horizontal extension satisfies the limitation

'335 Pet., 18-24; '347 Pet., 19-23.

'335 Patent claims 1 and 5: "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer"

<u>'347 Patent claim 1:</u> "forming side surfaces of the p-type gate material that extend horizontally towards the

source and drain contacts, respectively, and contact the barrier layer"

| Petitioners' Proposed  Construction                                          |                                                                         |                        |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------|

| type gate material such<br>that the bottom of the<br>p-type gate material is | such that the bottom of<br>the material is wider<br>than the top of the | No construction needed |

#### **Board's Construction at** Institution

No construction needed

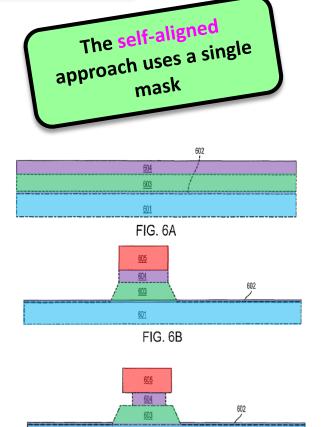

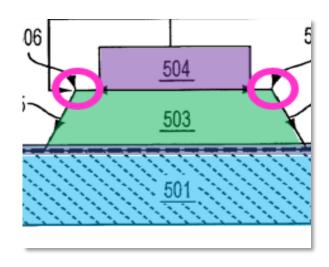

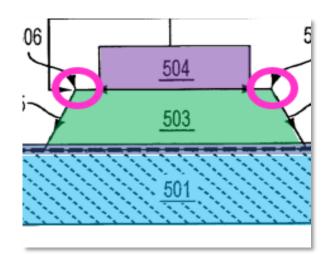

06 503 No need to resolve dispute further for purposes of validity. Petitioner adopts Board's construction for this

proceeding

**Under Board's** construction, any horizontal extension

satisfies the claim

'335 Pet., 18-23; Paper No. 7 ('335 POPR), 6-10; Paper No. 11 ('335 ID), 11-16. '347 Pet., 19-23; Paper No. 7 ('347 POPR), 6-9; Paper No. 11 ('347 ID), 11-15.

<u>'335 Patent claims 1 and 5</u>: "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer"

<u>'347 Patent claim 1:</u> "forming side surfaces of the p-type gate material that extend horizontally towards the

source and drain contacts, respectively, and contact the barrier layer"

"[B]ecause no express construction is needed for our decision, we do not construe them. See Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co., 868 F.3d 1013, 1017 (Fed. Cir. 2017)."

PNC Bank, N.A. v. United Servs. Auto. Ass'n, No. IPR2021-01073, Paper 72, 13 (P.T.A.B. Jan. 19, 2023). Board's Construction at Institution

No construction needed

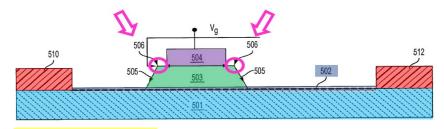

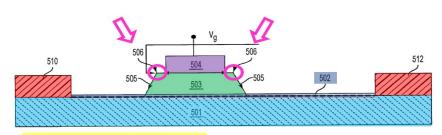

construction, any horizontal extension satisfies the claim  $\frac{504}{503}$

**Under Board's**

No need to resolve dispute further for purposes of validity. Petitioner adopts Board's construction for this proceeding

'335 Pet., 18-23; Paper No. 7 ('335 POPR), 6-10; Paper No. 11 ('335 ID), 11-16. '347 Pet., 19-22; Paper No. 7 ('347 POPR), 6-9; Paper No. 11 ('347 ID), 11-15.

## **Two Terms Construed in the Petitions**

1) '335 and '347 Patents: "side surfaces" limitations

<u>'335 Patent claims 1 and 5</u>: "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer"

<u>'347 Patent claim 1:</u> "forming side surfaces of the p-type gate material that extend horizontally towards the source and drain contacts, respectively, and contact the barrier layer"

1. No construction is needed to resolve the dispute—any horizontal extension satisfies the limitation

#### '335 Patent claims 2 and 5: "self-aligned" ledges

| Petitioners' Proposed Construction | Patent Owner's IPR Construction |

|------------------------------------|---------------------------------|

| Product-by-process                 | Not product-by-process          |

# Board's Construction at Institution

Invite the parties to brief this issue, raising questions on Patent Owner's Analysis [2] The enhancement-mode GaN transistor according to claim!, wherein the pair of horizontal ledges of the p-type gate material are self aligned.

"Self-aligned" describes how the ledges are made, not what they are: no patentable weight

[5f] wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively

# '335 Patent: "Self-Aligned" Lends No Patentable Weight

#### <u>'335 Patent claims 2 and 5</u>: "self-aligned" ledges

| Petitioners' Proposed Construction | Patent Owner's IPR<br>Construction |

|------------------------------------|------------------------------------|

| Product-by-process                 | Not product-by-process             |

# Board's Construction at Institution

Invite the parties to brief this issue, raising questions on Patent Owner's Analysis The Board noted "at least one other method can produce transistors with the same structure features" as a "self-aligned" approach and "the language in the Specification addresses making an old product using a new, more advantageous process." '335 ID, 18-19.

Patentability of the claimed transistor does not depend on how it is made. The patent says the claimed structure can be made by other processes.

#### <u>'335 Patent claims 2 and 5</u>: "self-aligned" ledges

| Petitioners' Proposed Construction | Patent Owner's IPR<br>Construction |

|------------------------------------|------------------------------------|

| Product-by-process                 | Not product-by-process             |

# Board's Construction at Institution

Invite the parties to brief this issue, raising questions on Patent Owner's Analysis

#### *In re Thorpe,* 777 F.2d 695, 697 (Fed. Cir. 1985)

"The patentability of a product does not depend on its method of production. If the product in the product-by-process claim is the same as or obvious from a product of the prior art, the claim is unpatentable even though the prior product was made by a different process."

# Kamstrup A/S v. Axioma Metering UAB, 43 F.4th 1374, 1381-83 (Fed. Cir. 2022) Finding "cast in one piece" in claim to flow meter a product-by-process element that gives no patentable weight);

United Therapeutics Corp. v. Liquidia Techs., Inc., 74 F.4th 1360, 1373 (Fed. Cir. 2023)

"As these claims are product claims, they are anticipated by a disclosure of the same product irrespective of the processes by which they are made.").

Patentability of the claimed transistor does not depend on how it is made. The patent says the claimed structure can be made by other processes.

'335 Pet., 23-24; '335 ID, 16-20; '335 Reply, 19-21; '335 Sur-Reply, 9.

'335 Patent claims 2 and 5: "self-aligned" ledges

It is undisputed that "self-aligned" refers to how the ledges are made

Patent Owner incorrectly alleges "self-aligned" connotes specific structure: a "minimum CD" (critical dimension) gate width and "substantially equal" ledges

But the patent provides different ways to make these features

# '335 Patent: "Self-Aligned" Lends No Patentable Weight

<u>'335 Patent claims 2 and 5</u>: "self-aligned" ledges

# The patent provides different ways to make "symmetric" ledges

• Claim Differentiation: Claim 1 recites "substantially equal" ledges while claim 2 requires "self-aligned" ledges.

Specification: The two-mask process may result in the possibility of misalignment, acknowledging that it may also result in alignment. '335 patent, 4:52-63.

## The patent provides different ways to make reach "minimum CD"

• Specification: The two-mask process "etch[es] the gate metal to a minimum CD". '335 patent, 4:57-58.

The Reply is consistent with the Institution Decision

**M**Innoscience

Patent Owner's contrary expert testimony should be given no weight. '335 Reply, 20-21 (citing Ex. 2005 ¶¶48-52; Genuine Enabling F.4<sup>th</sup> 1365, 1373 (Fed. Cir. 2022); Phillips v. AWH Corp., 415 F.3d 1303, 1318 (Fed. Cir. 2005)).

'335 Pet., 23-24; '335 ID, 16-20; '335 Reply, 19-21.

<u>'335 Patent claims 2 and 5</u>: "self-aligned" ledges

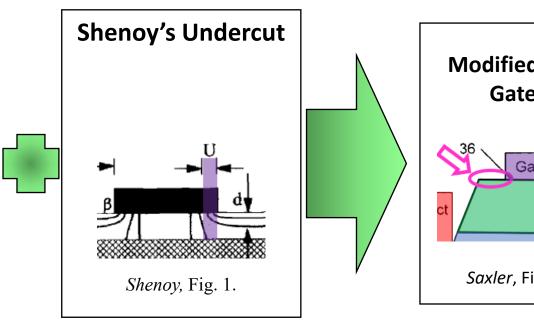

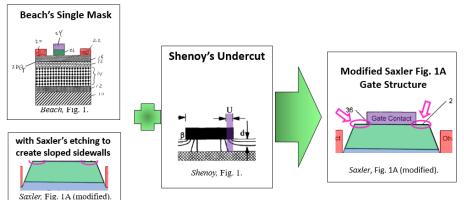

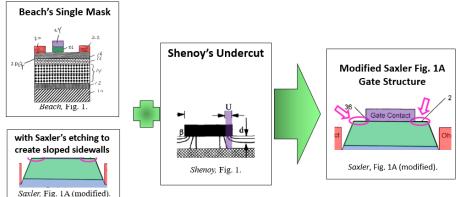

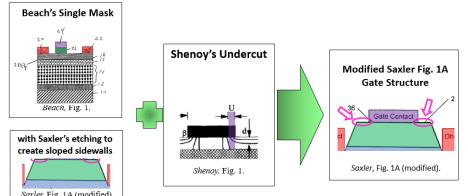

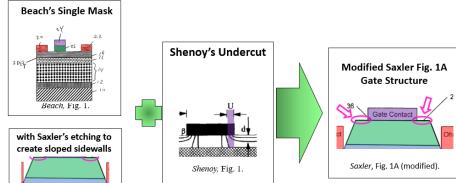

Prior art references Beach and Shenoy are only relied on for "self-aligned" ledges (Grounds 3, 6). If the Board agrees "self-aligned" is a product-by-process term, the claims are invalid over Saxler, Yoshida, and their combinations (Grounds 1-2, 4-5).

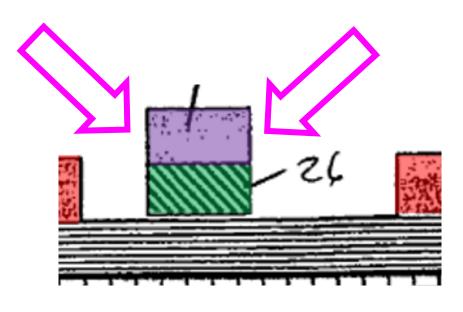

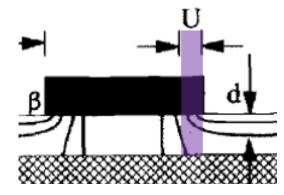

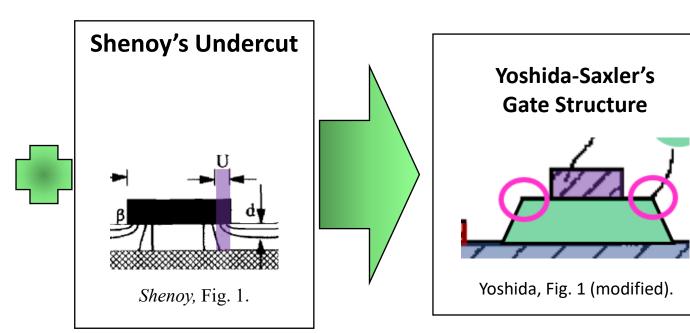

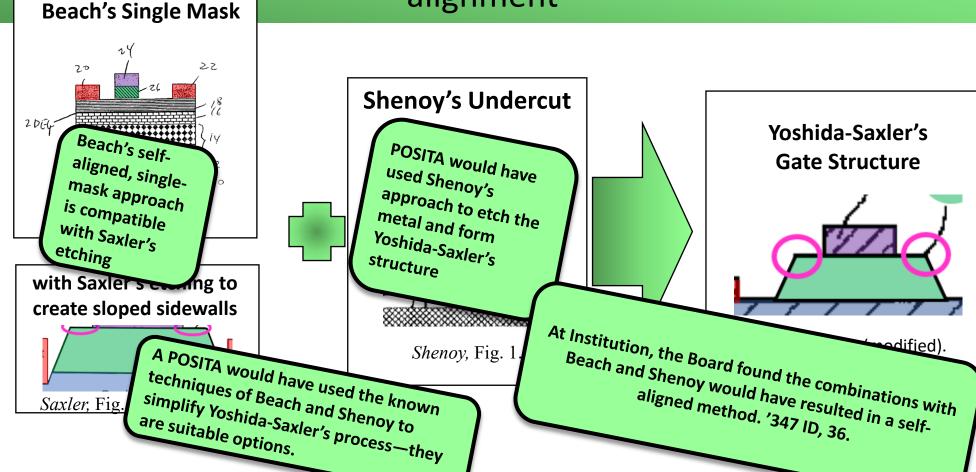

Beach, Fig. 1.

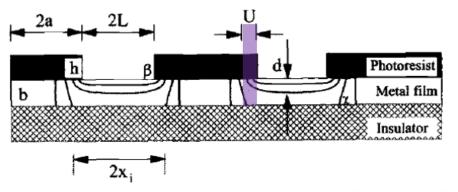

Fig. 1. Schematic diagram of a patterned metal film supported on an insulator.

Shenoy, Fig. 1.

## **Two Terms Construed in the Petitions**

1) '335 and '347 Patents: "side surfaces" limitations

<u>'335 Patent claims 1 and 5</u>: "side surfaces [extending/that extend] horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer"

'347 Patent claim 1: "forming side surfaces of the p-type gate material that extend horizontally towards the source and drain contacts, respectively, and contact the horizontally

towards the source and drain contacts, respectively, and contact the barrier layer"

2) '335 Patent: "self-aligned" limitations

'335 Patent, claims 2 and 5: "self-aligned" ledges

2. The prior art need not teach "selfaligned" because it is a product-by process limitation. 1. No construction is needed to resolve the dispute--any horizontal extension satisfies the limitation

'335 Pet., 18-24; '347 Pet., 19-22.

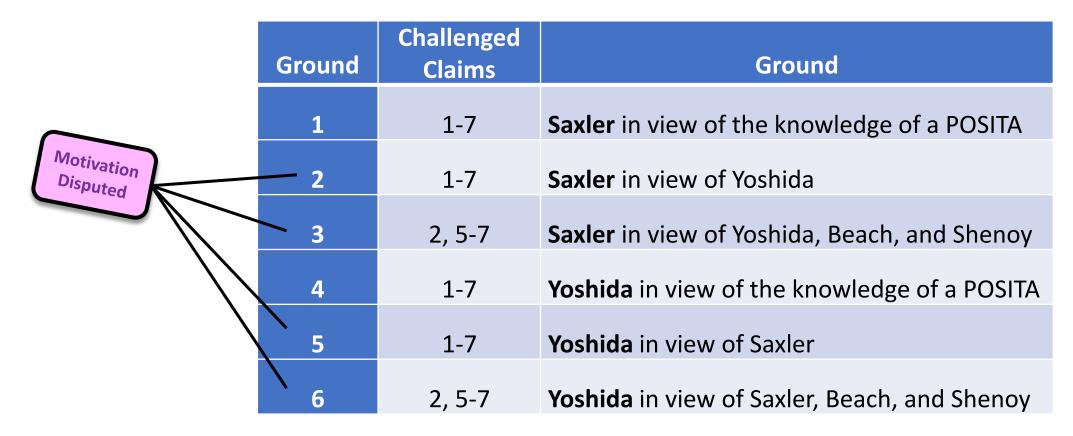

# '335 Patent Invalidity Grounds

|                 | Ground | Challenged<br>Claims | Basis | Prior Art                                    |

|-----------------|--------|----------------------|-------|----------------------------------------------|

| Saxler Grounds  | 1      | 1-7                  | § 103 | Saxler in view of the knowledge of a POSITA  |

|                 | 2      | 1-7                  | § 103 | Saxler in view of Yoshida                    |

|                 | 3      | 2, 5-7               | § 103 | Saxler in view of Yoshida, Beach, and Shenoy |

| Yoshida Grounds | 4      | 1-7                  | § 103 | Yoshida in view of the knowledge of a POSITA |

|                 | 5      | 1-7                  | § 103 | Yoshida in view of Saxler                    |

|                 | 6      | 2, 5-7               | § 103 | Yoshida in view of Saxler, Beach, and Shenoy |

'335 Pet. at 29.

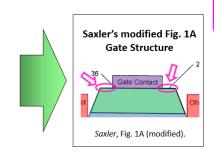

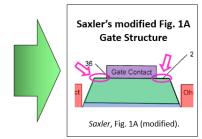

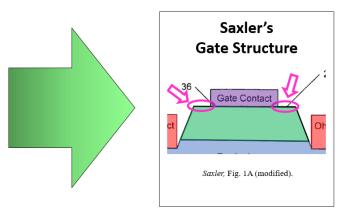

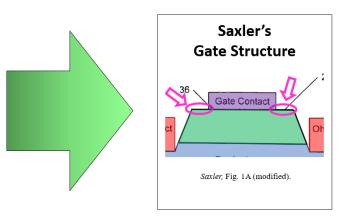

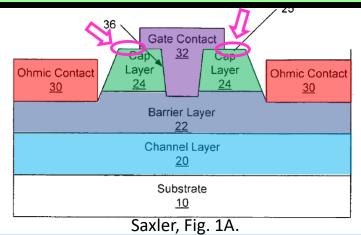

# Saxler Renders the Claims of the '335 Patent Obvious

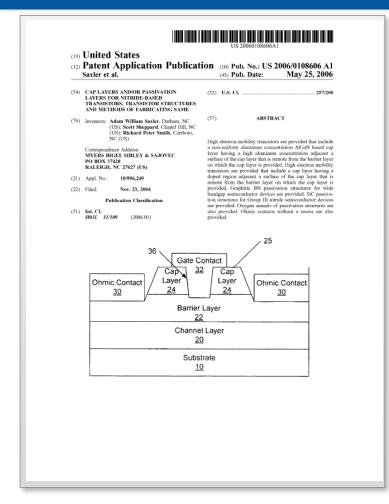

Ex. 1007 at Cover

35 U.S.C. §102(b) Prior Art (published May 25, 2006)

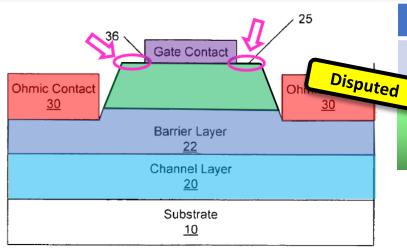

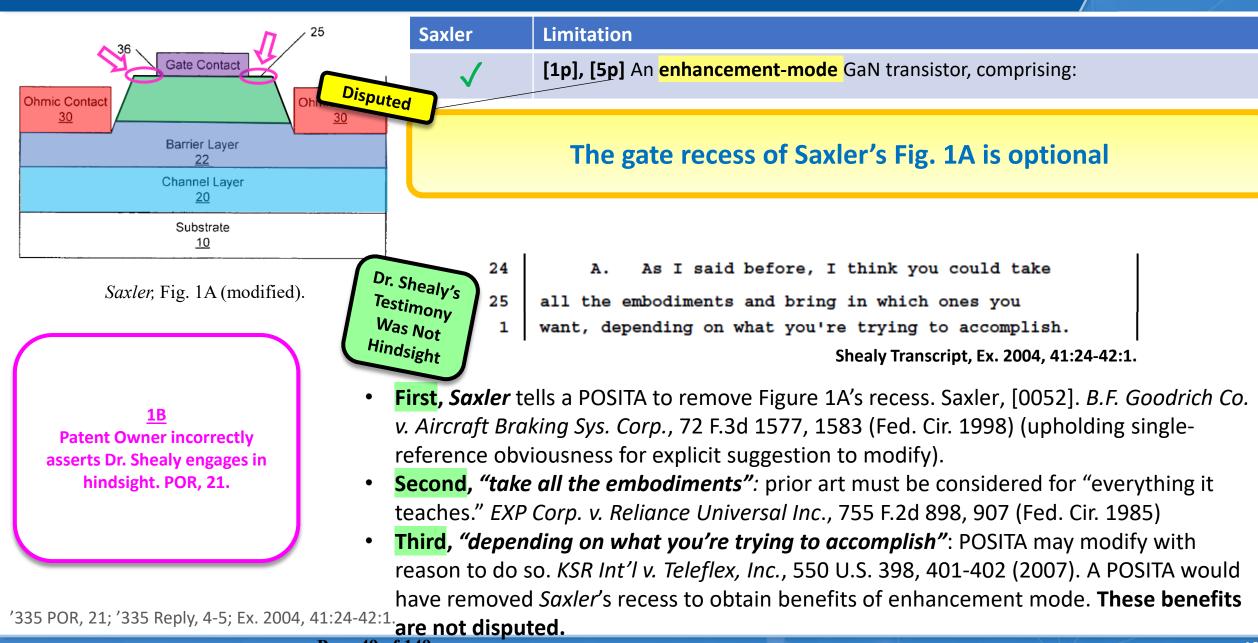

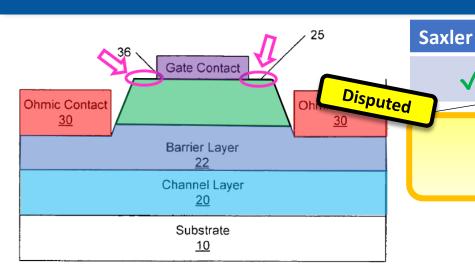

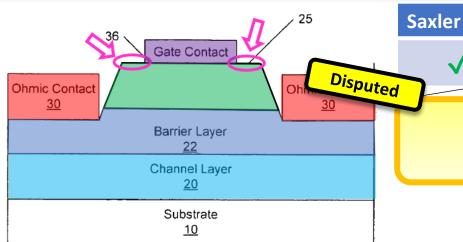

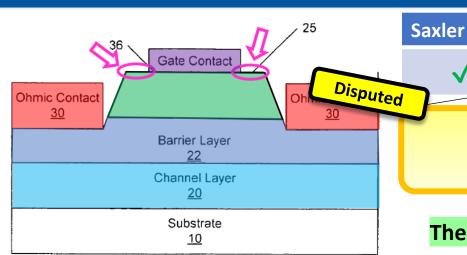

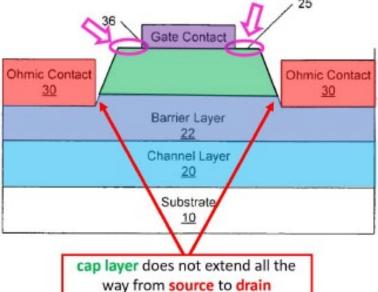

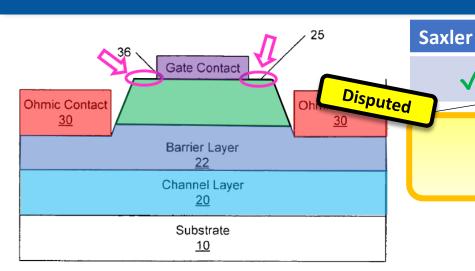

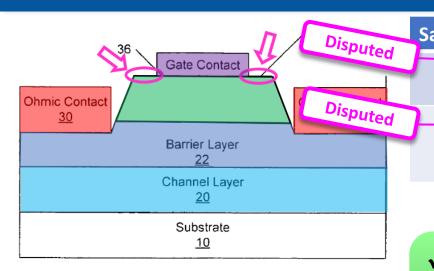

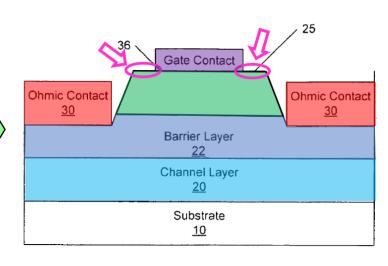

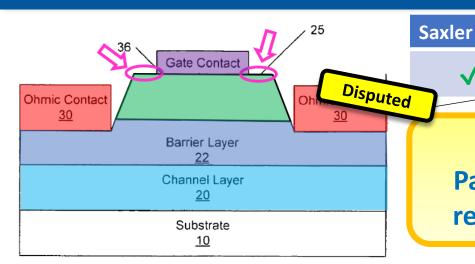

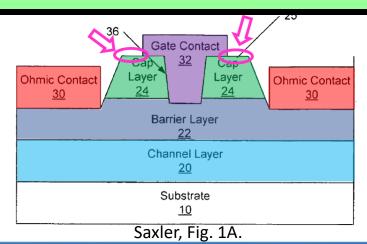

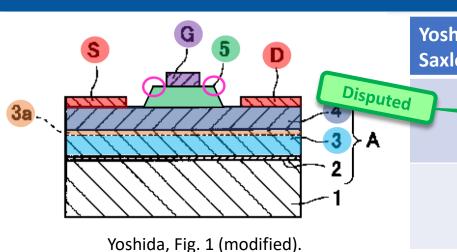

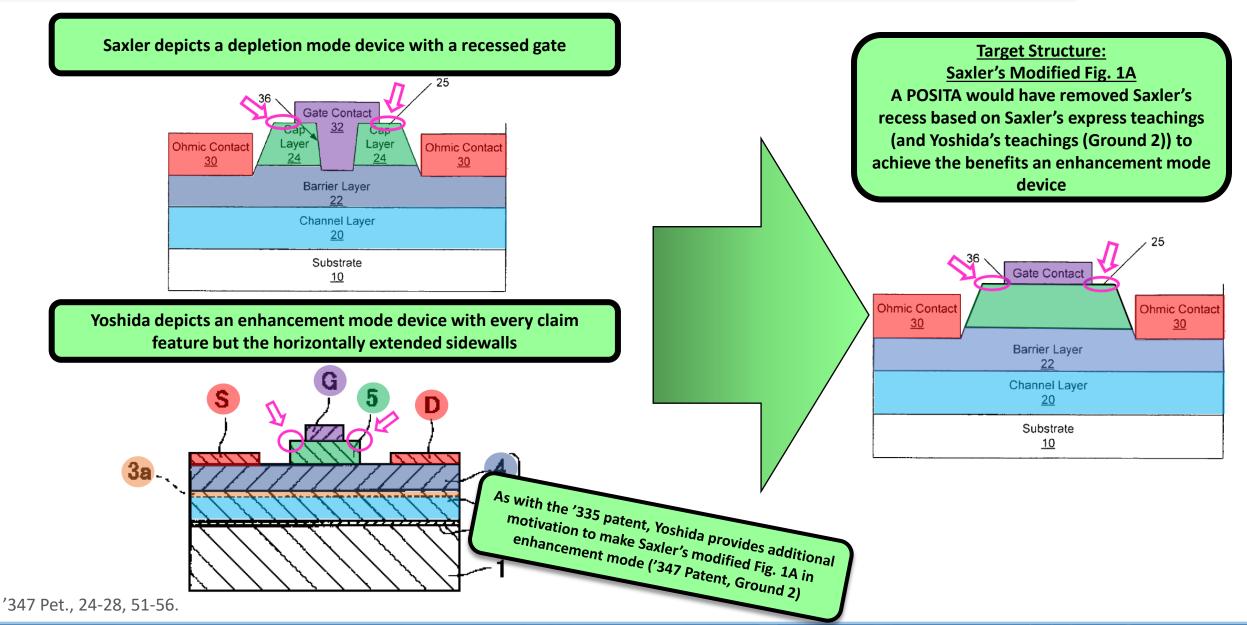

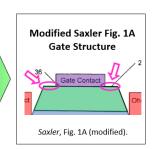

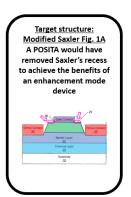

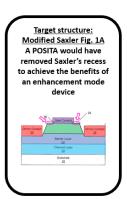

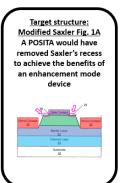

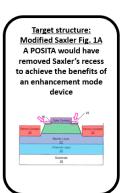

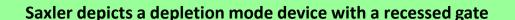

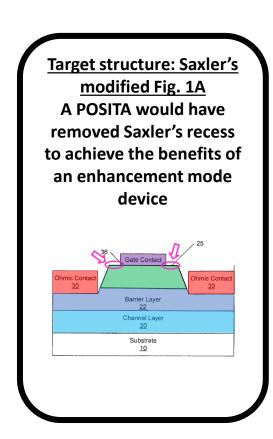

Saxler depicts a depletion mode device with a recessed gate

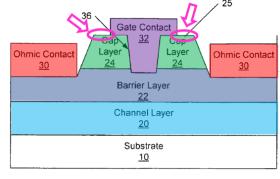

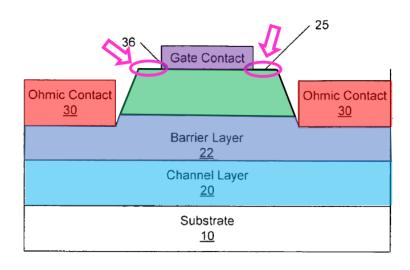

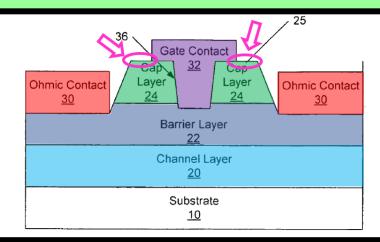

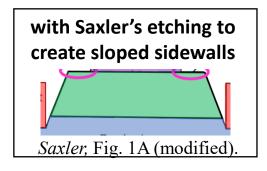

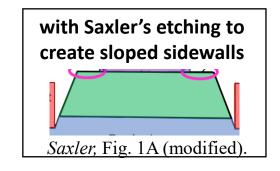

Saxler, Fig. 1A.

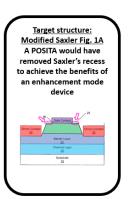

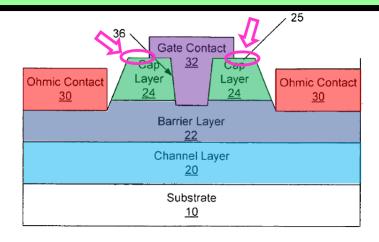

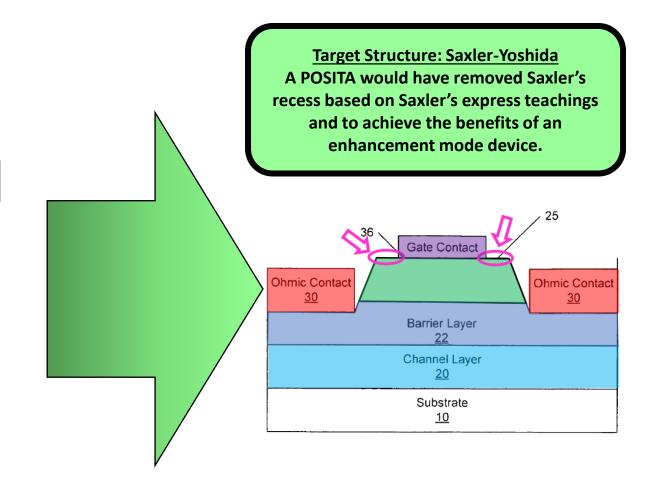

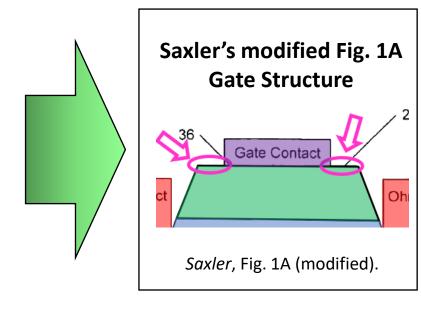

A POSITA would have removed Saxler's recess based on Saxler's express teachings to do so and to achieve an enhancement mode device

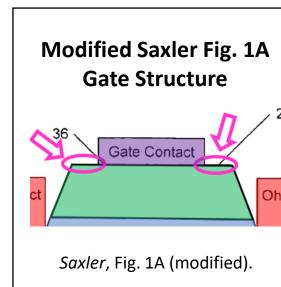

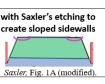

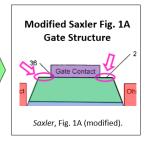

Saxler, Fig. 1A (modified).

If the Board agrees on claim construction, to find all claims invalid over Saxler (Ground 1) or Saxler-Yoshida (Ground 2), the Board need only:

- ✓ Agree modified Fig. 1A would have been obvious and is in enhancement mode

- ✓ Agree Saxler's drawings can be relied on to disclose "substantially equal" ledges (no factual dispute, only a legal dispute that drawings can disclose this limitation)

'335 Pet. at Cover, 16, 25-26, 35-36.

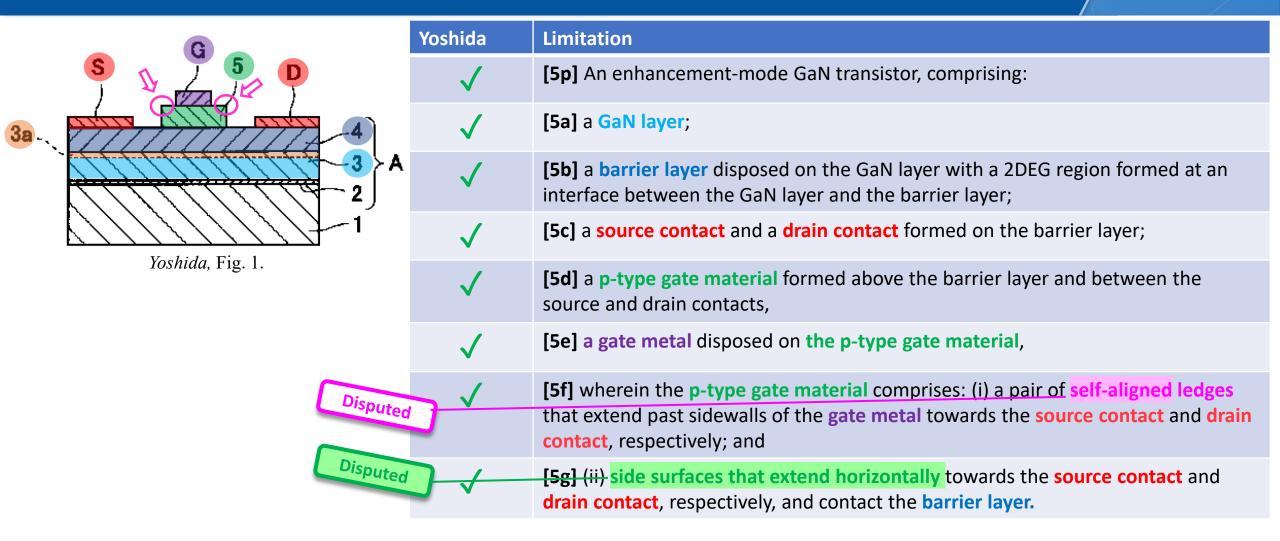

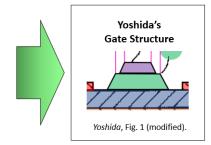

# Yoshida Renders the Claims of the '335 Patent Obvious

At Institution, the Board found

Petitioner's evidence (Saxler, Uemoto, and Dr. Shealy's declaration) supported argument a POSITA would understand argument's sidewalls to have a wider Yoshida's sidewalls to have a wider bottom surface than top. '335 ID, 51.

Ex. 1005 at Cover 35 U.S.C. §102(b) Prior Art (published Sept. 24, 1999)

Yoshida depicts an enhancement mode device with every feature but the horizontally extended sidewalls

Yoshida (Ground 4), the Board need only:

A POSITA would have found horizontally extended sidewalls obvious over Yoshida because perfectly vertical sidewalls were rare in practice when making real devices

If the Board agrees on claim construction, to find all claims invalid over

✓ Agree horizontally extended sidewalls were obvious because perfectly vertical sidewalls were rare in practice when making real devices

✓ Agree Yoshida's drawings can be relied on to disclose "substantially equal" ledges (no factual dispute, only a legal dispute that drawings can disclose this limitation)

'335 Pet. at 16, 27, 67-68.

# '335 Patent: Just Four Claim Features Disputed

Patent Owner only disputes the combinations of prior art shows four features for claims 1-7 of the '335 patent and the motivations to combine the references

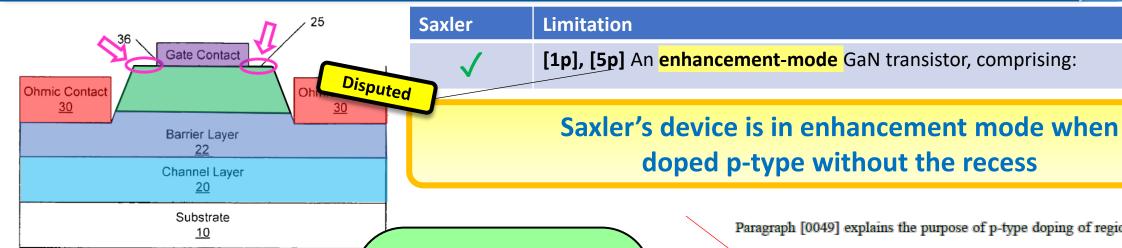

- ✓ [1p], [5p] enhancement mode (Saxler grounds)

- ✓ [1d], [5g] the p-type gate material having side surfaces extending horizontally (Yoshida alone)

- √ [1f] horizontal ledges with substantially equal widths (all grounds)

- √ [2], [5f] self aligned horizontal ledges (all grounds)

- ✓ Motivations to combine (grounds 2-3, 4-5)

At the Board found Petitioners' evidence that p-type doping would provide an enhancement-mode transistor persuasive. The Board further noted that the cap layer does not extend from source to drain as Patent Owner alleged to argue the device nonoperational. '335 ID, 31.

At Institution, the Board found Petitioner's evidence (Saxler, Uemoto, and Dr. Shealy's declaration) supported argument a POSITA would understand Yoshida's sidewalls to have a wider bottom surface

At Institution, the Board reasoned "substantially' is a common approximation or term of degree in patent claims," which Patent Owner did not dispute, so Hockerson does not apply, and drawings can disclose this limitation. '335 ID, 38-39.

The Board noted "at least one other method can produce transistors with the same structure features" as a "self-aligned" approach and "the language in the Specification addresses making an old product using a new, more advantageous process." '335 ID, 18-19.

Patent Owner only disputes the combinations of prior art shows *four* features of the '335 patent claims 1-4

#### Disputed limitations:

- √ [1p] enhancement mode (Saxler grounds)

- ✓ [1d] the p-type gate material having side surfaces extending horizontally (Yoshida alone)

- ✓ [1f] horizontal ledges with substantially equal widths (all grounds)

- √ [2] self aligned ledges (all grounds)

[1p] An enhancement-mode GaN transistor, comprising:

[1a] a GaN layer;

[1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;

[1c] a source contact and a drain contact formed on the barrier layer;

[1d] a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and

[1e] a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,

[1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively.

[2] The enhancement-mode GaN transistor according to claim1, wherein the pair of horizontal ledges of the p-type gate material are self aligned.

Disputed

Disputed

Disputed

Disputed

See generally '335 POR.

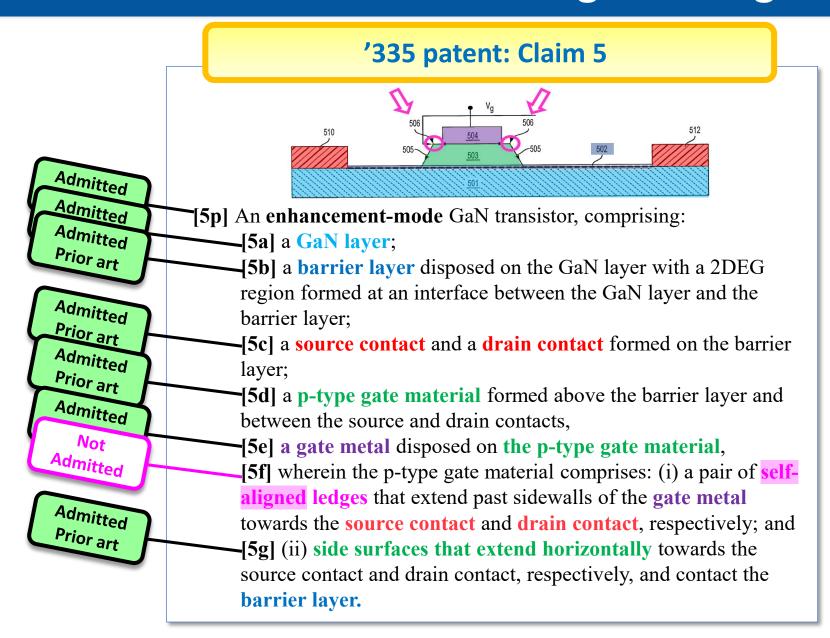

Patent Owner only disputes the combinations of prior art shows *three* features for claims 5-7

#### Disputed limitations:

- √ [5p] enhancement mode (Saxler grounds)

- [5g] the p-type gate material having side surfaces extending horizontally (Yoshida alone)

- √ [5f] self aligned ledges (all grounds)

[5p] An enhancement-mode GaN transistor, comprising:

[5a] a GaN layer;

[5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;

[5c] a source contact and a drain contact formed on the barrier layer;

[5d] a p-type gate material formed above the barrier layer and between the source and drain contacts,

[5e] a gate metal disposed on the p-type gate material,

[5f] wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively; and [5g] (ii) side surfaces that extend horizontally towards the source contact and drain contact, respectively, and contact the barrier layer.

Disputed

Disputed

Disputed

# '335 Patent: Just Four Claim Features Disputed

Patent Owner disputes the motivations to combine for grounds 2, 3, 5, and 6

|   |                 | Ground | Challenged<br>Claims | Basis | Prior Art                                    |

|---|-----------------|--------|----------------------|-------|----------------------------------------------|

|   |                 | 1      | 1-7                  | § 103 | Saxler in view of the knowledge of a POSITA  |

| ı | Saxler Grounds  | 2      | 1-7                  |       |                                              |

|   |                 | 3      | 2, 5-7               |       |                                              |

|   |                 | 4      | 1-7                  |       | Yoshida in view of the knowledge of a POSITA |

| , | Yoshida Grounds | 5      | 1-7                  |       | Yoshida in view of Saxler                    |

|   |                 | 6      | 2, 5-7               |       | Yoshida in view of Saxler, Beach, and Shenoy |

If the Board agrees on claim construction, to find all claims invalid over Saxler (Ground 1) or Saxler-Yoshida (Ground 2), the Board need only:

- ✓ Agree modified Fig. 1A would have been obvious and is in enhancement mode

- ✓ Agree Saxler's drawings can be relied on to disclose "substantially equal" ledges (no factual dispute, only a legal dispute that drawings can disclose this limitation)

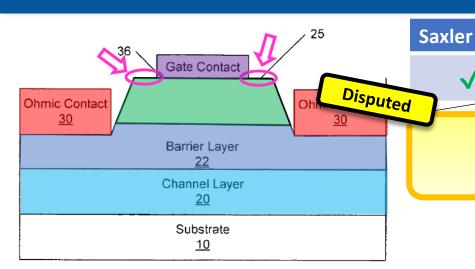

Saxler, Fig. 1A (modified).

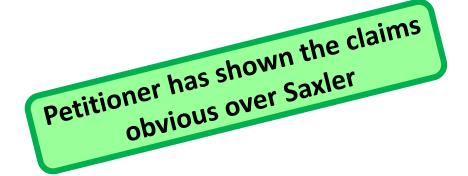

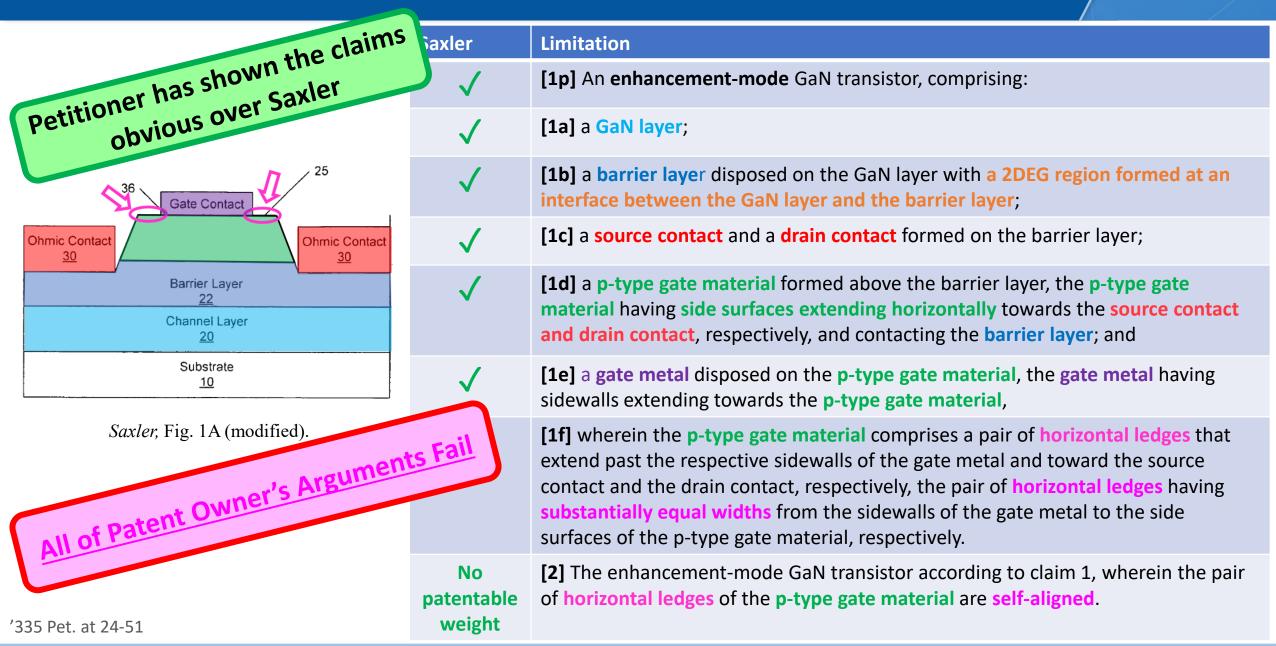

| Saxler                     | Limitation                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>✓</b>                   | [1p] An enhancement-mode GaN transistor, comprising:                                                                                                                                                                                                                                                                                                                            |

| <b>✓</b>                   | [1a] a GaN layer;                                                                                                                                                                                                                                                                                                                                                               |

| <b>√</b>                   | [1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                                                                                                                                                                                                           |

| <b>√</b>                   | [1c] a source contact and a drain contact formed on the barrier layer;                                                                                                                                                                                                                                                                                                          |

| <b>✓</b>                   | [1d] a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and                                                                                                                                              |

| <b>√</b>                   | [1e] a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,                                                                                                                                                                                                                                             |

| <b>✓</b>                   | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively. |

| No<br>patentable<br>weight | [2] The enhancement-mode GaN transistor according to claim 1, wherein the pair of horizontal ledges of the p-type gate material are self-aligned.                                                                                                                                                                                                                               |

'335 Pet. at 24-51

|                                       | Saxler                     | Limitation                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disputed                              | <b>√</b> _                 | [1p] An enhancement-mode GaN transistor, comprising:                                                                                                                                                                                                                                                                                                                            |

| - Sputed                              |                            | [1a] a GaN layer;                                                                                                                                                                                                                                                                                                                                                               |

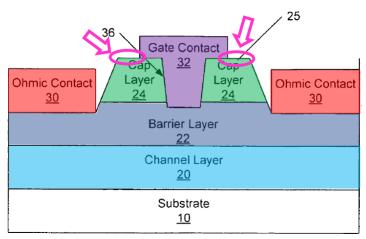

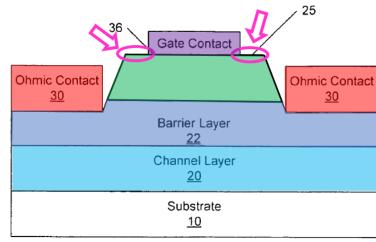

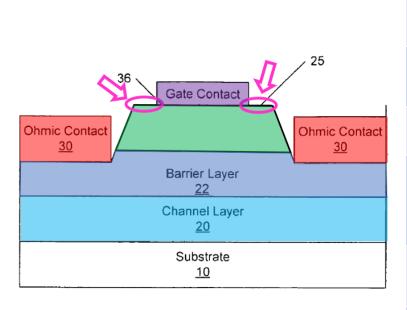

| Gate Contact 25                       | <b>√</b>                   | [1b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                                                                                                                                                                                                           |

| Ohmic Contact 30                      | $\checkmark$               | [1c] a source contact and a drain contact formed on the barrier layer;                                                                                                                                                                                                                                                                                                          |

| Barrier Layer 22 Channel Layer 20     | <b>✓</b>                   | [1d] a p-type gate material formed above the barrier layer, the p-type gate material having side surfaces extending horizontally towards the source contact and drain contact, respectively, and contacting the barrier layer; and                                                                                                                                              |

| Substrate<br>10                       | <b>✓</b>                   | [1e] a gate metal disposed on the p-type gate material, the gate metal having sidewalls extending towards the p-type gate material,                                                                                                                                                                                                                                             |

| Saxler, Fig. 1A (modified).  Disputed |                            | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively. |

| '335 Pet. at 24-51; '335 POR, 16-47.  | No<br>patentable<br>weight | [2] The enhancement-mode GaN transistor according to claim 1, wherein the pair of horizontal ledges of the p-type gate material are self-aligned.                                                                                                                                                                                                                               |

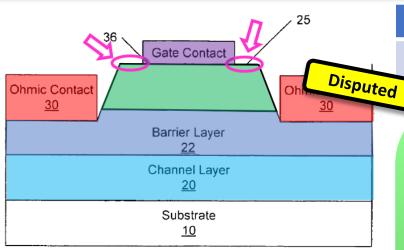

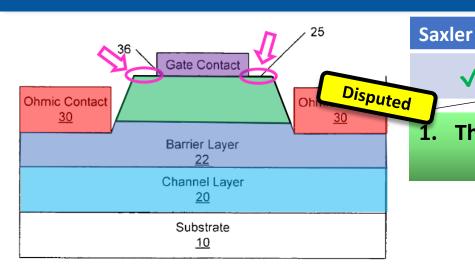

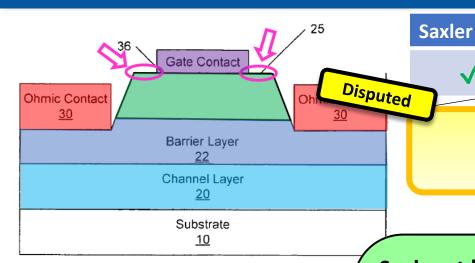

|                                  | Saxler     | Limitation                                                                                                                                                                                      |

|----------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disputed                         | <b>√</b> _ | [5p] An enhancement-mode GaN transistor, comprising:                                                                                                                                            |

|                                  |            | [5a] a GaN layer;                                                                                                                                                                               |

| 36 Gate Contact                  | <b>✓</b>   | [5b] a barrier layer disposed on the GaN layer with a 2DEG region formed at an interface between the GaN layer and the barrier layer;                                                           |

| Ohmic Contact 30                 | <b>✓</b>   | [5c] a source contact and a drain contact formed on the barrier layer;                                                                                                                          |

| Barrier Layer  22  Channel Layer | <b>✓</b>   | [5d] a p-type gate material formed above the barrier layer and between the source and drain contacts,                                                                                           |

| 20<br>Substrate                  | <b>✓</b>   | [5e] a gate metal disposed on the p-type gate material,                                                                                                                                         |

| Saxler, Fig. 1A (modified).      |            | [5f] wherein the p-type gate material comprises: (i) a pair of self-aligned ledges that extend past sidewalls of the gate metal towards the source contact and drain contact, respectively; and |

|                                  | <b>✓</b>   | [5g] (ii) side surfaces that extend horizontally towards the source contact and drain contact, respectively, and contact the barrier layer.                                                     |

'335 Pet. at 24-51; '335 POR, 16-47.

- √ [1p], [5p] enhancement mode (Saxler grounds)

- √ [1f] horizontal ledges with substantially equal widths (all grounds)

- ✓ [2], [5f] self aligned horizontal ledges (all grounds)

- ✓ Motivation to modify Saxler

- √ [1p], [5p] enhancement mode (Saxler grounds)

- √ [1f] horizontal ledges with substantially equal widths (all grounds)

- ✓ [2], [5f] self aligned horizontal ledges (all grounds)

- ✓ Motivation to modify Saxler

- ✓ Saxler's modified Fig. 1A is in enhancement mode.

- ✓ A POSITA would have modified Fig. 1A based on Saxler's teachings and for the benefits of enhancement mode.

Saxler, Fig. 1A (modified).

| Saxler   | Limitation                                                 |

|----------|------------------------------------------------------------|

| <b>√</b> | [1p], [5p] An enhancement-mode GaN transistor, comprising: |

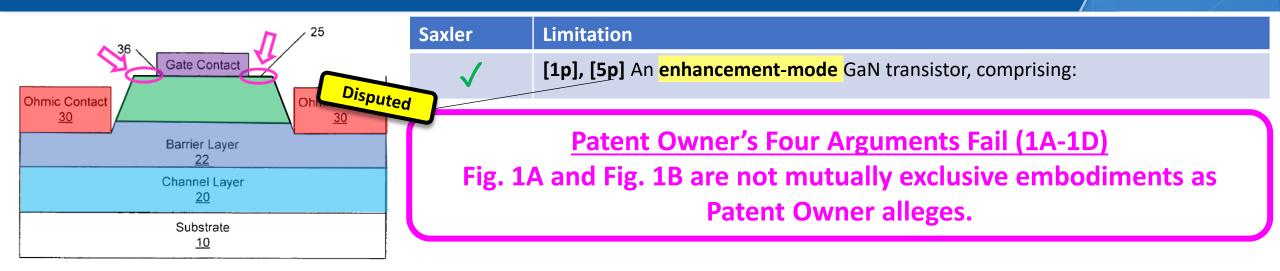

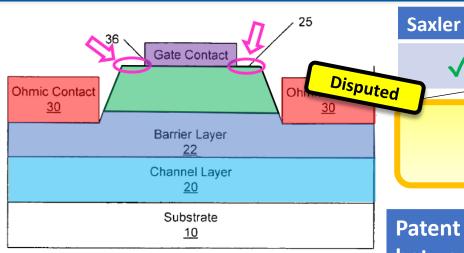

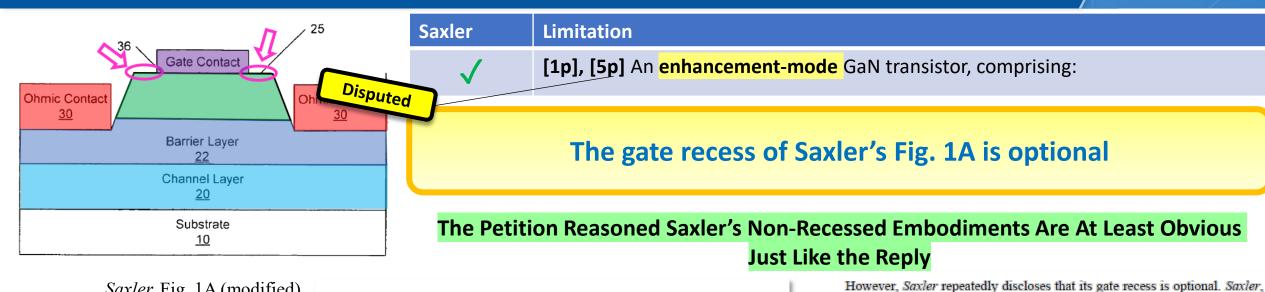

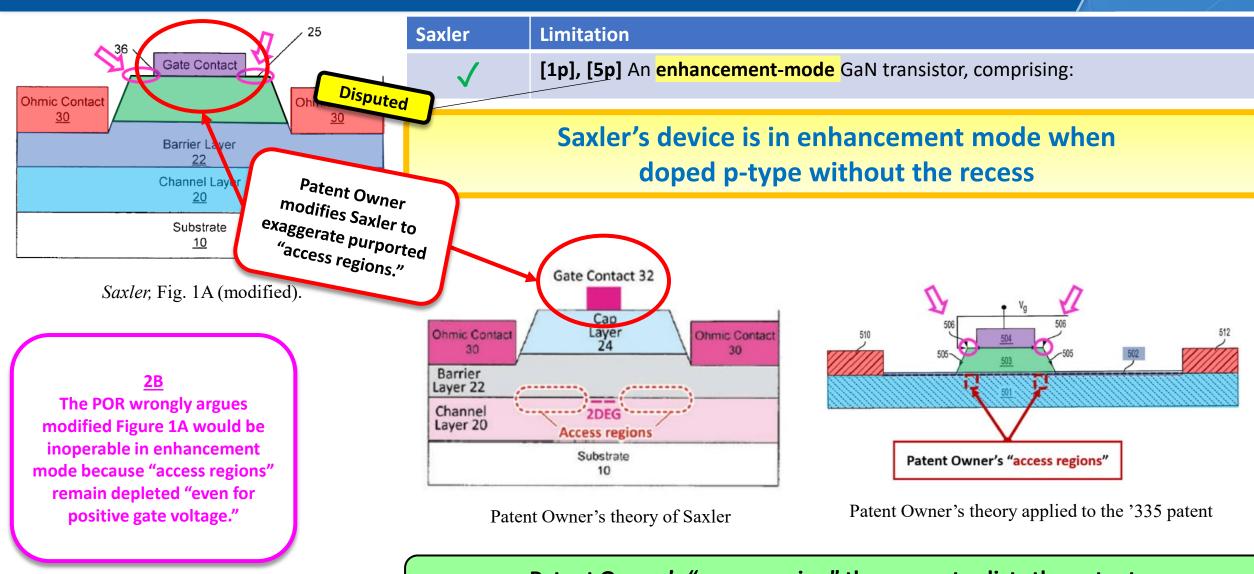

✓ Modified Fig. 1A would have been obvious and is in enhancement mode

## The Petition shows:

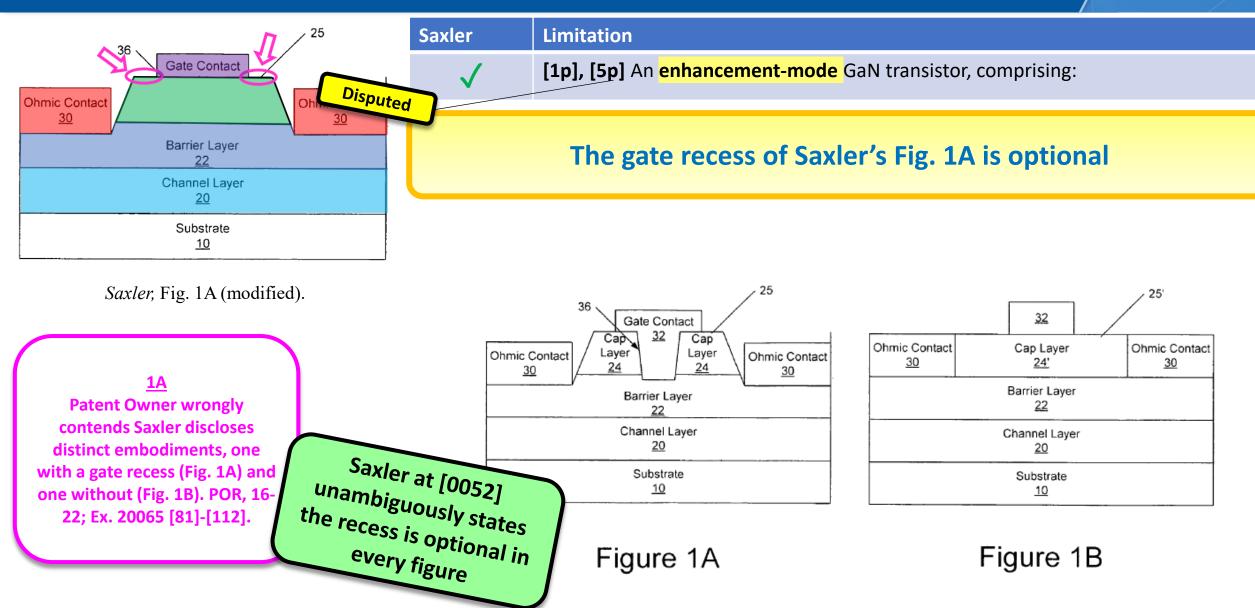

- 1. The gate recess of Saxler's Fig. 1A is optional

- 2. A POSITA would have removed Fig. 1A's recess to achieve the benefits of enhancement mode

'335 Pet., 25-26, 35-36; '335 Reply, 2-11.; '335 Shealy, [090]-[091], [108]-[109], [122]; Ex. 2004, 31:1-20, 37:7-21.

Saxler, Fig. 1A (modified).

Saxler at [0052]

unambiguously

states the recess is

optional in every

figure (may or may

not include)

Limitation

[1p], [5p] An enhancement-mode GaN transistor, comprising:

The gate recess of Saxler's Fig. 1A is optional

[0052] Exemplary devices according to some embodiments of the present invention are schematically illustrated in FIGS. 1A through 6. Thus, while embodiments of the present invention are described herein with reference to a recessed gate structure or a non-recessed gate structure, other embodiments of the present invention may include or not include a gate recess. Accordingly, embodiments of the present invention should not be construed as limited to the particular exemplary embodiments described herein but may include any suitable structure having a cap layer and/or passivation layer as described herein.

B.F. Goodrich Co. v. Aircraft Braking Sys. Corp., 72 F.3d 1577, 1583 (Fed. Cir. 1998) (upholding single-reference obviousness for explicit suggestion to modify); Boston Sci. Scimed, Inc. v. Cordis Corp., 554 F.3d 982, 991 (Fed. Cir. 2009).

'335 Pet., 24-26, 31, 35-36, 40-41; '335 Reply, 2-11.; '335 Shealy, [090]-[091], [108]-[109], [122]; Ex. 2004, 31:1-20, 37:7-21.

Saxler, Fig. 1A (modified).

Petitioner's expert Dr.

Shealy confirms:

Saxler's device is

enhancement mode

when doped p-type

without the recess

| Saxler | Limitation |

|--------|------------|

|--------|------------|

[1p], [5p] An enhancement-mode GaN transistor, comprising:

. A POSITA would have removed Fig. 1A's recess to achieve the benefits of enhancement mode

Further, with the recess, Saxler's device is not enhancement mode (always off), and a POSITA would have been motivated to remove the recess to create an enhancement mode device and realize the benefits of a normally off device, which renders it suitable for high power applications. Suh, 1.

'335 Shealy, [103]

'335 Pet., 25-26, 35-36; '335 Reply, 2-11.; '335 Shealy, [090]-[091], [103], [108]-[109], [122]; Ex. 2004, 31:1-20, 37:7-21.

Saxler, Fig. 1A (modified).

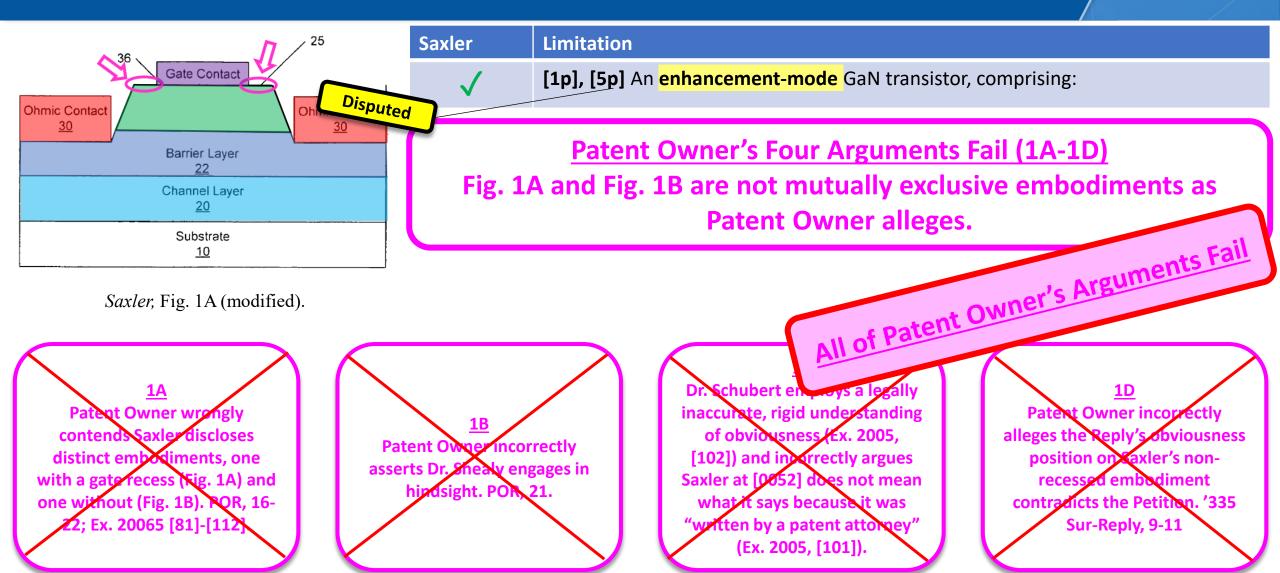

#### 1Δ

Patent Owner wrongly contends Saxler discloses distinct embodiments, one with a gate recess (Fig. 1A) and one without (Fig. 1B). POR, 16-22; Ex. 20065 [81]-[112].

1B

Patent Owner incorrectly

asserts Dr. Shealy engages in

hindsight. POR, 21.

<u>1C</u>

Dr. Schubert employs a legally inaccurate, rigid understanding of obviousness (Ex. 2005, [102]) and incorrectly argues Saxler at [0052] does not mean what it says because it was "written by a patent attorney" (Ex. 2005, [101]).

LD

Patent Owner incorrectly alleges the Reply's obviousness position on Saxler's non-recessed embodiment contradicts the Petition. '335 Sur-Reply, 9-11

'335 POR, 16-22; Reply, 2-11.; '335 Shealy, [090]-[091], [103], [108]-[109], [122]; Ex. 2004, 31:1-20, 37:7-21; '335 Sur-Reply, 9-11.

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE Page 46 of 149

'335 POR, 18-20; '335 Reply, 3-4.

Limitation

| Ohmic Contact  Ohmic Contact                                                                                                                                       |                                                                | ent-mode GaN transistor, comprising:                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Barrier Layer  22  Channel Layer  20                                                                                                                               |                                                                | s of Saxler's Fig. 1A is optional                                                                                                                                                                                                 |

| Substrate<br><u>10</u>                                                                                                                                             | Patent Owner alleges <i>differences</i> between Fig. 1A and 1B | But Saxler discloses similarities                                                                                                                                                                                                 |

| Saxler, Fig. 1A (modified).                                                                                                                                        | Cap layer thickness                                            | ✓ The quoted range overlap (5-20 Å).                                                                                                                                                                                              |

| 1A                                                                                                                                                                 | X Thickness of doped region.                                   | √ The quoted range overlaps (20-50 Å)                                                                                                                                                                                             |

| Patent Owner wrongly contends Saxler discloses distinct embodiments, one with a gate recess (Fig. 1A) and one without (Fig. 1B). POR, 16-22; Ex. 20065 [81]-[112]. | Dopant concentration.                                          | ✓ Patent Owner cites example <i>n-type</i> dopant ranges. <i>Saxler</i> , [0012]. But <i>p-type</i> is used in enhancement mode. <i>P-type</i> ranges are the same for recessed and non-recessed. <i>Saxler</i> , [0013], [0071]. |

| 335 POR, 18-20; '335 Reply, 3-4.                                                                                                                                   | Thickness of increased Al concentration                        | √ The quoted range overlaps (30-100 Å)                                                                                                                                                                                            |

Page 48 of 149 DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE Page 49 of 149

Saxler, Fig. 1A (modified).

# <u>1C</u> Dr. Schubert employs a legally inaccurate, rigid understanding of obviousness (Ex. 2005, [102]) and incorrectly argues Saxler at [0052] does not mean what it says because it was "written by a patent attorney" (Ex. 2005, [101]).

Limitation[1p], [5p] An enhancement-mode GaN transistor, comprising:

The gate recess of Saxler's Fig. 1A is optional

KSR Rejected Dr. Schubert's Rigid Understanding of Obviousness as Limited to "What is Actually Disclosed"

Although  $\P[0052]$  of Saxler says

"embodiments of the present invention should not be construed as limited to the particular exemplary embodiments," it is only reasonable to consider that the disclosure of Saxler must be "limited" to what is actually disclosed. Importantly, ¶[0052] of Saxler does not mention anything about **combining** features of the recessed and the non-recessed embodiments

Ex. 2005, [102]

KSR, 550 U.S. at 418 (obviousness accounts for "inferences and creative steps"), 422 (A POSITA "is also a person of ordinary creativity, not an automaton.").

'335 POR, 17-18; '335 Reply, 5-6; Ex. 2005, 102.

Saxler, Fig. 1A (modified).

### **1C**

Dr. Schubert employs a legally inaccurate, rigid understanding of obviousness (Ex. 2005, [102]) and incorrectly argues Saxler at [0052] does not mean what it says because it was "written by a patent attorney" (Ex. 2005, [101]).

Limitation

[1p], [5p] An enhancement-mode GaN transistor, comprising:

The gate recess of Saxler's Fig. 1A is optional

Dr. Schubert Cannot Ignore Saxler [0052] – Saxler did "actually disclose[]" the non-recessed Fig. 1A

101. ¶52 of Saxler is nothing more than a "catch-all" paragraph written by a patent attorney, commonly used in many patent applications, from my understanding. ¶52 of Saxler does not provide support to POSA to modify ("mix and match") the transistors of Saxler to produce the

particular structure as claimed. Ex. 2005, [101]

[0052] Exemplary devices according to some embodiments of the present invention are schematically illustrated in FIGS. 1A through 6. Thus, while embodiments of the present invention are described herein with reference to a recessed gate structure or a non-recessed gate structure, other embodiments of the present invention may include or not include a gate recess. Accordingly, embodiments of the present invention should not be construed as limited to the particular exemplary embodiments described herein but may include any suitable structure having a cap layer and/or passivation layer as described herein.

'335 POR, 17-18; '335 Reply, 5-6; Ex. 2005, 102.

Saxler, Fig. 1A (modified).

**Patent Owner incorrectly** alleges the Reply's position on Saxler's non-recessed embodiment was obvious contradicts the Petition. '335 Sur-Reply, 9-11

> The petition states Saxler "discloses or at least renders obvious" modified Figure 1A. "'335 Pet., 40-41.

Saxler discloses "a p-type gate material ... having side surfaces" as recited in claim 1. Although it depicts its gate recess may separate its cap layer into two portions in some embodiments, the recess in Saxler's cap layer 24 need not be present and need not extend through the cap layer 24 and into the barrier layer. Saxler, Abstract, [0012]-[0013], [0027], [0052], [0064], [0070]-[0071], [0073], claims 3, 14, 21, 27, 31, 88; Shealy, [122]. Saxler thus discloses or at least renders obvious a single p-type gate material having two side surfaces that extend horizontally towards the source and drain. Shealy, [123].

Abstract, [0012]-[0013], [0027], [0052], [0064], [0070]-[0071], [0073], claims 3, 14, 21, 27, 31, 88. While its figures do not explicitly depict a stacked gate structure having a gate contact and cap layer isolated from the source and drain contacts and without a gate recess, this disclosure would at a minimum render the claimed structure obvious. Shealy, [101]. To the extent Patent Owner disagrees with Saxler's

The petition states Saxler's disclosure of a nonrecessed embodiment "render[s] the claimed structure obvious." '335 Pet., 31.

'335 Pet., 31, 40-41.

Page 52 of 149 52 **DEMONSTRATIVE EXHIBIT – NOT EVIDENCE**

Saxler, Fig. 1A (modified).

# Patent Owner incorrectly alleges the Reply's position on Saxler's non-recessed embodiment was obvious contradicts the Petition. '335 Sur-Reply, 9-11

Limitation

[1p], [5p] An enhancement-mode GaN transistor, comprising:

The gate recess of Saxler's Fig. 1A is optional

The Petition Reasoned a POSITA Would Have Been Motivated to Remove Saxler's Recess to Achieve the Benefits of Enhancement Mode Just Like the Reply

A POSITA would have further been motivated to remove the gate recess to turn Saxler's device into an enhancement mode device, thus realizing the benefits of reduced power consumption and suitability for high power applications. Suh, 1; Shealy, [057]-[063] (citing Beach, Saxler, Ahn, Xu, Sheppard, Smith, Hu, Shenoy),

[103].

The known benefits.

The known benefits of enhancement mode are not disputed.

'335 Pet., 25-26, 35-36; '335 Reply, 2-11.; '335 Shealy, [090]-[091], [103] [108]-[109], [122]; Ex. 2004, 31:1-20, 37:7-21.

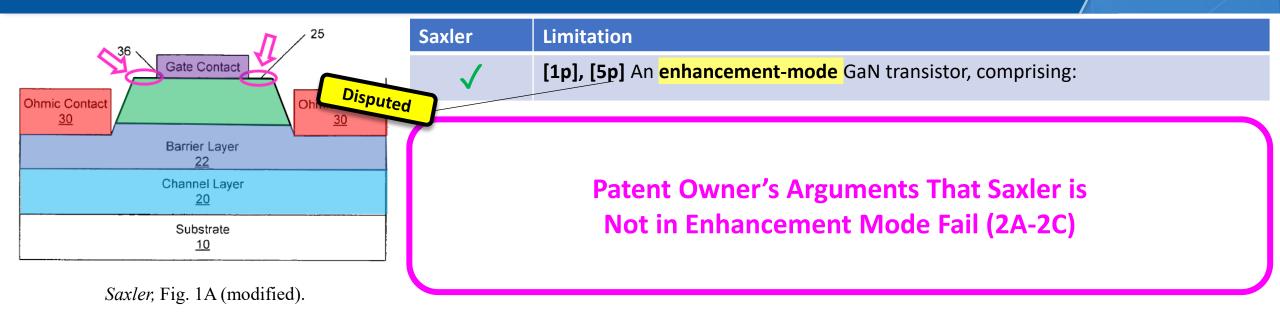

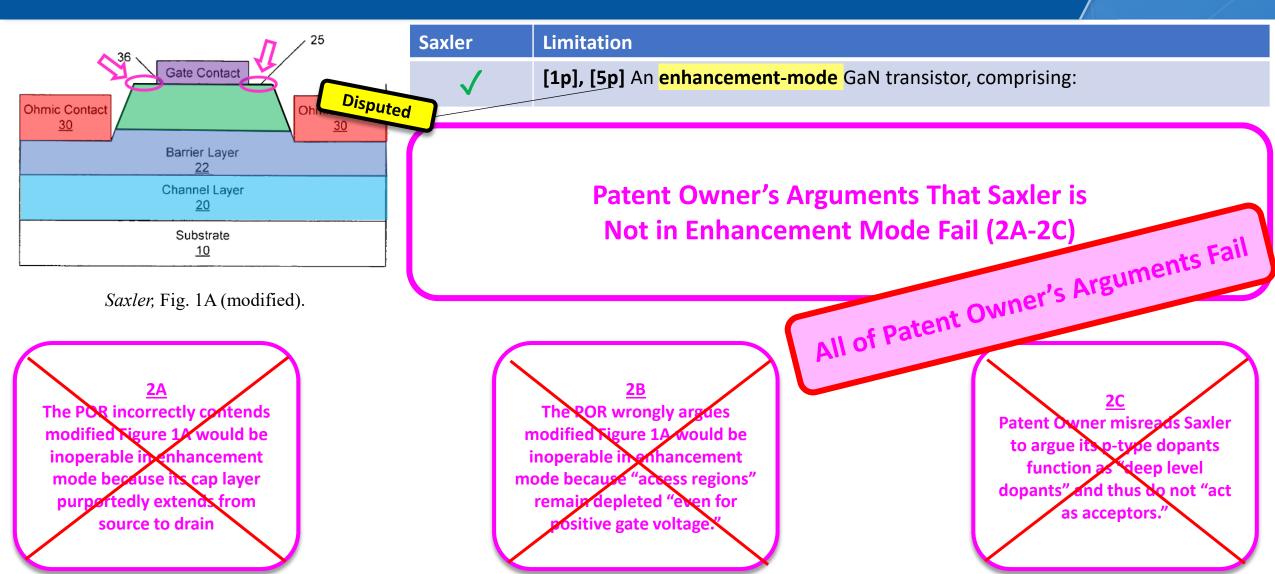

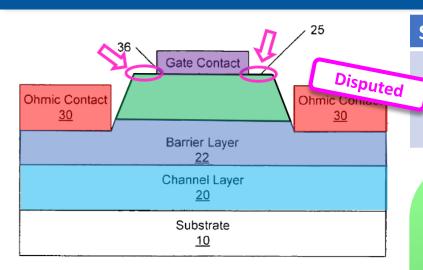

2Δ

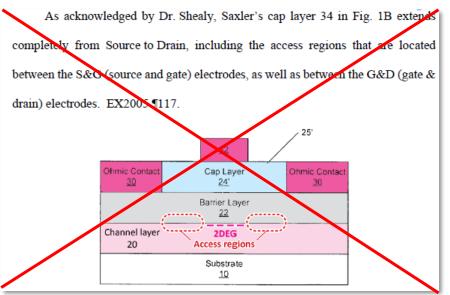

The POR incorrectly contends modified Figure 1A would be inoperable in enhancement mode because its cap layer purportedly extends from source to drain

**2**B

The POR wrongly argues modified Figure 1A would be inoperable in enhancement mode because "access regions" remain depleted "even for positive gate voltage."

Patent Owner misreads Saxler to argue its p-type dopants function as "deep level

dopants" and thus do not "act as acceptors."

Saxler, Fig. 1A (modified).

The POR incorrectly contends

modified Figure 1A would be inoperable in enhancement mode because its cap layer purportedly extends from

oortedly extends fro source to drain The Board noted that the cap layer does not extend from source to drain as Patent Owner alleged to argue the device non-operational. '335

Patent Owner is wrong. The cap layer does not extend from source to drain in modified Figure 1A. The barrier separates the cap layer from source and drain.

'335 POR, 22-26; '335 Reply, 6-7.

Saxler, Fig. 1A (modified).

## **2**A

The POR incorrectly contends modified Figure 1A would be inoperable in enhancement mode because its cap layer purportedly extends from source to drain

Limitation

[1p], [5p] An enhancement-mode GaN transistor, comprising:

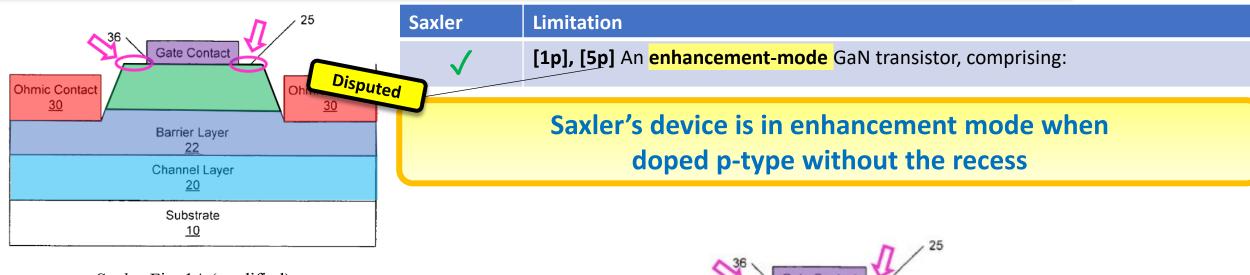

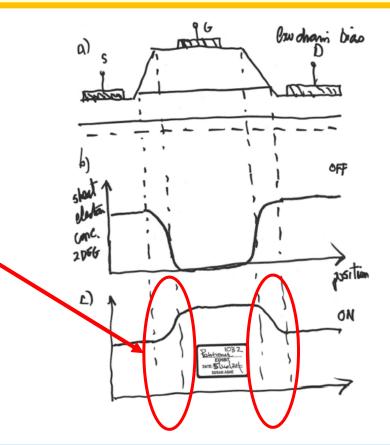

# Saxler's device is in enhancement mode when doped p-type without the recess

'335 POR, 22-26

Patent Owner irrelevantly analyzes Figure 1B, where the cap extends from source to drain. This misunderstands the Petition, which shows removing the recess of Figure 1A would have been obvious.

'335 POR, 22-26; '335 Reply, 7-8.

Patent Owner's "access region" theory contradicts the patent,

which has the same geometry.

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE Page 58 of 149

Saxler, Fig. 1A (modified).

## **2B**

The POR wrongly argues modified Figure 1A would be inoperable in enhancement mode because "access regions" remain depleted "even for positive gate voltage."

Limitation

[1p], [5p] An enhancement-mode GaN transistor, comprising:

Saxler's device is in enhancement mode when doped p-type without the recess

Patent Owner ignored

Dr. Shealy's explanation

describing how Figure

1A is in enhancement

mode, which refutes

Patent Owner's depleted

"access region" theory—

these regions are not

depleted when voltage

is applied.

'335 POR, 25-26; '335 Reply, 9-11; Ex. 1032; Ex. 2004, 104:9-105:19.

Saxler, Fig. 1A (modified).

2C

Patent Owner misreads Saxler to argue its p-type dopants function as "deep level dopants" and thus do not "act as acceptors."

Patent Owner quotes

Saxler at [0049] out of

context to incorrectly

conclude Saxler's p-type

dopants "do not act as

[electron] acceptors"

and cannot deplete the

2DEG, so Saxler's "cap

layer cannot function in

enhancement mode."

Paragraph [0049] explains the purpose of p-type doping of region 40 at the top of the cap layer: "the dopants at the outer surface of the device may segregate to dislocations in the cap layer and, thereby, reduce gate leakage along the dislocations." Id. ¶[0049] Indeed, Saxler points out that the dopants "segregate to dislocations,30 rather than depleting the 2DEG. Id. Paragraph [0049] further explains that "a shallow dopant in the bulk crystal may have characteristics of a deep level when at a dislocation" which is "especially true in the case of p-type [...] dopants." Id. Thus, the shallow acceptors of Saxler do not even act as acceptors once they "segregate to dislocations." EX2005 ¶128. If the shallow dopants do not act as acceptors, the cap layer cannot function in enhancement mode. Id. That is, the dopants that Dr. Shealy envisions as regular, shallow p-type dopants, are in fact characteristics of "deep level" dopants. Id. '335 POR, 24-25

Limitation

[1p], [5p] An enhancement-mode GaN transistor, comprising:

# Saxler's device is in enhancement mode when doped p-type without the recess

Saxler, Fig. 1A (modified).

2C

Patent Owner misreads Saxler

to argue its p-type dopants

function as "deep level

dopants" and thus do not "act

as acceptors."

Saxler at [0049] refers to p-type dopants at crystal "dislocations." There, they act as "deep level dopants" to further reduce leakage.

But p-type dopants act as shallow dopants "in the bulk crystal" and can deplete the 2DEG to function in enhancement mode.

p-type dopants do not function as shallow dopants at *other* locations. *Id. Saxler* never says p-type dopants do not function as shallow dopants at *other* locations. *Id. Saxler* specifically clarifies its "references to p-type ... dopants refer[] to the characteristics of the dopants in the bulk crystal rather than when at a dislocation." *Id.* When Saxler describes p-typed doping in a sub-region or when doped throughout its cap layer (e.g., Saxler, [0013], [0069] [0071]), it describes shallow dopants in the bulk crystal, capable of depleting the 2DEG when the recess is removed. Petition, 25, 35-36; Shealy, [090], [108]

Patent Owner's Sur-Reply does

not refute Saxler's clear

disclosure that its p-type

dopants act as p-type in the

bulk crystal

'335 Reply, 11

- √ [1p], [5p] enhancement mode (Saxler grounds)

- √ [1f] horizontal ledges with substantially equal widths (all grounds)

- ✓ [2], [5f] self aligned horizontal ledges (all grounds)

- ✓ Motivation to modify Saxler

- ✓ Saxler's modified Fig. 1A is in enhancement mode.

- ✓ A POSITA would have modified Fig. 1A based on Saxler's teachings and for the benefits of enhancement mode.

- √ [1p], [5p] enhancement mode (Saxler grounds)

- √ [1f] horizontal ledges with substantially equal widths (all grounds)

- √ [2], [5f] self aligned horizontal ledges (all grounds)

- ✓ Motivation to modify Saxler

- √ [1p], [5p] enhancement mode (Saxler grounds)

- √ [1f] horizontal ledges with substantially equal widths (all grounds)

- ✓ [2], [5f] self aligned horizontal ledges (all grounds)

- ✓ Motivation to modify Saxler

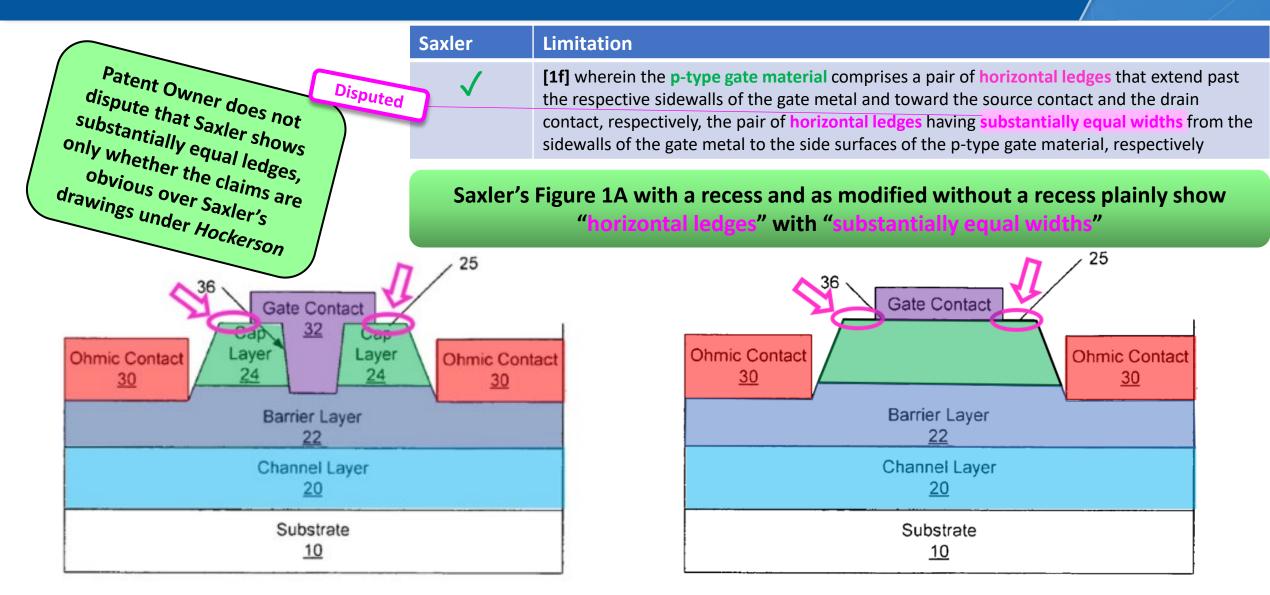

✓ Saxler's drawings disclose ledges with substantially equal widths

Saxler, Fig. 1A (modified).

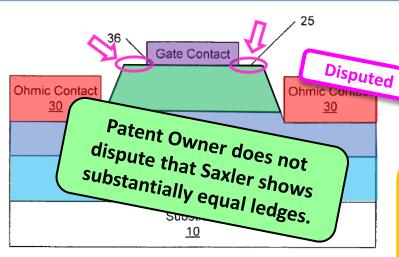

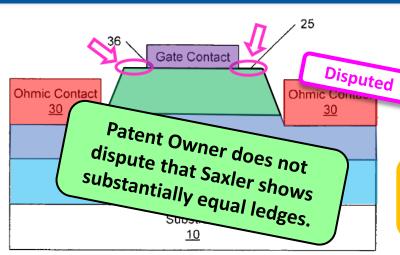

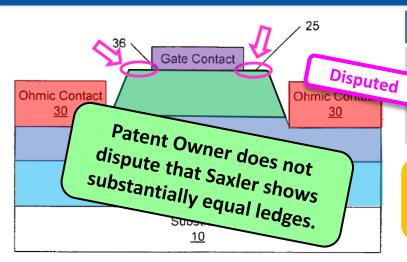

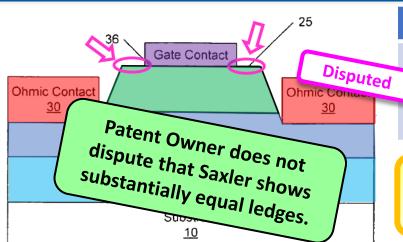

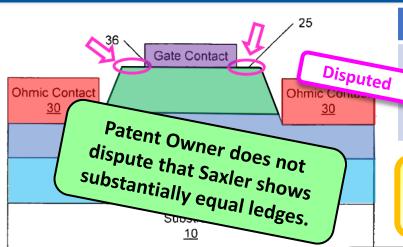

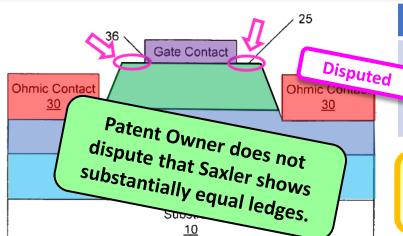

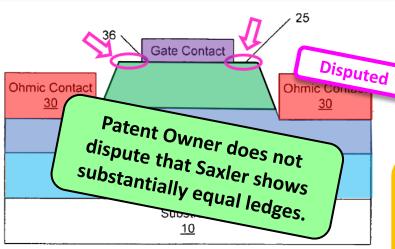

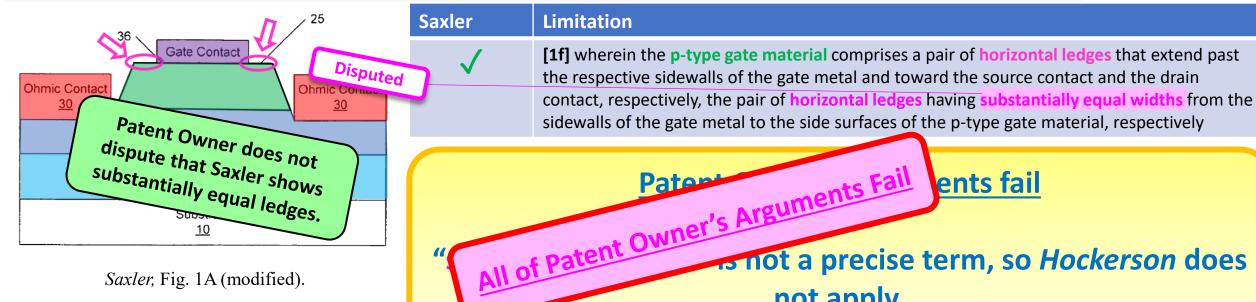

Patent Owner does not dispute that Saxler shows substantially equal ledges, only that the claims cannot be obvious over Saxler's drawings under legal precedent (Hockerson)

| Saxler   |  | Limitation                                                                                                                                                                                 |

|----------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>√</b> |  | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain        |

|          |  | contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively |

- ✓ Saxler's drawings disclose ledges with "substantially equal widths"

- 1. Saxler's Figure 1A with a recess and as modified without a recess plainly show "horizontal ledges" with "substantially equal widths" [undisputed]

- 2. "substantially equal" is not a precise term, so *Hockerson* does not apply.

At Institution, the Board reasoned "substantially' is a common approximation or term of degree in patent claims," which Patent Owner did not dispute, so *Hockerson* does not apply, and drawings can disclose this limitation. '335 ID, 38-39.

'335 Pet., 49-51.

Saxler, Fig. 1A.

Saxler, Fig. 1A (modified).

Saxler, Fig. 1A (modified).

| Saxler   | Limitation                                                                                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>√</b> | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain        |

| _        | contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively |

## Patent Owner's arguments fail

"substantially equal" is not a precise term, so *Hockerson* does not apply.

#### Δ

Patent Owner incorrectly argues Saxler's figures cannot disclose "substantially equal widths" under *Hockerson*

### <u>B</u>

Patent Owner misunderstands Ex Parte Bjorn to inaccurately contend "substantially equal" cannot be disclosed by figures (

Patent Owner relies on Saxler's optional "offset" between the gate and source/drain to inaccurately contend Saxler does not disclose "substantially equal" ledges"

'335 Pet., 49-51; '335 POR, 29-38; '335 Reply, 14-19.

| S | axler    | Limitation                                                                                                                                                                                 |

|---|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | <b>✓</b> | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain        |

| _ |          | contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively |

"substantially equal" is not a precise term, so Hockerson does not apply.

Saxler, Fig. 1A (modified).

A

Patent Owner incorrectly

argues Saxler's figures cannot

disclose "substantially equal

widths" under Hockerson

Hockerson holds that drawings not to scale cannot disclose precise proportions or dimensions. Hockerson-Halberstadt, Inc. v. Avia Grp. Int'l, Inc., 222 F.3d 951, 956 (Fed. Cir. 2000).

At Institution, the Board reasoned

"substantially' is a common

approximation or term of degree in

patent claims," which Patent Owner did

not dispute, so Hockerson does not

apply, and drawings can disclose this

limitation. '335 ID, 38-39.

'335 Pet., 49-51; '335 POR, 32; '335 Reply, 15.

Saxler, Fig. 1A (modified).

A

Patent Owner incorrectly

argues Saxler's figures cannot

disclose "substantially equal

widths" under Hockerson

| Saxler |          | Limitation                                                                                                                                                                                 |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | <b>√</b> | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain        |

| J      |          | contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively |

"substantially equal" is not a precise term, so Hockerson does not apply.

Hockerson does not extend to relative proportions, terms of degree, and approximation. Paper No. 8 at 2. Petitioners showed "substantially equal" is an approximation or term of degree, which the POR does not dispute. Id. at 4 (citing Seattle Box Co., Inc. v. Indus. Crating & Packing, Inc., 731 F.2d 818, 826 (Fed. Cir. 1984); M.P.E.P. § 2173.05(b)(II)(D)); POR, 31-35 (no discussion of Seattle Box or M.P.E.P.). Hockerson does not apply.

'335 Reply, 15

At Institution, the Board reasoned that "substantially' is a common approximation or term of degree in patent claims," which Patent Owner did apply, and drawings can disclose this limitation. '335 ID, 38-39.

'335 Pet., 49-51; '335 POR, 29-36; '335 Reply, 15-19.

| Saxler |          | Limitation                                                                                                                                                                          |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| )      | <b>√</b> | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain |

|        |          | contact, respectively, the pair of horizontal ledges having substantially equal widths from the                                                                                     |

|        |          | sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively                                                                                          |

"substantially equal" is not a precise term, so Hockerson does not apply.

Saxler, Fig. 1A (modified).

В

Patent Owner misunderstands Ex Parte Bjorn to inaccurately contend "substantially equal" cannot be disclosed by figures Patent Owner misunderstands Ex Parte Bjorn's discussion of "less than or substantially equal" to contend it focuses on the open ended "less than ... equal" requirement

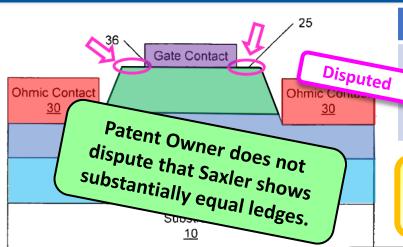

In Ex parte Bjorn, the Board first addressed the limitation "less than or substantially equal" of independent claim 1 that was directed to a bone implant. Id. at \*10 (emphasis added). The Board found that "claim 1 merely requires the abutment to have an exterior surface diameter that is 'less than or substantially equal to the maximum thread diameter of the male screw section of the bone fixture.' No particular dimensions or proportions are claimed." Id. The limitation of "less than or substantially equal" was thus found to be open-ended. Id. (emphasis added).

**Ex Parte Bjorn does not support Patent Owner**

'335 POR, 32

'335 Pet., 49-51; '335 POR, 29-36; '335 Reply, 15-19.

| Saxier |          | Limitation                                                                                                                                                                                 |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <b>√</b> | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain        |

| _      |          | contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively |

"substantially equal" is not a precise term, so Hockerson does not apply.

Saxler, Fig. 1A (modified).

В

Patent Owner misunderstands Ex Parte Bjorn to inaccurately contend "substantially equal" cannot be disclosed by figures repeatedly found prior art drawings not to scale showed screws with "substantially equal" diameters without mention of the "less than ... equal" requirement.

Parte Bjorn, 2019 WL 6173305 at \*1. Ex Parte Bjorn first found Hockerson did not apply because "no particular dimensions" were claimed. Id. at \*10-11. The Board then found numerous prior art figures not to scale from different references disclosed "substantially equal" diameters. E.g., id. at \*11 (e.g., noting certain figures show "diameters substantially equal" and still others "clearly show ... substantially equal" diameters), 17 (certain figure "clearly illustrates ... substantially equal" diameters). Here, the Board did not find the prior art showed "less than ... equal" diameters—the prior art showed "substantially equal" diameters. Id.

**Ex Parte Bjorn supports Petitioner**

'335 Reply, 16

'335 Pet., 49-51; '335 POR, 29-36; '335 Reply, 15-19.

Saxler

| limitation   | Limitation                              |

|--------------|-----------------------------------------|

| Lillillation | LIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII |

[1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively

"substantially equal" is not a precise term, so Hockerson does not apply.

Saxler, Fig. 1A (modified).

<u>B</u>

Patent Owner misunderstands Ex Parte Bjorn to inaccurately contend "substantially equal" cannot be disclosed by figures Ex Parte Bjorn

repeatedly found prior

art drawings not to

scale showed screws

with "substantially

equal" diameters

without mention of the

"less than ... equal"

requirement.

'335 Pet., 49-51; '335 POR, 29-36; '335 Reply, 15-19.

## '335 Patent Ground 1: Saxler renders obvious claims 1-7

| Saxier | Limitation                                                                                                                                                                                 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ✓      | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain        |

|        | contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively |

"substantially equal" is not a precise term, so Hockerson does not apply.

Saxler, Fig. 1A (modified).

В

Patent Owner misunderstands Ex Parte Bjorn to inaccurately contend "substantially equal" cannot be disclosed by figures Patent Owner focuses on analysis of a figure showing a larger diameter screw, where Hockerson applied. POR, 32; Ex Parte Bjorn at \*17. But when the prior art showed "substantially equal" diameters, the Board found the limitation obvious.

The issue is whether Lazzara's abutment portion, which is *larger* in diameter than the maximum diameter of the bone fixture screw threads in Figure 9, can be considered "substantially equal to the maximum thread diameter of the male screw section of the bone fixture" as recited in claim 8.

• • •

However, even if we determine what percentage or ratio of an oversized abutment diameter is permitted within the scope of the claim, the drawings cannot be relied on to disclose such precise or relative proportions. *See Hockerson-Halberstadt*, 222 F.3d at 956. The Specification indicates that "substantially equal" requires abutment diameter D1 to be very nearly equal to maximum thread diameter D2. **We cannot make that determination from Figure 9 of Lazzara, which illustrates the abutment diameter as larger than the maximum thread diameter**, but Figure 9 is not disclosed as being to scale or having any particular dimensions. Thus, we do not sustain the rejection of claim 8 or claim 10, which depends from claim 8.

'335 Pet., 49-51; '335 POR, 29-36; '335 Reply, 15-19.

Ex Parte Bjorn, 2019 WL 6173305 at \*17.

| Saxler   | Limitation                                                                                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>√</b> | [1f] wherein the p-type gate material comprises a pair of horizontal ledges that extend past the respective sidewalls of the gate metal and toward the source contact and the drain        |

| ,        | contact, respectively, the pair of horizontal ledges having substantially equal widths from the sidewalls of the gate metal to the side surfaces of the p-type gate material, respectively |

Saxler's optional "offset" between gate and source/drain does not contradict Figure 1A's centered gate with ledges of substantially equal width

C

Patent Owner relies on Saxler's optional "offset" between the gate and source/drain to inaccurately contend Saxler does not disclose "substantially equal" ledges"

The POR cites Saxler [0065], which uses non-limiting language ("the recess *may* be offset") to describe an optional feature, which means other embodiments—like Figure 1A—would not have an offset. '335 POR, 37-38.

Further, Saxler [0065] does not describe the relationship between the gate electrode and cap layer which defines the widths of the claimed ledges. It describes the spatial relationship between the gate and source/drain. Saxler, [0065].

'335 POR, 37-38; '335 Reply, 18-19.

## '335 Patent Ground 1: Saxler renders obvious claims 1-7

s not a precise term, so *Hockerson* does

not apply.

ents fail

Patent Owner incorrectly argues Saxler rigures cannot disclose "substantially equal s" under Hockerson

**Patent Owner misanderstands** Ex Parte Bjorn o inaccurately contend "substantially equal" cannot be disclosed by figures Patent Owner relies on Saxler's optional "offset" between the gate and so wee/drain to inaccurately contend Saxler stantially equal" leases

'335 Pet., 49-50; '335 POR, 29-38; '335 Reply, 15-19.

## '335 Patent Ground 1: Saxler renders obvious claims 1-7

| axler    | Limitation                                                                                                                                          |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

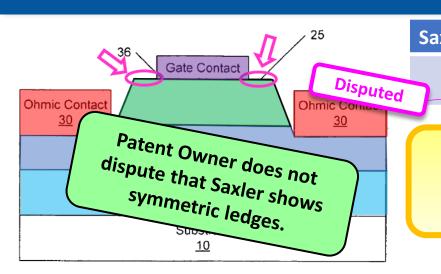

| <b>✓</b> | [7] The enhancement mode GaN transistor according to claim 5, wherein the pair of self-aligned ledges are symmetric with respect to the gate metal. |

For the same reasons, *Hockerson* does not apply to claim 7's "symmetric" ledges

Saxler, Fig. 1A (modified).

At Institution, the Board invited the parties to brief whether *Hockerson* applies to claim 7's "symmetric" ledges.

Petitioners Briefed this issue. But Patent Owner did not and thus forfeited any response. *See* '335 POR; '335 Sur-Reply.

Petitioners' undisputed position shows the patent equates "substantially equal" and "symmetric." Hockerson does not apply to "symmetric" for the same reasons as for "substantially equal."

ledges 500 on each side of the gate metal 504. The pair of ledges 506 that extend past sidewalls of the gate metal 504 have equal or substantially equal widths, i.e., the respective ledges are symmetric from the respective sidewalls of the gate metal to the side surfaces of the p-type gate material, which is due to the self-aligned manufacturing process.

'335 patent, 3:59-64.

'335 ID, 38; '335 Reply, 17-18.

Patent Owner only disputes the Saxler combinations of prior art shows *three* features for claims 1-7 of the '335 patent and the motivations to combine the references

- √ [1p], [5p] enhancement mode (Saxler grounds)

- √ [1f] horizontal ledges with substantially equal widths (all grounds)

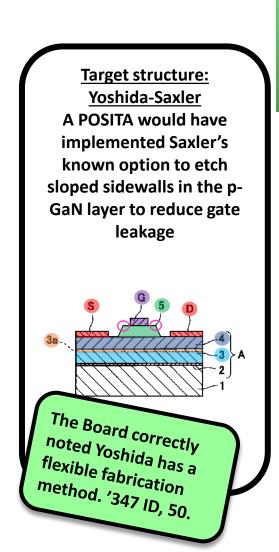

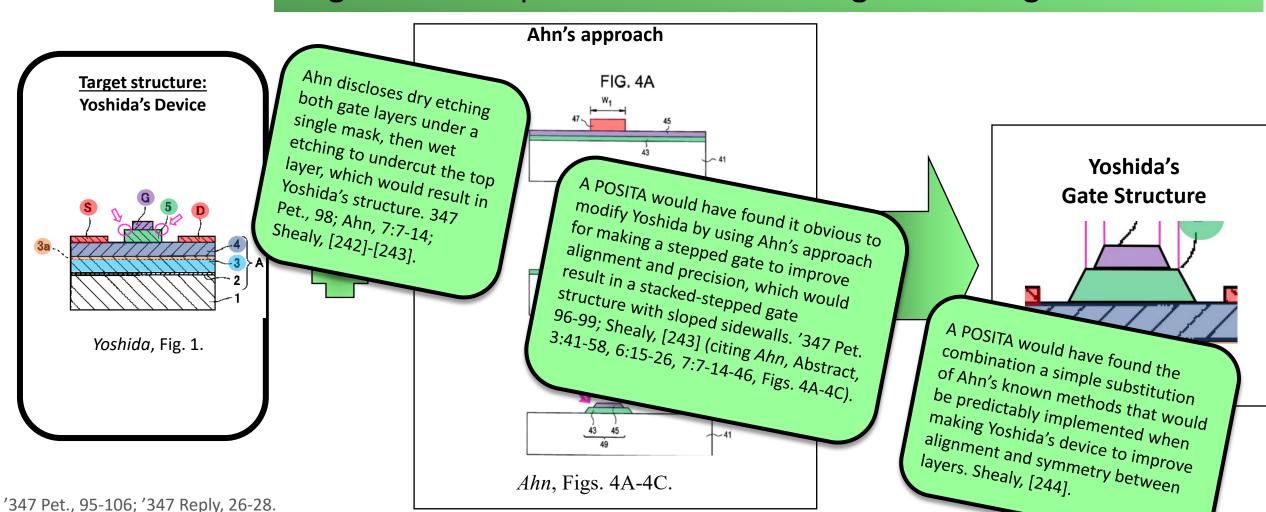

- √ [2], [5f] self aligned horizontal ledges (all grounds).