#### Before the Honorable Clark S. Cheney Chief Administrative Law Judge

In the Matter of

CERTAIN SEMICONDUCTOR DEVICES, AND METHODS OF MANUFACTURING SAME AND PRODUCTS CONTAINING THE SAME **Investigation No. 337-TA-1366**

**RESPONDENTS' POST-HEARING INITIAL BRIEF**

## TABLE OF CONTENTS

| 1.  |      |       | N VIEW OF PRIOR ART                                                                                                                                                              | 1  |

|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | A.   | The ' | 294 Patent Is Invalid in View of Prior Art                                                                                                                                       | 1  |

|     |      | 1.    | All Elements of the '294 Patent Are Admitted Prior Art Except "Compensated GaN Layer," Which Was Well Known in the Art                                                           | 1  |

|     |      | 2.    | EPC's Expert Agrees "Compensated GaN" Is Found in Prior Art                                                                                                                      | 4  |

|     | B.   | The ' | 508 Patent Is Also Invalid in View of Prior Art                                                                                                                                  | 6  |

|     |      | 1.    | All Elements of the '508 Patent Were Known in the Art                                                                                                                            | 6  |

|     |      | 2.    | EPC's Expert Agrees All Elements of Asserted Claim 1 Are Found in Prior Art                                                                                                      | 8  |

|     | C.   | Proce | edural History of the Investigation                                                                                                                                              | 9  |

|     | D.   | The I | Private Parties                                                                                                                                                                  | 10 |

|     |      | 1.    | Respondents                                                                                                                                                                      | 10 |

|     |      | 2.    | Complainant                                                                                                                                                                      | 10 |

|     | E.   | The I | Patents-at-Issue                                                                                                                                                                 | 10 |

|     |      | 1.    | Overview of the '294 Patent: All Elements Are <i>Admitted</i> as Prior Art, Except "Compensated GaN"                                                                             | 10 |

|     |      | 2.    | Overview of the '508 Patent: The Device Itself Is Admitted Prior Art, While the "Present Invention" Is About the Process of Self-Aligning the Gate Metal and Doped GaN Materials | 15 |

| II. | U.S. | PATEN | IT NO. 8,350,294                                                                                                                                                                 | 19 |

|     | A.   |       | n Construction for the '294 Patent: Compensated GaN Is at Least conductive or Semi-Insulating                                                                                    | 19 |

|     | В.   |       | idity of the '294 Patent: Both Grounds Invalidate All Three Asserted                                                                                                             | 20 |

|     |      | 1.    | Priority Date                                                                                                                                                                    | 20 |

|     |      | 2.    | Level of Ordinary Skill                                                                                                                                                          | 20 |

| 3. | Overv | riew of | the Prior Art                                                                                                                                 | 20 |

|----|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | a.    | Uemo    | to (US2008/0087915A1, RX-0073)                                                                                                                | 21 |

|    | b.    | Beach   | a189 (US2006/0145189A1, RX-0011)                                                                                                              | 22 |

|    | c.    | Kigan   | ni (JP2006253224A, RX-0079)                                                                                                                   | 23 |

| 4. | Uemo  | to Grou | and: Uemoto Renders Claims 1-3 Obvious                                                                                                        | 24 |

|    | a.    | [1pre]  | : A column III Nitride transistor                                                                                                             | 24 |

|    | b.    | [1a]: a | a substrate                                                                                                                                   | 25 |

|    | c.    | [1b]: a | a set of III-N transition layers above the substrate                                                                                          | 25 |

|    | d.    | [1c]: a | a III-N buffer layer above the set of transition layers                                                                                       | 26 |

|    | e.    | [1d]: a | a III-N barrier layer above the buffer layer                                                                                                  | 27 |

|    | f.    | comp    | t Opinions Regarding Disputed Elements: [1e]: a ensated GaN layer above the barrier layer and [1f]: a contact above the compensated GaN layer | 27 |

|    |       | i.      | Structural Component: "compensated GaN layer"                                                                                                 | 27 |

|    |       | ii.     | Structural Component: "gate contact"                                                                                                          | 28 |

|    |       | iii.    | Positional Component: compensated GaN layer "above the barrier layer"; and gate contact "above the compensated GaN layer"                     | 28 |

|    | g.    | [2p]: ' | The transistor of claim 1                                                                                                                     | 31 |

|    | h.    |         | wherein the compensated GaN layer contains acceptor lopant atoms passivated with hydrogen                                                     |    |

|    | i.    | [3p]: ' | The transistor of claim 2                                                                                                                     | 31 |

|    | j.    |         | where the acceptor type atoms are selected from the consisting of Mg, Zn, Be and Ca                                                           | 32 |

| 5. |       |         | ound: Beach189 Anticipates Claim 1, and Beach189 igami Renders Claims 2 and 3 Obvious                                                         | 32 |

|    | a.    | Claim   | 1 is anticipated by Beach189                                                                                                                  | 32 |

|    |       | i       | [1pre]: A column III Nitride transistor                                                                                                       | 32 |

|    |       | ii.       | [1a]: a substrate                                                                                                                                                                                                                    | 33 |

|----|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    |       | iii.      | [1b]: a set of III-N transition layers above the substrate                                                                                                                                                                           | 33 |

|    |       | iv.       | [1c]: a III-N buffer layer above the set of transition layers                                                                                                                                                                        | 34 |

|    |       | v.        | [1d]: a III-N barrier layer above the buffer layer                                                                                                                                                                                   | 35 |

|    |       | vi.       | [1e]: a compensated GaN layer above the barrier layer                                                                                                                                                                                | 35 |

|    |       | vii.      | [1f]: a gate contact above the compensated GaN layer                                                                                                                                                                                 | 36 |

|    |       | viii.     | Expert Opinions: EPC's arguments are meritless                                                                                                                                                                                       | 37 |

|    | b.    |           | s 2 and 3 are rendered obvious by <i>Beach189</i> and <i>i</i>                                                                                                                                                                       | 42 |

|    |       | i.        | Motivation to Combine for Claims 2 and 3: A POSITA would have been motivated to form <i>Beach189</i> 's compensated GaN using <i>Kigami</i> 's process for doping the GaN with magnesium and passivating the magnesium with hydrogen | 42 |

|    |       | ii.       | Expert Opinions Regarding Claims 2 and 3: EPC argument against the motivation to combine fails as EPC misinterprets the claims and the prior art references                                                                          | 44 |

|    |       | iii.      | [2p]: The transistor of claim 1,                                                                                                                                                                                                     | 46 |

|    |       | iv.       | [2a]: wherein the compensated GaN layer contains acceptor type dopant atoms passivated with hydrogen                                                                                                                                 | 46 |

|    |       | v.        | [3p]: The transistor of claim 2                                                                                                                                                                                                      | 48 |

|    |       | vi.       | [3a]: where the acceptor type atoms are selected from the group consisting of Mg, Zn, Be and Ca                                                                                                                                      | 49 |

| 6. | EPC F | ails to S | Show Secondary Considerations                                                                                                                                                                                                        | 50 |

|    | a.    |           | 1: Secondary considerations irrelevant as Claim 1 is lover a single reference                                                                                                                                                        | 50 |

|      |      |       | b.       |          | ns 2 and 3: EPC fails to tie secondary considerations to a elements                                                      | 51 |

|------|------|-------|----------|----------|--------------------------------------------------------------------------------------------------------------------------|----|

|      |      |       |          | i.       | Alleged Nexus                                                                                                            | 51 |

|      |      |       |          | ii.      | Alleged Failure of Others and Long Felt Need                                                                             | 52 |

| III. | U.S. | PATEN | IT NO.   | 8,404,5  | 08                                                                                                                       | 54 |

|      | A.   | Clain | n Const  | truction | for the '508 Patent: Not at Issue for Invalidity                                                                         | 54 |

|      | B.   | Inval | idity of | the '50  | 8 Patent                                                                                                                 | 55 |

|      |      | 1.    | Prior    | ity Date | ÷                                                                                                                        | 55 |

|      |      | 2.    | Leve     | l of Ord | linary Skill                                                                                                             | 55 |

|      |      | 3.    | Over     | view of  | the Prior Art                                                                                                            | 55 |

|      |      |       | a.       | Hikit    | a (U.S. Patent Appl. Pub. No. 2006/0273347)                                                                              | 56 |

|      |      |       | b.       | Shep     | pard (U.S. Patent No. 7,238,560)                                                                                         | 60 |

|      |      |       | c.       |          | h624 (International Patent Appl. Pub. No. WO /057624)                                                                    | 61 |

|      |      | 4.    |          |          | nd Invalidates Claim 1: <i>Hikita</i> in View of <i>Sheppard</i> 24 Renders Claim 1 Obvious                              | 64 |

|      |      |       | a.       |          | OSITA would have been motivated to form <i>Sheppard</i> 's ple transition layers in <i>Hikita</i> 's transistor          | 64 |

|      |      |       | b.       |          | OSITA would have been motivated to use <i>Beach624</i> 's esses for forming the gate and ohmic contacts in <i>Hikita</i> | 65 |

|      |      |       |          | i.       | Elements [1e] through [1i] – Gate Formation                                                                              | 65 |

|      |      |       |          | ii.      | Elements [1e] through [1i] – Self-Aligned Process                                                                        | 68 |

|      |      |       |          | iii.     | Elements [1n] through [1r] – Ohmic Formation                                                                             | 70 |

|      |      |       | c.       | - 1      | e]: A method of forming an enhancement mode GaN istor                                                                    | 72 |

|      |      |       | d.       | [1a]:    | nucleating and growing transition layers on a substrate                                                                  | 72 |

|      |      |       | e.       | [1b]:    | growing an III Nitride EPI layer over the transistor                                                                     | 7/ |

|    | f.    | [1c]: g            | rowing an III Nitride barrier layer over the EPI layer                                                                                                                                                        | 75 |

|----|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | g.    |                    | rowing a GaN layer with acceptor type dopants over rier layer                                                                                                                                                 | 76 |

|    | h.    | [1e] th            | rough [1i]:                                                                                                                                                                                                   | 77 |

|    | i.    | applyin<br>dielect | rough [1m]: [1j] depositing a dielectric layer; [1k] ng a contact photo resistant pattern; [1l] etching the ric layer to open the drain and source contact area; emoving the contact photo resistant pattern; | 81 |

|    | j.    | [1o] ap            | rough [1q]: [1n] depositing an Ohmic contact metal; oplying a metal photo resistant pattern; [1p] etching mic contact metal; [1q] removing the metal photo nt pattern; and                                    | 82 |

|    | k.    |                    | erforming rapid thermal annealing to form Ohmic nd source contacts                                                                                                                                            | 84 |

|    | 1.    | analys             | Opinions: EPC fails to rebut Dr. Lebby's invalidity is as EPC misinterpret the claims, the prior art, and sposed combination                                                                                  | 85 |

|    |       | i.                 | Beach624 discloses or at least suggests both a "gate photo resistant pattern" and a "metal photo resistant pattern"                                                                                           | 85 |

|    |       | ii.                | The claim does not require a gate-first process                                                                                                                                                               | 86 |

|    |       | iii.               | Even if Hikita suggests using a liftoff technique, it would have been obvious to instead implement <i>Beach624</i> 's etching technique                                                                       | 87 |

|    |       | iv.                | Beach624 is an enhancement mode device contrary to Dr. Schubert's assertion, but that is irrelevant to the proposed combination                                                                               | 88 |

|    |       | v.                 | When combined as Dr. Lebby proposed, the combination of <i>Hikita</i> and <i>Beach624</i> is functional—the dielectric is deposited after the gate metal                                                      | 89 |

| 5. | EPC F | ails to S          | Show Secondary Considerations                                                                                                                                                                                 | 91 |

|    | a.    | Allege             | d Nexus                                                                                                                                                                                                       | 91 |

|    | b.    | Allege             | d Failure of Others and Long Felt Need                                                                                                                                                                        | 92 |

|     | c. Alleged Praise                                         | 92 |

|-----|-----------------------------------------------------------|----|

|     |                                                           |    |

| IV. | CONCLUSION: THE ASSERTED PATENTS ARE INVALID AND THERE IS |    |

|     | NO VIOLATION                                              | 93 |

## **TABLE OF AUTHORITIES**

| Page(s                                                                                                                                    | <b>i)</b> |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Federal Cases                                                                                                                             |           |

| Acco Brands Corp. v. Fellowes, Inc.,<br>813 F.3d 1361 (Fed. Cir. 2016)                                                                    | 8         |

| Allergan, Inc. v. Sandoz Inc.,<br>818 F. Supp. 2d 974 (E.D. Tex. 2011)5                                                                   | 0         |

| Cohesive Technologies, Inc. v. Waters Corp., 543 F.3d 1351 (Fed. Cir. 2008)                                                               | 0         |

| EMI Grp. N. Am., Inc. v. Cypress Semiconductor Corp., 68 F. Supp. 2d 421 (D. Del. 1999)2                                                  | 9         |

| Fox Factory, Inc. v. SRAM, LLC,<br>944 F.3d 1366 (Fed. Cir. 2019)                                                                         | 1         |

| Geo. M. Martin Co. v. All. Mach. Sys. Int'l LLC,<br>618 F.3d 1294 (Fed. Cir. 2010)                                                        | 0         |

| Infection Prevention Techs., LLC v. Lumalier Corp., Case No. 10-cv-12371, 2012 WL 3248232 (E.D. Mich. Aug. 8, 2012)3                      | 0         |

| Intel Corp. v. Qualcomm Inc.,<br>21 F.4th 784 (Fed. Cir. 2021)                                                                            | 8         |

| Intercontinental Great Brands LLC v. Kellogg N. Am. Co.,<br>118 F. Supp. 3d 1022 (N.D. Ill. 2015), aff'd, 869 F.3d 1336 (Fed. Cir. 2017)4 | 5         |

| <i>Iron Grip Barbell Co. v. USA Sports, Inc.</i> , 392 F.3d 1317 (Fed. Cir. 2004)5                                                        | 3         |

| <i>In re Keller</i> , 642 F.2d 413 (C.C.P.A. 1981)88, 8                                                                                   | 9         |

| KSR Int'l Co. v. Teleflex Inc.,<br>550 U.S. 398 (2007)88, 8                                                                               | 9         |

| Marrin v. Griffin, 599 F.3d 1290 (Fed. Cir. 2010)                                                                                         |           |

| Metso Mins., Inc. v. Powerscreen Int'l Distribution, Ltd., 526 F. App'x 988 (Fed. Cir. 2013)                                              |           |

| Mformation Technologies, Inc. v. Research in Motion Ltd., 764 F.3d 1392 (Fed. Cir. 2014)8            | 36 |

|------------------------------------------------------------------------------------------------------|----|

| Nike, Inc. v. Adidas AG, 955 F.3d 45 (Fed. Cir. 2020)5                                               | 52 |

| Novartis Pharms. Corp. v. West-Ward Pharms. Int'l Ltd., 923 F.3d 1051 (Fed. Cir. 2019)8              | 88 |

| Schwendimann v. Neenah, Inc.,         82 F.4th 1371 (Fed. Cir. 2023)                                 | 4  |

| Terlep v. Brinkman Corp., Case No. 02-cv-5127, 2004 U.S. Dist. LEXIS 28453 (W.D. Ark. Mar. 23, 2004) | 29 |

| Trustees of Columbia Univ. in City of New York v. Illumina, Inc., 620 F. App'x 916 (Fed. Cir. 2015)  | 51 |

| ZUP, LLC v. Nash Mfg., Inc.,<br>896 F.3d 1365 (Fed. Cir. 2018)5                                      | 0  |

| Federal Statutes                                                                                     |    |

| Pre-AIA 35 U.S.C. § 102                                                                              | m  |

| Pre-AIA 35 U.S.C. § 103                                                                              | 55 |

| Ground Rules                                                                                         |    |

| Rule 14.15                                                                                           | 0  |

### TABLE OF ABBREVIATIONS

| Abbr.      | Full description                                              |

|------------|---------------------------------------------------------------|

| HEMT       | high electron mobility transistor                             |

| 2DEG       | two-dimensional electron gas                                  |

| GaN        | gallium nitride                                               |

| Si         | silicon                                                       |

| Mg         | magnesium                                                     |

| AlGaN      | aluminum gallium nitride                                      |

| MOCVD      | metal-organic chemical vapor deposition                       |

| Н          | hydrogen                                                      |

| V          | volt                                                          |

| MOSFET     | metal-oxide-semiconductor field-effect transistor             |

| N          | nitride                                                       |

| Tr         | Transcript of Evidentiary Hearing, February 26-March 1, 2024  |

| Markman Tr | Transcript of Markman Hearing and Case Management Conference, |

|            | October 13, 2023                                              |

## TABLE OF FREQUENTLY CITED EXHIBITS

| Ex. No. | Full description                                                           |

|---------|----------------------------------------------------------------------------|

| JX-0014 | U.S. Patent No. 8,350,294                                                  |

| JX-0015 | U.S. Patent No. 8,404,508                                                  |

| RX-0073 | U.S. Patent Application Publication No. 2008/0087915A1 to Uemoto et al.    |

|         | ("Uemoto")                                                                 |

| RX-0011 | U.S. Patent Application Publication No. 2006/0145189A1 to Beach            |

|         | ("Beach189")                                                               |

| RX-0079 | Japanese Patent Application Publication No. JP2006253224A to Kigami et al. |

|         | ("Kigami")                                                                 |

| RX-0041 | U.S. Patent Application Publication No. 2006/0273347 to Hikita et al.      |

|         | ("Hikita")                                                                 |

| RX-0288 | U.S. Patent No. 7,238,560 to Sheppard et al. ("Sheppard")                  |

| RX-0286 | International Patent Application Publication No. WO 2005/057624 to Beach   |

|         | ("Beach624")                                                               |

## AGREED UPON NOMENCLATURE FOR '508 CLAIM 11

| Claim  | Limitation                                                              |  |  |

|--------|-------------------------------------------------------------------------|--|--|

| [1pre] | A method of forming an enhancement mode GaN transistor, the             |  |  |

|        | method comprising:                                                      |  |  |

| [1a]   | nucleating and growing transition layers on a substrate;                |  |  |

| [1b]   | growing an III Nitride EPI layer over the transistor layers;            |  |  |

| [1c]   | growing an III Nitride barrier layer over the EPI layer;                |  |  |

| [1d]   | growing a GaN layer with acceptor type dopants over the barrier layer;  |  |  |

| [1e]   | depositing a gate contact layer on the doped GaN layer;                 |  |  |

| [1f]   | applying a gate photo resistant pattern;                                |  |  |

| [1g]   | etching away the gate contact layer outside the gate region;            |  |  |

| [1h]   | etching away the doped GaN layer, except a portion of the doped GaN     |  |  |

|        | layer beneath the gate contact;                                         |  |  |

| [1i]   | [1i] removing the gate photo resistant pattern;                         |  |  |

| [1j]   | [1j] depositing a dielectric layer;                                     |  |  |

| [1k]   | applying a contact photo resistant pattern;                             |  |  |

| [11]   | etching the dielectric layer to open the drain and source contact area; |  |  |

| [1m]   | removing the contact photo resistant pattern;                           |  |  |

| [1n]   | depositing an Ohmic contact metal;                                      |  |  |

| [1o]   | applying a metal photo resistant pattern;                               |  |  |

| [1p]   | etching the Ohmic contact metal;                                        |  |  |

| [1q]   | removing the metal photo resistant pattern; and                         |  |  |

| [1r]   | performing rapid thermal annealing to form Ohmic drain and source       |  |  |

|        | contacts.                                                               |  |  |

<sup>&</sup>lt;sup>1</sup> CALJ Cheney: "Why don't y'all put some kind of translation in your brief so that I know the nomenclature that's used at trial in comparison to what your opponent used so that I can compare apples to apples." Tr. 62:18-21.

#### **GROUND RULE 14.1 CERTIFICATION**

Counsel for Respondents certifies this post-hearing initial brief, which addresses those issues on which Respondents bear the burden of proof, complies with the word-count limit set by Ground Rule 14.1 and includes 19,963 words as measured by the word count feature of Microsoft Word.

Respondents will address in its post-hearing responsive brief those issues and evidence raised in the post-hearing initial briefs of Complainant and the Commission Investigative Staff. *See* Ground Rule 14.2. Respondents may also address any other issues in accordance with the Chief Administrative Law Judge's instructions given during the evidentiary hearing. Tr. 1263:2-7.

# I. INTRODUCTION AND BACKGROUND: BOTH ASSERTED PATENTS ARE INVALID IN VIEW OF PRIOR ART

Complainant EPC alleges infringement of two patents, U.S. Patent Nos. 8,350,294 ("the '294 patent") and 8,404,508 ("the '508 patent"), but both patents are invalid in view of the prior art, precluding a finding of violation.

#### A. The '294 Patent Is Invalid in View of Prior Art

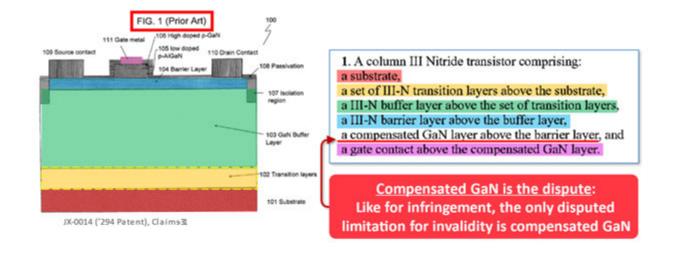

1. All Elements of the '294 Patent Are *Admitted* Prior Art Except "Compensated GaN Layer," Which Was Well Known in the Art

First, the '294 patent' claims a narrow, ultimately impractical, change over otherwise admitted prior art. The patent claims the use of an insulating "compensated GaN layer" instead of a conductive p-type GaN (pGaN) layer in a GaN based transistor to reduce gate leakage current (hereinafter "gate leakage" or "leakage"). But the prior art shows that the "compensated GaN layer" approach of the '294 patent was not new and, at best, was an obvious modification to existing devices. Forming compensated GaN layers and incorporating compensated GaN layers into transistors were known for many years before the '294 patent. For example, years before the '294 patent was filed, while working for a previous employer, one of the inventors (Dr. Robert Beach) of the '294 patent had applied for a patent (Beach189), which also used a "compensated GaN" layer. This inventor never disclosed his previous application to the USPTO during the '294 patent examination, but his previous patent application—undisputedly prior art—explicitly discloses use of a "compensated GaN" in a transistor. And other prior art also demonstrates that the structure of the '294 patent and the claimed use of hydrogen to passivate GaN (and create a "compensated GaN layer") was well known.

## Admitted Prior Art Has All But "compensated GaN"

**MInnoscience**

ontains Confidential Business Information — Subject To Protective Orde

RDX0013.13

**RDX-0013.13**

Claim is composed of regular elements of GaN FET

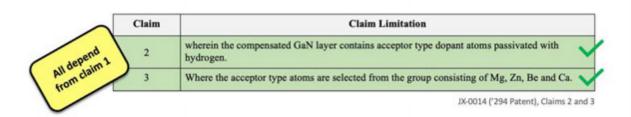

As Dr. Lebby explained during the Evidentiary Hearing, and EPC did not dispute, the only disputed element of claim 1 of the '294 patent is the "compensated GaN layer" present in claim elements [1e] and [1f]. Tr. (Lebby) 851:1-13; *see also id.* 856:25-4; 876:17-24; *see generally* Tr. (Schubert) 947:17-957:9. The prior art, specifically (1) *Uemoto* and (2) *Beach189* discloses this "compensated GaN layer," along with the other elements, and therefore invalidates claim 1. Further, (1) *Uemoto* and (2) *Beach189* in view of *Kigami* discloses all elements of claims 2 and 3. As shown in the figures below, and as will be described in the following sections, *Uemoto* renders obvious claims 1-3.

#### **Ground 2: Uemoto** Claim 1 **Not Disputed** A column III-Nitride transistor comprising: 1p 1A a substrate, 1B a set of III-N transition layers above the substrate, **Not Disputed** 1C **Not Disputed** a III-N buffer layer above the set of transition layers,

1D

1E

1F

**Not Disputed**

**M**Innoscience

RX-0126C ¶¶ 174-212 **Uemoto discloses all elements of claim 1** RDX-0013.56

Claim Limitation

Ground 2: Dependent Claims 2 and 3

a III-N barrier layer above the buffer layer,

a compensated GaN layer above the barrier layer, and

a gate contact above the compensated GaN layer.

**MInnoscience**

RX-0126C ¶¶ 174-212 **Uemoto discloses claims 2 and 3** RDX-0013.57

#### RDX-0013.57

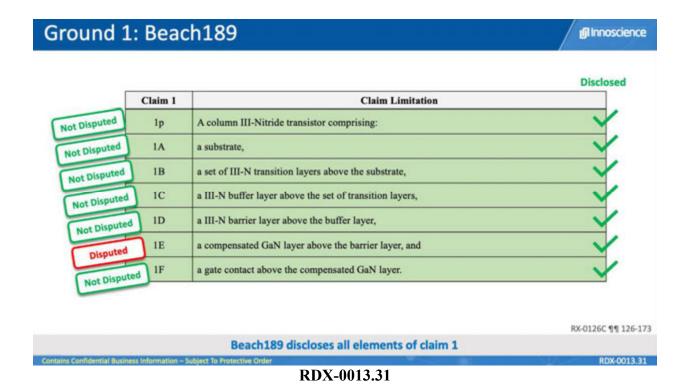

And, as shown in the figure below, and as will be described in the following sections, Beach 189 also discloses all elements of claim 1.

Therefore, the '294 patent is invalid over the prior art.

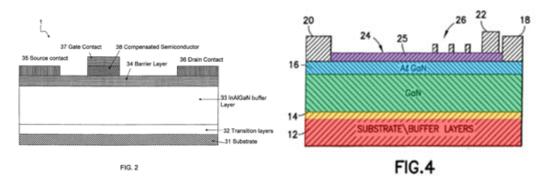

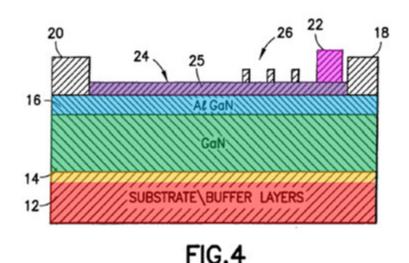

#### 2. EPC's Expert Agrees "Compensated GaN" Is Found in Prior Art

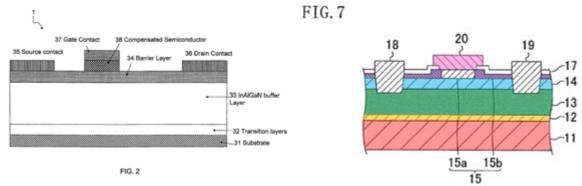

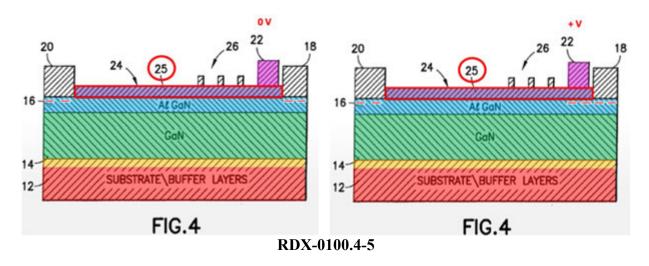

During the Evidentiary Hearing, Dr. Lebby testified that both *Beach189* and *Uemoto* disclose the single disputed element of the '294 patent. As shown in the two figures below, *Beach189* explicitly discloses this allegedly novel "compensated GaN layer." On the left, Figure 2, from the '294 patent, discloses a "compensated semiconductor 38." JX-0014 Fig 2. On the right, Figure 4, from *Beach189*, discloses this same compensated GaN layer 25 by referring to this layer with the unicorn words, "compensated GaN." RX-0011 ¶ [0026] ("[U]ltra resistive field plate 25 [is] formed with a highly electrically resistive material, such as . . . *compensated GaN*)" (emphasis added).

RDX-0013.11; JX-0014 Fig. 2 (left); RDX-0013.23; RX-0011 Fig. 4 (right) (annotated)

EPC's argument is that the "compensated GaN" of *Beach189* is different from the "compensated GaN" of the '294 patent, even though both references use the exact same unicorn words and describe the material in the same way. Tr. (Schubert) 950:16-951:8. In describing the features of this layer, the '294 patent states that the "compensated semiconductor layer 38 is a highly compensated semi-insulating material." JX-0014 3:47-48. And as Dr. Lebby described during the Evidentiary Hearing, the ultra resistive field plate 25 of *Beach189*, which is made from compensated GaN, is also semi-insulating. Tr. (Lebby) 938:15-939:4. Therefore, *Beach189* invalidates claim 1.

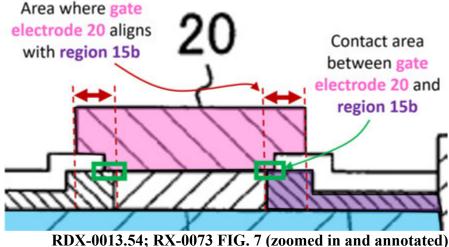

In addition, *Uemoto* discloses the disputed "compensated GaN layer," as shown in the two figures below. As described above, Figure 2 of the '294 patent discloses "compensated semiconductor 38." JX-0014 Fig 2. Shown below, Figure 7, from *Uemoto*, discloses the same compensated GaN layer 15b. RX-0073 Fig. 7. As Dr. Schubert admitted, this "layer 15b is gallium nitride, contains magnesium and hydrogen, is passivated, and is non-conductive. So in that sense, it meets the claim term 'compensated gallium nitride.'" Tr. (Schubert) 1033:21-1034:7.

RDX-0013.11; JX-0014 Fig. 2 (left); RDX-0013.53; RX-0073 Fig. 7 (right) (annotated)

EPC does not dispute that *Uemoto* discloses a compensated GaN layer. Tr. (Schubert) 964:1-7, 1033:21-1034:7. Instead, EPC incorrectly argues that 15b is not under the gate contact. But Dr. Schubert *admitted* that at least "a sliver of region 15B" *is under* gate electrode 20. Tr. (Schubert) 965:3-19 ("[T]he gate electrode is above a small region of layer 15b."); *see also id*. 966:21-24. Based on Dr. Schubert's own testimony, region 15b is under the gate contact, and thus satisfies the requirements of claim 1, making claim 1 invalid in view of *Uemoto*.

#### B. The '508 Patent Is Also Invalid in View of Prior Art

#### 1. All Elements of the '508 Patent Were Known in the Art

Turning second to the <u>'508 patent</u>, this patent is entirely about a prior art device, the known normally-off GaN transistor. Rather than claiming a new device, the '508 patent claims a specific allegedly new method of manufacture, one way (but not all ways) to make a "self-aligned" gate wherein the gate metal and the underlying p-type GaN layer are etched together and thus their edges are aligned to each other. But self-aligned processes had been used in the manufacture of transistors for decades. Indeed, Robert Beach had previously used the same "self-aligned" technique, aligning the gate contact and doped GaN layer to each other, as shown by *Beach624*.

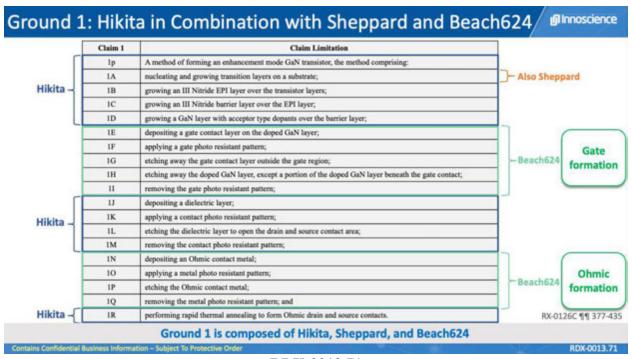

As Dr. Lebby explained during the Evidentiary Hearing, all elements of claim 1 can be found in the prior art, specifically, *Hikita*, *Sheppard*, and *Beach624*. Tr. (Lebby) 895:6-913:21. The figure below shows where each element of claim 1 can be found in the prior art.

RDX-0013.71

As shown in the figure below, *Hikita, Sheppard*, and *Beach624* show that the method of the '508 patent was obvious over the prior art.

RDX-0013.105

# 2. EPC's Expert Agrees All Elements of Asserted Claim 1 Are Found in Prior Art

While the '508 patent appears more complex at first glance, claim 1 is simply comprised of elements that were known in the prior art, as shown by the figures above. Even EPC admits as much, and instead only argues (1) the '508 patent allegedly teaches a gate-first process, (2) *Beach624* discloses using separate gate photo resistant and metal photo resistant patterns, and (3) there is a lack of motivation to combine *Hikita* and *Beach624*. Tr. (Schubert) 972:12-23; 1004:5-11. None of these three arguments rebut the clear and convincing evidence the combination renders the claim obvious.

With respect to (1), EPC *never proposed* a construction of claim 1 that required the claim elements to occur in a specific order, and the claim itself does not require a gate first process. The only order the patent emphasizes is the order of the gate stack itself, which EPC argues can be performed in *any* order. EPC's contradictory, and late, position on "gate first" is wrong.

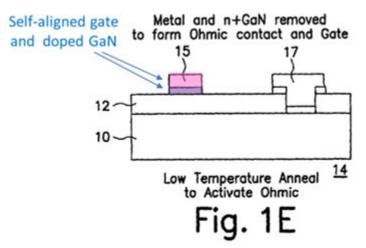

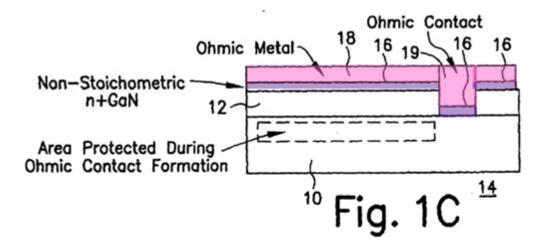

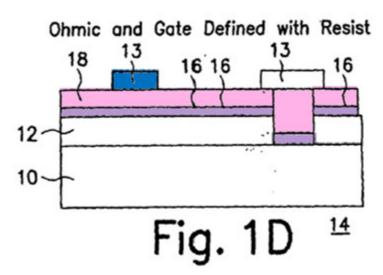

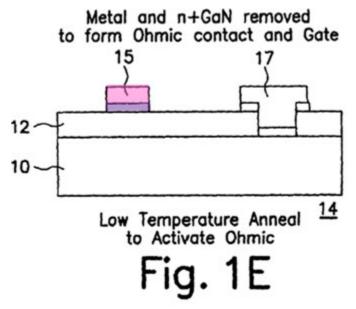

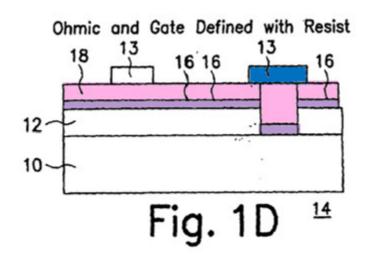

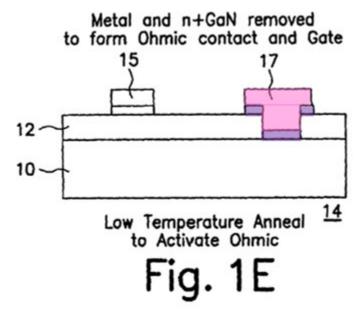

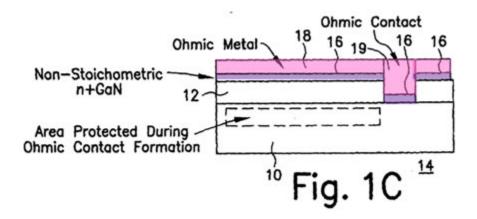

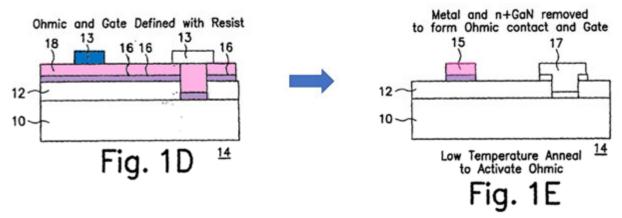

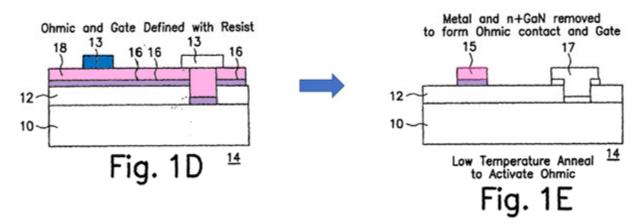

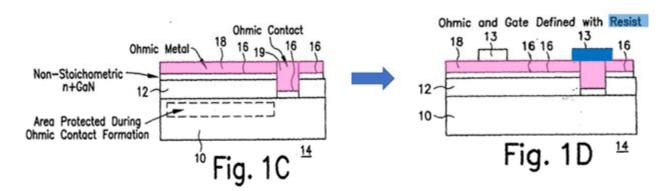

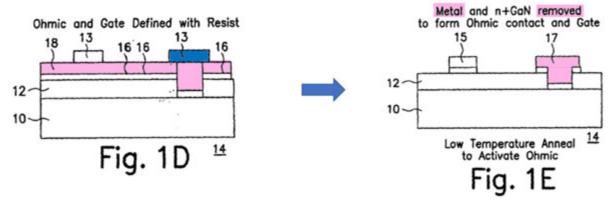

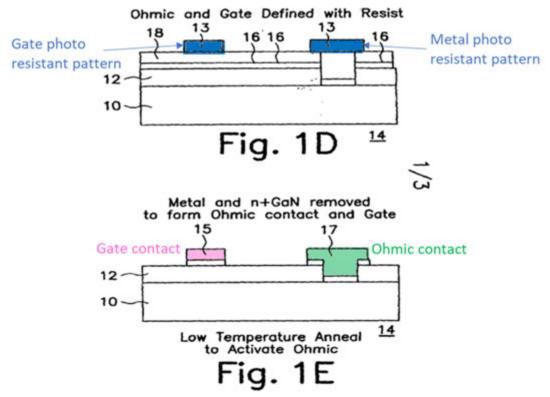

With respect to (2), EPC provides a narrow reading of *Beach624*, assuming incorrectly that one photoresist pattern must be used to form the gate and ohmic contacts simultaneously. But the figures show two different photoresist patterns are used to separately form the gate and ohmic contact. RDX-0013.102; RX-0286 Figs. 1D, 1E. Further, nothing in the claim limits these patterns from being applied simultaneously, so this attack is a strawman.

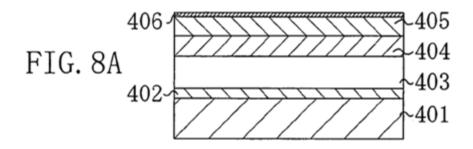

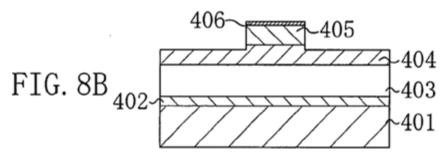

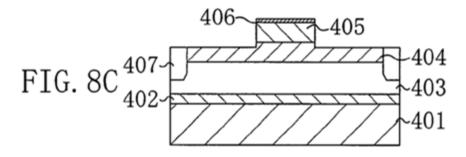

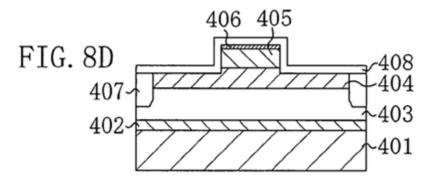

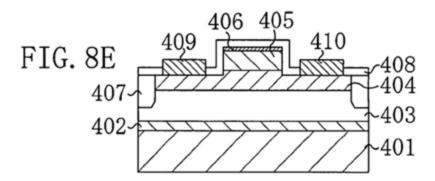

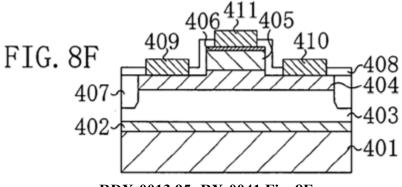

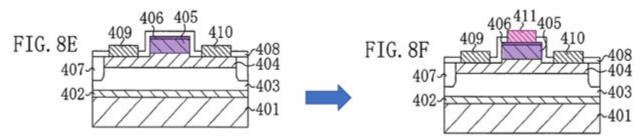

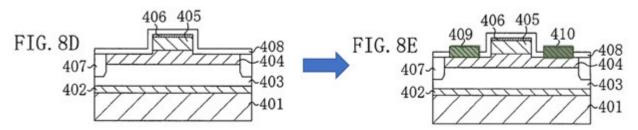

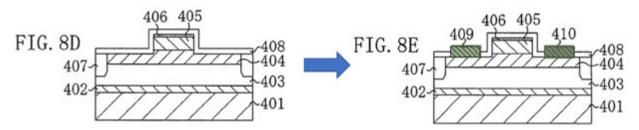

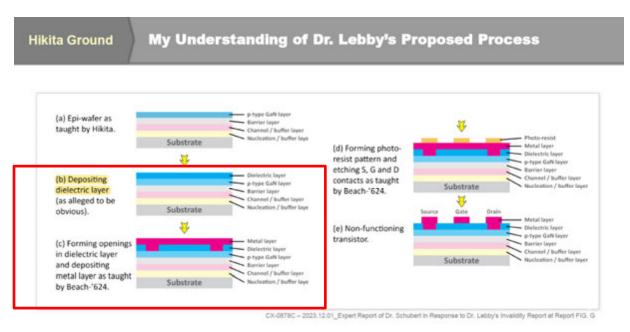

Finally, with respect to number (3), EPC misinterprets the combination and applies an incorrect analysis that is contrary to the law. In particular, EPC does not attack Dr. Lebby's actual combination, but rather Dr. Schubert's "understanding" of the combination. This "understanding" incorrectly assumes the gate would be deposited after, or on top of, the dielectric layer. But *Hikita*, as Dr. Lebby explained, describes etching the doped GaN layer **before** depositing a dielectric layer. Tr. (Lebby) 910:3-14; Tr. (Schubert) 996:13-20; RX-0041, ¶ [0061] ("The source electrode 409, the drain electrode 410 and the gate electrode 411 may be formed before formation of the SiN film 408"); Figs. 8C, 8D. That ordering is preserved in Dr. Lebby's combination, but not Dr. Schubert's manufactured "understanding." Indeed, on cross examination, Dr. Schubert acknowledged that *Hikita* disclosed depositing the dielectric layer **after depositing the gate metal**. Tr. (Schubert) 1029:14-1030:7. As all the elements of the only asserted claim were known in the art, and EPC's attacks on the motivations to combine fail, claim 1 is invalid as obvious.

As the evidence shows and as summarized herein, both asserted patents are invalid. Innoscience respectfully requests that the CALJ so hold.

#### C. Procedural History of the Investigation

This Investigation instituted on July 3, 2023, based on EPC's May 26, 2023 Complaint, as supplemented, which alleged infringement of certain claims of U.S. Patent Nos. 8,350,294 ("the '294 patent"); 8,404,508 ("the '508 patent"); 9,748,347 ("the '347 patent"); and 10,312,335 ("the '335 patent"). 88 Fed. Reg. 42756 (Jul. 3, 2023). On December 13, 2023, and February 12,

2024, the CALJ issued Order Nos. 9 and 12, respectively granting EPC's motions to terminate the '347 patent and the '335 patent from the investigation. EPC continues to assert claims 1-3 of the '294 patent and claim 1 of the '508 patent.

The Evidentiary Hearing took place on February 26 through March 1, 2024. The Final Initial Determination is currently due June 3, 2024, and the Target Date is October 3, 2024.

#### **D.** The Private Parties

#### 1. Respondents

**Innoscience (Zhuhai):** Innoscience (Zhuhai) Technology Company, Ltd. Is a Chinese corporation that has a principal place of business and headquarters at No. 39, Jinyuan 2<sup>nd</sup> Road, High-Tech Zone, Zhuhai, Guangdong, 519099 China.

**Innoscience America:** Innoscience America, Inc. is a California corporation that has its principal place of business at 5451 Great America Pkwy, Ste 125, Santa Clara, CA 95054.

Innoscience (Zhuhai) and Innoscience America are collectively referred to as "Innoscience" or "Respondents" herein.

#### 2. Complainant

Complainant Efficient Power Conversion Corporation ("Complainant" or "EPC") is a Delaware corporation with its headquarters and principal place of business located at 909 N. Pacific Coast Highway, Suite 230, El Segundo, CA 90245.

#### E. The Patents-at-Issue

# 1. Overview of the '294 Patent: All Elements Are *Admitted* as Prior Art, Except "Compensated GaN"

The '294 patent issued on January 8, 2013. JX-0014 Cover. The patent issued from an application that was submitted on April 8, 2010, which claimed priority to provisional application 61/167,792 submitted on April 8, 2009. *Id*.

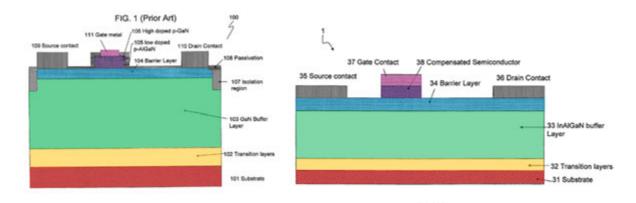

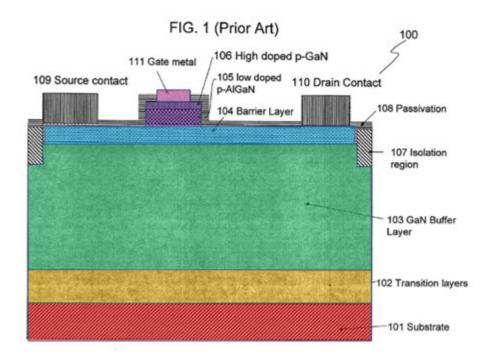

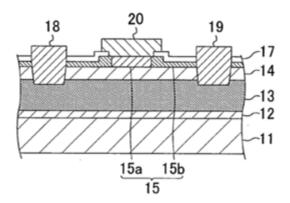

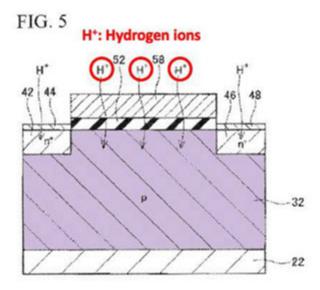

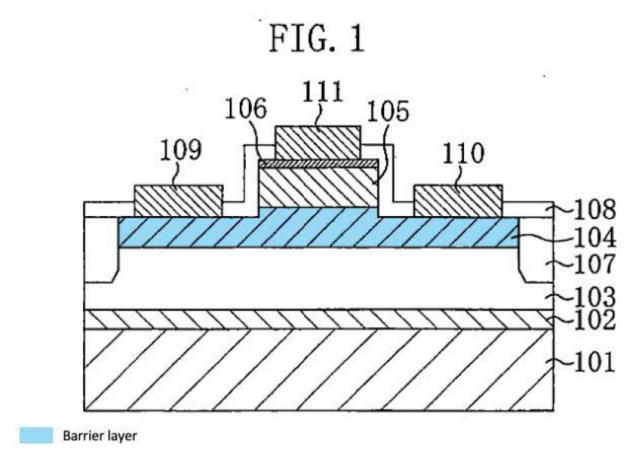

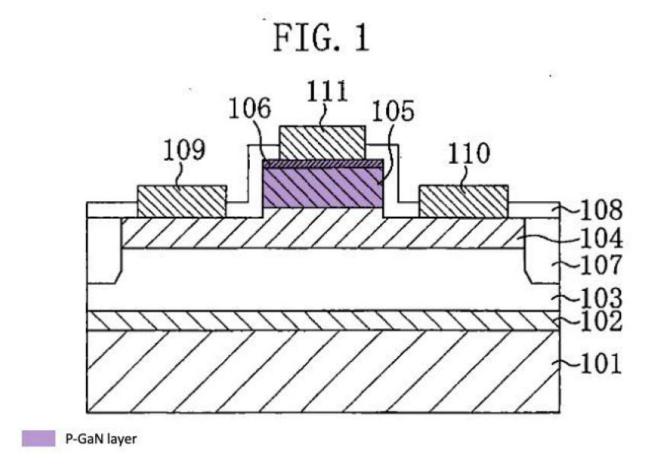

The '294 patent relates to a "transistor with a compensated GaN layer or a semi-insulating GaN layer below the gate contact and above the barrier." JX-0014 1:16-18. The '294 patent concedes that GaN transistors were "prior art." JX-0014 1:55-2:2, Fig. 1. The '294 patent also concedes that "conventional enhancement mode GaN transistor[s]" formed with a substrate, transition layers, buffer layer, barrier layer, p-type layers, and contacts for gate and source/drain were known in the prior art. JX-0014 1:55-2:2. Figure 1 of the '294 patent, which is labeled "Prior Art" and reproduced with color coding below, illustrates the admitted prior art.

RDX-0012C.12; RDX-0013.13; JX-0014 FIG. 1

The '294 patent describes Figure 1 as "a cross-section of a prior art transistor" for "a conventional enhancement mode GaN transistor device." JX-0014 1:55-2:23. The '294 patent describes the Admitted Prior Art ("APA") as including a "substrate 101 that can be composed of silicon (Si), silicon carbide (SiC), sapphire, or other material, transition layers 102 typically composed of AlN and AlGaN that is about 0.1 to about 1.0 μm in thickness, buffer material 103 typically composed of GaN that is about 0.5 to about 10 μm in thickness, barrier material 104

typically composed of AlGaN where the Al to Ga ratio is about 0.1 to about 0.5 with thickness from about 0.005 to about 0.03 μm, p-type AlGaN 105, heavily doped p-type GaN 106, ... and gate metal 111 typically composed of a nickel (Ni) and gold (Au) metal contact over a p-type GaN gate." JX-0014 1:55-2:9.

The '294 patent purports to address leakage issues in APA transistors, stating that forming a "compensated" or a "semi-insulating" layer "below the gate contact" could reduce leakage. JX-0014 2:3-9, 3:17-21, 3:63-67. The patent pinpoints its "invention" as the formation of a compensated layer through passivation, emphasizing that "[t]he critical step . . . that differentiates the device of the present invention from the prior art device (FIG. 1) is the passivation of a p-type impurity using hydrogen." JX-0014 3:43-45. Tr. (Schubert) 433:7-22; *see also* Tr. (Lidow) 103:2-19.

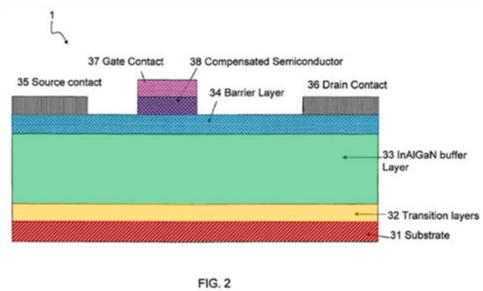

The '294 patent presents different transistor embodiments that include either "compensated" or "semi-insulating" layers. The first embodiment has a **substrate**, **transition**, **buffer**, **barrier**, **gate** of (elements the patent notes were already present in conventional prior art transistors), and a "[c]ompensated semiconductor layer 38 [that] preferably comprises AlGaN or GaN with a deep level passivated p-type impurity" below the gate (substituting a p-type layers). JX-0014 3:10-11. Figure 2, reproduced and color-coded below, illustrates the first embodiment which includes such a compensated semiconductor layer:

JX-0014 Fig. 2

As the patent notes, the only notable difference between the APA and the alleged invention in this embodiment is the use of a passivation step to compensate the capping layer below the gate metal; the other relevant features remain the same. JX-0014 3:43-52. Specifically, the patent identifies a passivation step for the formation of the compensated layer as the key element distinguishing from the prior art, stating that "[t]he critical step in the above process that differentiates the device of the present invention from the prior art device (FIG. 1) is the passivation of a p-type impurity using hydrogen." JX-0014 3:43-45.

Comparing the first embodiment with the APA, both shown in the figures below, illustrates this minor difference. On the right, the alleged invention includes a "compensated semiconductor" layer (labeled as element 38) under the gate contact. The APA structure on the left, however, includes doped p-type layers (labeled as elements 105 and 106). The substrate, transition layers, buffer layer, barrier layer, and gate metal, remain the same between the two structures.<sup>2</sup>

13

<sup>&</sup>lt;sup>2</sup> Figures 1 and 2 also have a different label for the buffer layer, with FIG. 1 labeling "103 GaN Buffer Layer" while FIG. 2 labels "33 InAlGaN buffer layer." But the labeling only reflects an embodiment of the patent and refers to a generic formulation. JX-0014 2:63-65. The patent and

RDX-0012C.12; RDX-0013.13; JX-0014 Figs. 1 (left) and 2 (right)

The second, third, and fourth embodiments of the '294 patent are substantially similar to the first embodiment, except they include "a semi-insulating layer 39 in place of the compensated semiconductor layer 38" (JX-0014 3:56-57) and, optionally, "a confinement layer . . . above the semi-insulating layer" (JX-0014 4:32-33) or "a spacer layer 49 beneath semi-insulating layer" (JX-0014 4:65-66). These additional embodiments relate solely to variations of the layers between the gate metal and the barrier layer.

EPC asserts claims 1-3 of the '294 patent. The asserted claims are reproduced below:

| Claim  | Limitation                                                      |  |  |

|--------|-----------------------------------------------------------------|--|--|

| [1pre] | A column III Nitride transistor comprising:                     |  |  |

| [1a]   | a substrate,                                                    |  |  |

| [1b]   | a set of III-N transition layers above the substrate,           |  |  |

| [1c]   | a III-N buffer layer above the set of transition layers,        |  |  |

| [1d]   | a III-N barrier layer above the buffer layer,                   |  |  |

| [1e]   | a compensated GaN layer above the barrier layer, and            |  |  |

| [1f]   | a gate contact above the compensated GaN layer.                 |  |  |

|        |                                                                 |  |  |

| [2pre] | The transistor of claim 1,                                      |  |  |

| [2a]   | wherein the compensated GaN layer contains acceptor type dopant |  |  |

|        | atoms passivated with hydrogen.                                 |  |  |

|        |                                                                 |  |  |

| [3pre] | The transistor of claim 2,                                      |  |  |

claims are clear the buffer layer is "made of a III Nitride material," which "can be composed of  $In_xAl_yGa_{1-x-y}N$  where  $x+y \le 1$ ," including GaN. JX-0014 3:12-15.

14

| Claim | Limitation                                                           |

|-------|----------------------------------------------------------------------|

| [3a]  | where the acceptor type atoms are selected from the group consisting |

|       | of Mg, Zn, Be and Ca.                                                |

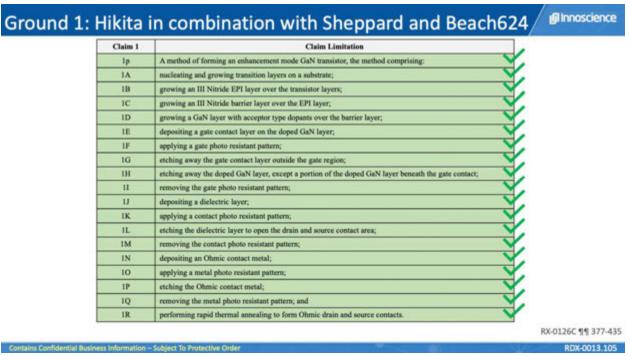

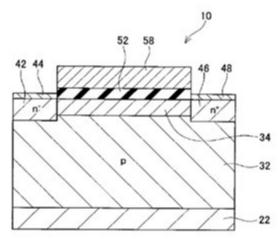

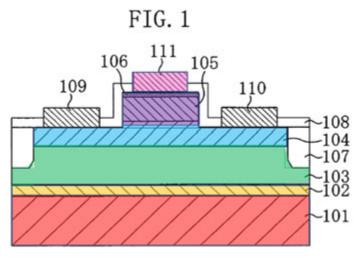

# 2. Overview of the '508 Patent: The Device Itself Is Admitted Prior Art, While the "Present Invention" Is About the Process of Self-Aligning the Gate Metal and Doped GaN Materials

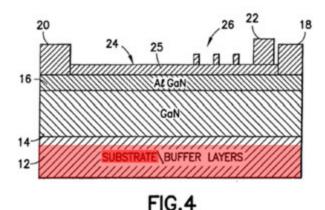

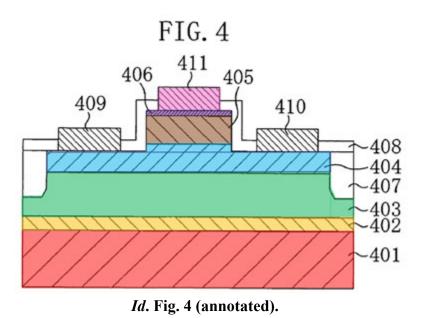

The '508 patent issued on March 26, 2013. JX-0015 Cover. The patent issued from an application that was filed on April 8, 2010, and claims priority to a provisional application that was filed on April 8, 2009. *Id.* The '508 patent is entitled "Enhancement mode GaN HEMT device and method for fabricating the same."

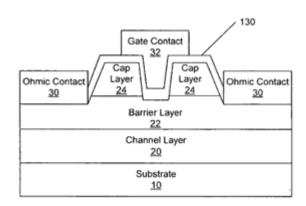

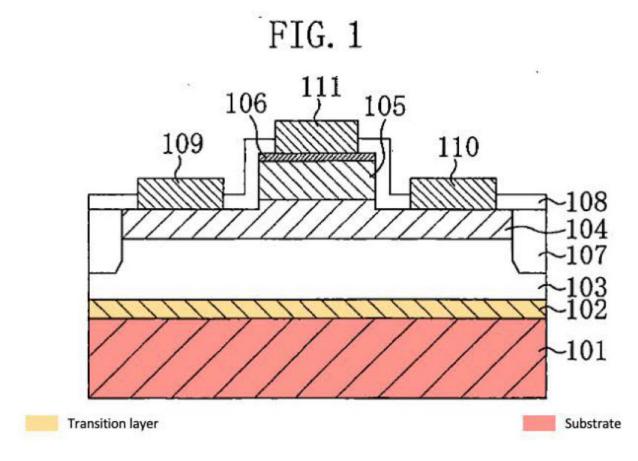

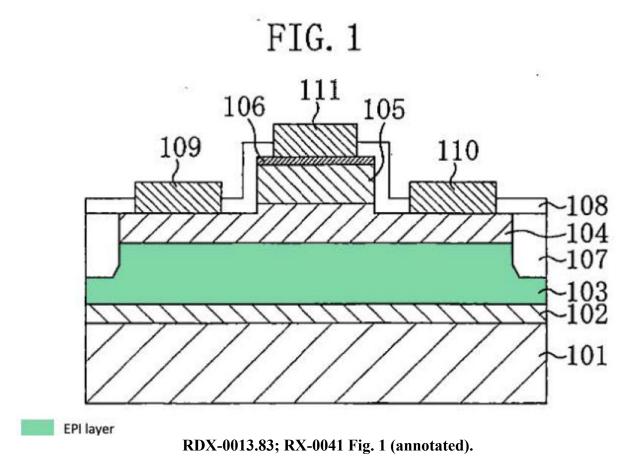

The '508 patent admits the basic features of an enhancement-mode GaN transistor were conventional and well known, as Figure 1 below shows. JX-0015 1:32-64. The '508 patent describes "a conventional enhancement mode GaN transistor device 100 which includes substrate 101 which can be either sapphire or silicon, transition layers 102, un-doped GaN material 103, un-doped AlGaN material 104, source ohmic contact metal 109, drain ohmic contact metal 110, p-type AlGaN or p-type GaN material 105, heavily doped p-type GaN material 106, and gate metal 111." JX-0015 1:58-64.

**RDX-0013.69**; **JX-0015** Fig. 1 (annotated)

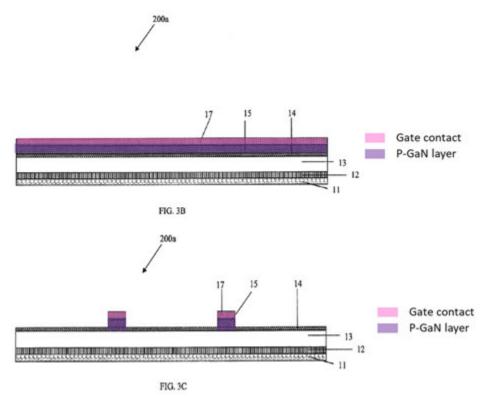

The '508 patent is instead directed to a method of forming a GaN-based transistor by self-aligning a doped GaN layer with the gate contact. The specification makes clear that using a self-aligned process to form the doped GaN layer and gate contact is essential to the purported invention of the '508 patent. See JX-0015 Abstract ("[T]he gate III-V compound and the gate metal are formed with a single photo mask process to be self-aligned and the bottom of the gate metal and the top of the gate compound have the same dimension."), 2:15-17 ("It would be desirable to provide an enhancement mode GaN transistor structure with a self-aligned gate which avoids the above-mentioned disadvantages of the prior art."), 3:1-6 ("The present invention is an enhancement mode GaN HEMT device with a gate metal material and a doped GaN or AlGaN material that are self-aligned, and a method for making such a device. The materials are patterned and etched using a single photo mask, which reduces manufacturing costs.").

The '508 patent states, "The present invention is an enhancement mode GaN HEMT device with a gate metal material and a doped GaN or AlGaN material that are self-aligned, and a method for making such a device." JX-0015 3:1-4. To achieve self-alignment, the patent explains that "[t]he materials are patterned and etched using a single photo mask." JX-0015 3:4-6. Figures 3B and 3C below illustrate a self-aligned process in which gate metal 17 and p-type GaN gate layer 15 are self-aligned.

RDX-0013.89; JX-0015 Figs. 3B, 3C (annotated)

In every embodiment provided by the '508 patent, the doped GaN layer and gate contact are self-aligned, which the '508 patent describes as having the same dimension at the point of contact of these layers. *See* JX-0015 Abstract ("[T]he gate III-V compound and the gate metal are formed with a single photo mask process to be self-aligned and the **bottom of the gate metal and the top of the gate compound have the same dimension**."), 3:10-17, 4:6-10, 4:20-25, 4:55-59, 5:4-17, 5:23-30, 5:38-45, 5:52-58, 5:61-6:1, 6:15-21, Figs. 2, 3A-3E, 4, 5A-5E, 6, 7A-7F, 8-12.

In addition to structures with the same dimension at the point of contact between the gate contact and doped GaN layer, the '508 patent also describes embodiments in which additional etching of the gate contact is performed after first forming a self-aligned gate contact and doped GaN layer. *See* JX-0015 Figs. 9, 10, 12. The '508 patent makes clear that in those embodiments the gate contact and doped GaN layer are self-aligned at an intermediate step of the process before additional etching of the gate contact is performed. JX-0015 5:38-45 (fifth embodiment), 5:52-58 (sixth embodiment), 6:15-21 (eighth embodiment).

EPC asserts claim 1 of the '508 patent. The asserted claim is reproduced below:

| Claim  | Limitation                                                              |  |  |

|--------|-------------------------------------------------------------------------|--|--|

| [1pre] | A method of forming an enhancement mode GaN transistor, the             |  |  |

|        | method comprising:                                                      |  |  |

| [1a]   | nucleating and growing transition layers on a substrate;                |  |  |

| [1b]   | growing an III Nitride EPI layer over the transistor layers;            |  |  |

| [1c]   | growing an III Nitride barrier layer over the EPI layer;                |  |  |

| [1d]   | growing a GaN layer with acceptor type dopants over the barrier layer;  |  |  |

| [1e]   | depositing a gate contact layer on the doped GaN layer;                 |  |  |

| [1f]   | applying a gate photo resistant pattern;                                |  |  |

| [1g]   | etching away the gate contact layer outside the gate region;            |  |  |

| [1h]   | etching away the doped GaN layer, except a portion of the doped GaN     |  |  |

|        | layer beneath the gate contact;                                         |  |  |

| [1i]   | removing the gate photo resistant pattern;                              |  |  |

| [1j]   | depositing a dielectric layer;                                          |  |  |

| [1k]   | applying a contact photo resistant pattern;                             |  |  |

| [11]   | etching the dielectric layer to open the drain and source contact area; |  |  |

| [1m]   | removing the contact photo resistant pattern;                           |  |  |

| [1n]   | depositing an Ohmic contact metal;                                      |  |  |

| [10]   | applying a metal photo resistant pattern;                               |  |  |

| [1p]   | etching the Ohmic contact metal;                                        |  |  |

| [1q]   | removing the metal photo resistant pattern; and                         |  |  |

| [1r]   | performing rapid thermal annealing to form Ohmic drain and source       |  |  |

|        | contacts.                                                               |  |  |

#### II. U.S. PATENT NO. 8,350,294

# A. Claim Construction for the '294 Patent: Compensated GaN Is at Least Nonconductive or Semi-Insulating

The parties dispute the construction of the term "compensated GaN layer" as recited in element [1e] of claim 1 of the '294 patent. The proposed constructions are:

| Term           | EPC                           | Innoscience           | Staff                |

|----------------|-------------------------------|-----------------------|----------------------|

| "a compensated | A semiconductor GaN gate      | "a doped GaN layer    | "a GaN layer in      |

| GaN layer"     | material in which one type of | formed with a step to | which one type of    |

|                | impurity (for example,        | passivate its         | impurity cancels     |

| (Claim 1, '294 | donor) cancels the electrical | impurities"           | the electric effects |

| Patent)        | effects of the other type of  |                       | of another type of   |

|                | impurity (for example,        | which is a "product-  | impurity"            |

|                | acceptor)                     | by- process"          |                      |

|                | - '                           | limitation.           |                      |

|                | Not a "product-by-process"    |                       |                      |

|                | limitation.                   |                       |                      |

At the Markman Hearing, the CALJ provided preliminary opinions on the term's construction. The CALJ indicated he is "not inclined to construe this as a product-by-process claim" and "not inclined to insert gate material into the construction." Markman Tr. 136:2-4. The CALJ also signaled he is inclined to apply a plain and ordinary meaning, indicating that he is "inclined to just use the words of the claim" and suggested the term's construction "is just going to be plain and ordinary meaning and you have a fact dispute over whether enough compensation has happened." *Id.* 136:9-13, 291:15-18.

Although the parties do not agree on the plain and ordinary meaning of "compensated GaN layer," the parties agree on what a "compensated GaN layer" is not: it is undisputed that conductive p-type GaN ("pGaN") is not "compensated GaN." The parties agree that a "compensated GaN" is passivated and a nonconductive or semi-insulating p-type GaN ("pGaN"). CDX-0002C.3; Tr. (Schubert) 433:7-22.

# B. Invalidity of the '294 Patent: Both Grounds Invalidate All Three Asserted Claims

The evidence shows that the asserted claims of the '294 patent are invalid under 35 pre-AIA U.S.C. §§ 102 and 103.

#### 1. Priority Date

The relevant priority date for the '294 patent, as well as the date from which to apply the perspective of a POSITA for the '294 patent, is April 8, 2009. JX-0014 Cover. Thus, pre-AIA 35 U.S.C. § 102 applies.

#### 2. Level of Ordinary Skill

A POSITA for both the '294 and '508 patents would have had at least a bachelor's degree in electrical engineering, chemical engineering, physics, or material science or a closely related field and at least two years of experience in semiconductor device design or fabrication, including the processing of semiconductor materials, analysis of device operation, or the development of new device topologies. Tr. (Lebby) 847:16-848:9. This definition is undisputed as EPC did not present a different definition during the Evidentiary Hearing.

#### 3. Overview of the Prior Art

The following references, either alone or in combination, invalidate claims 1-3 of the '294 patent:

- **RX-0073:** U.S. Patent Application Publication No. 2008/0087915A1 to Uemoto et al. ("*Uemoto*")

- **RX-0011:** U.S. Patent Application Publication No. 2006/0145189A1 to Beach ("Beach189")

- **RX-0079:** Japanese Patent Application Publication No. JP2006253224A to Kigami et al. ("*Kigami*")

Each of the above references qualifies as prior art.

#### a. *Uemoto* (US2008/0087915A1, RX-0073)

*Uemoto* is a U.S. patent publication published on April 17, 2008, that was filed on July 24, 2007. RX-0073 Cover. Thus, *Uemoto* is prior art under pre-AIA § 102(a), as EPC does not dispute. *See* Tr. (Schubert) 949:8-19.

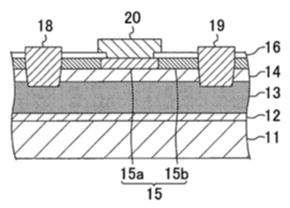

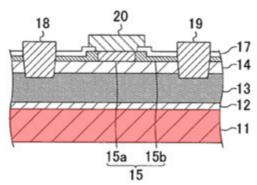

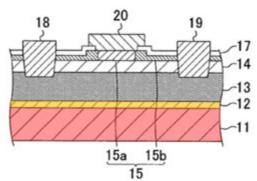

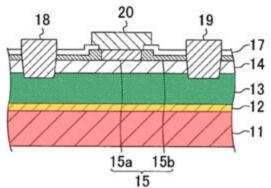

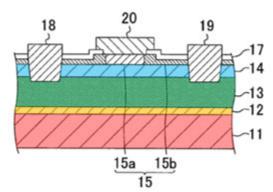

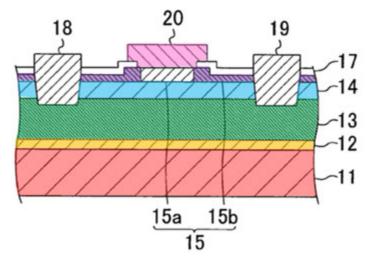

*Uemoto* discloses III-nitride transistors formed with multiple nitride layers, and it describes the formation of transistors with source, gate, and drain electrodes. RX-0073 ¶¶ [0031]-[0035]; Tr. (Lebby) 873:21-874:2. Figure 1 below illustrates an embodiment of a transistor structure discussed in *Uemoto*.

FIG. 1

RDX-0013.43; RX-0073 Fig. 1

According to *Uemoto*, the layer 15 can be formed having two regions: a control region 15a (with active impurities) and a highly resistive region 15b (where hydrogen inactivates or passivates impurities). RX-0073 ¶¶ [0015], [0033], FIG. 1. *Uemoto* discloses that the selective formation of the high resistive region 15b with hydrogen diffusion reduces leakage current between the gate and the drain and improves the transistor performance by making it more stable. *Id.* ¶¶ [0059], [0063]-[0064], Figs. 7-8.

#### b. *Beach189* (US2006/0145189A1, RX-0011)

Beach 189 is a U.S. patent application publication that published on July 6, 2006. RX-0011 Cover. Thus, Beach 189 is prior art under pre-AIA § 102(b), as EPC does not dispute. The inventor of Beach 189 is the same inventor Robert Beach identified on the '294 patent. Compare RX-0011 Cover with JX-0014 Cover. During the examination of the '294 patent, however, Robert Beach did not disclose his previous Beach 189 patent application to the USPTO. JX-0014 Cover; see generally JX-0004.

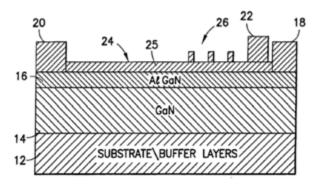

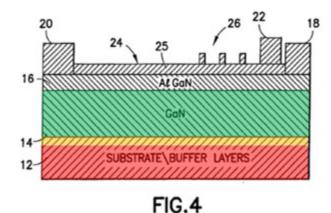

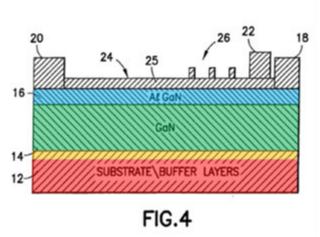

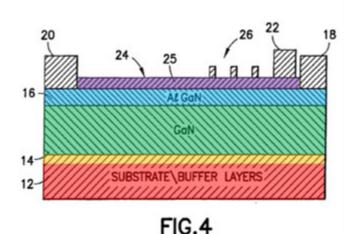

Beach189 relates to a III-nitride transistor, describing "a III-nitride heterojunction power semiconductor device" and a "typical III-nitride power semiconductor device [that] includes a drain electrode, a source electrode and a gate electrode [that] controls the current." RX-0011 ¶¶ [0002]-[0003]. Beach189 describes a method to improve the transistor's performance using a "field relaxation feature [that] includes an ultra resistive field plate." RX-0011 ¶¶ [0004]-[0006]. Beach189 discloses that the "ultra resistive field plate 25" is "formed with a highly electrically resistive material, such as, silicon rich SiN, compensated GaN or the like material." RX-0011 ¶¶ [0026] (emphasis added); see also RX-0011 Claim 7 ("field plate is comprised of a compensated III-nitride semiconductor"). In FIG. 4, reproduced below, Beach189 illustrates an embodiment showing such a field plate (element 25), along additional elements such as a substrate, buffer layers, and gate electrode. RX-0011 ¶¶ [0026], [0040]-[0044].

FIG.4 RDX-0013.19-25; RX-0011 Fig. 4

#### c. *Kigami* (JP2006253224A, RX-0079)

*Kigami* is a Japanese patent application publication published on September 21, 2006. RX-0079 Cover. Thus, *Kigami* is prior art under pre-AIA § 102(b).

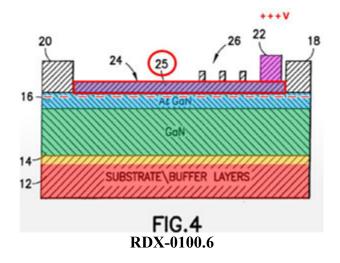

Kigami discloses normally-off III-nitride transistors. RX-0079 ¶¶ [0001]-[0005]. Kigami teaches that III-nitride transistors can be improved by introducing hydrogen into GaN layers to passivate impurities. RX-0079 ¶¶ [0007], [0022]. Kigami discloses techniques to introduce hydrogen in GaN layers using an ionized hydrogen gas. RX-0079 ¶ [0026], Fig. 5. Kigami describes that the introduced hydrogen forms a composite with magnesium, inactivating the magnesium impurities, improving the breakdown, frequency, and threshold characteristics. RX-0079 ¶¶ [0007], [0022], [0023], [0029]. Figure 1, reproduced below, illustrates Kigami's transistor structure.

FIG. 1

RDX-0013.34; RX-0079 Fig. 1

## 4. *Uemoto* Ground: *Uemoto* Renders Claims 1-3 Obvious

## a. [1pre]: A column III Nitride transistor

To the extent the preamble is limiting, *Uemoto* discloses it. Tr. (Lebby) 874:14-22; RDX-0013.45. *Uemoto* discloses "nitride semiconductor transistors" made with "III Nitride materials." RX-0073 ¶¶ [0005], [0031]-[0032]; Tr. (Lebby) 874:16-22. *Uemoto*'s Figure 7, reproduced below, illustrates "a cross sectional view showing a nitride semiconductor transistor." RX-0073 Fig. 7.

FIG. 7

RDX-0013.45; RX-0073 Fig. 7

EPC does not dispute *Uemoto* discloses the preamble [1pre] of claim 1, challenging instead a hypothetical "non-functioning transistor embodiment." Tr. (Lebby) 874:18-22. The claim,

however, does not require any functionality. JX-0014 Claim 1. And there is no evidence that any of *Uemoto*'s disclosed embodiments are "non-functioning." *See* RX-0073. Further, "[a] prior art reference does not need to be fully functional to quality as prior art; indeed, a prior art reference 'need not work' and may even be 'inoperative." *Metso Mins., Inc. v. Powerscreen Int'l Distribution, Ltd.*, 526 F. App'x 988, 955 (Fed. Cir. 2013) (citation omitted).

# b. [1a]: a substrate

*Uemoto* discloses [1a]. Tr. (Lebby) 874:24-875:6; RDX-0013.46. EPC does not dispute that *Uemoto* satisfies [1a]. Tr. (Lebby) 875:1-6. *Uemoto* discloses "a substrate 11 [that] is made of silicon," the same material the '294 patent associates with [1a]. RX-0073 ¶ [0031]; Tr. (Lebby) 875:1-6. *Uemoto*'s Figure 7 below highlights **substrate 11**.

FIG. 7

**RDX-0013.46**; **RX-0073** Fig. 7 (annotated)

# c. [1b]: a set of III-N transition layers above the substrate

*Uemoto* renders obvious [1b]. Tr. (Lebby) 875:9-17; RDX-0013.47. EPC does not dispute that *Uemoto* satisfies [1b]. Tr. (Lebby) 875:11-22. *Uemoto* discloses or at least renders obvious [1b] by describing a "buffer layer 12 of AlN having a thickness of 100 nm is formed on the principal plane of the substrate 11," which is formed with the same material as the transition layers described in the '294 patent. RX-0073 ¶ [0031]; Tr. (Lebby) 875:9-17. *Uemoto*'s buffer layer 12,

located above **substrate 11**, teaches or suggests the claimed III-N transition layers as highlighted in Figure 7 below.

FIG. 7

RDX-0013.47; RX-0073 Fig. 7 (annotated)

# d. [1c]: a III-N buffer layer above the set of transition layers

Uemoto discloses [1c]. Tr. (Lebby) 875:19-876:2; RDX-0013.48. EPC does not dispute Uemoto satisfies [1c]. Tr. (Lebby) 875:21-876:2. Uemoto discloses "[a] first nitride semiconductor layer 13 [(buffer layer)] of undoped GaN . . . formed on the buffer layer 12." RX-0073 ¶ [0032]; Tr. (Lebby) 875:21-876:2. Uemoto's semiconductor layer 13 is formed with the same material the '294 patent associates with a "buffer layer." JX-0014 3:12-15 ("Buffer layer 33 and barrier layer 34 are made of a III Nitride material.") Uemoto's Figure 7 below highlights semiconductor layer 13, which is located above buffer layer(s) 12.

FIG. 7

RDX-0013.48; RX-0073 Fig. 7 (annotated)

## e. [1d]: a III-N barrier layer above the buffer layer

*Uemoto* discloses [1d]. Tr. (Lebby) 876:4-13; RDX-0013.49. EPC does not dispute that *Uemoto* satisfies [1d]. Tr. (Lebby) 876:6-7. *Uemoto* discloses "a second nitride semiconductor layer 14 of undoped AlGaN" (barrier layer) formed above the first nitride semiconductor layer 13. RX-0073 ¶ [0032]; Tr. (Lebby) 876:6-13. *Uemoto*'s second nitride semiconductor layer 14 is formed with the same material the '294 patent associates with the "barrier layer." JX-0014 3:12-15 ("Buffer layer 33 and barrier layer 34 are made of a III Nitride material.") *Uemoto*'s Figure 7 below highlights semiconductor layer 14, which is located above semiconductor layer 13.

FIG. 7

RDX-0013.49; RX-0073 Fig. 7 (annotated)

f. Expert Opinions Regarding Disputed Elements: [1e]: a compensated GaN layer above the barrier layer and [1f]: a gate contact above the compensated GaN layer

*Uemoto* discloses or at least renders obvious limitations [1e] and [1f]. Tr. (Lebby) 876:15-879:14; RDX-0013.50-54. Taken together, limitations [1e] and [1f] require two structural components (a compensated GaN layer and a gate contact) and one positional component (the compensated GaN layer must be above the barrier layer and below the gate contact).

#### i. Structural Component: "compensated GaN layer"

While the parties have competing constructions for "compensated GaN," there is no dispute that "compensated GaN" is at least passivated and resistive. *See e.g.*, Tr. (Lidow) 103:13-19; Tr.

(Schubert) 433:7-22; 435:8-13; Tr. (Lebby) 858:5-15. *Uemoto*, therefore, indisputably discloses "a compensated GaN layer" under any construction. Tr. (Lebby) 876:15-878:7.

Uemoto discloses a "third nitride semiconductor layer 15" including "a high resistive region 15b in which Mg is not activated." RX-0073 ¶¶ [0033], [0063]; Tr. (Lebby) 876:17-877:3. Uemoto explains that third nitride semiconductor layer 15 is Mg-doped and that 15b includes Mg passivated with H to inactivate the Mg and make the layer highly resistive. RX-0073 ¶¶ [0033], [0049], [0063]; Tr. (Lebby) 877:16-25.

EPC admits 15b is "p-doped, passivated and a resistive region," and therefore is indisputably "compensated GaN," as claimed. Tr. (Schubert) 960:4-10; 960:20-23. Indeed, Dr. Schubert testified that *Uemoto*'s "layer 15b is gallium nitride, contains magnesium and hydrogen, is passivated, and is non-conductive. So in that sense, it meets the claim term 'compensated gallium nitride." Tr. (Schubert) 1033:21-1034:7. There is no dispute, *Uemoto*'s region 15b is "compensated gallium nitride." *Id.* 964:1-7; 1033:21-1034:7.

#### ii. Structural Component: "gate contact"

Uemoto discloses a "gate contact." Tr. (Lebby) 878:9-879:14. Uemoto discloses "gate electrode 20" that is located above semiconductor layer 15 (including high resistive region 15b). RX-0073 ¶¶ [0034], [0056], [0062]; Tr. (Lebby) 878:9-879:14. EPC does not dispute that Uemoto's gate electrode 20 is the "gate contact" as recited in [1f]. See Tr. (Schubert) 965:3-13; 966:21-24.

# iii. Positional Component: compensated GaN layer "above the barrier layer"; and gate contact "above the compensated GaN layer"

*Uemoto* discloses layer 15 is a GaN layer and "[o]n the second nitride semiconductor layer 14," the barrier. RX-0073 ¶¶ [0033], [0054]; Tr. (Lebby) 877:5-12. Figure 7, annotated below, shows that *Uemoto*'s **layer 15b** (compensated GaN layer) is above the **semiconductor layer 14**

(barrier layer); and gate electrode 20 is above layer 15b (compensated GaN layer). Tr. (Lebby) 878:9-879:14.

FIG. 7

RDX-0013.53; RX-0073 Fig. 7 (annotated)

EPC's only dispute with the entirety of the *Uemoto* ground is that *Uemoto* fails to disclose the positional requirement of "a gate contact above the compensated GaN layer." Tr. (Schubert) 963:5-16; *see id.* 1034:4-25 (Dr. Schubert admitting *Uemoto*'s 15b is the claimed "compensated GaN" but alleging it is not positioned as in the claim).

**First**, EPC is wrong. *Uemoto*'s "gate contact [is] above the compensated GaN layer;" specifically, region 15b. Tr. (Lebby) 878:11-879:14. In the '294 patent, the claims use the term "above" as a preposition, to convey the spatial relationship between the claimed layers—meaning no more than "higher than." JX-0014 5:11-6:27; *See EMI Grp. N. Am., Inc. v. Cypress Semiconductor Corp.*, 68 F. Supp. 2d 421, 431 (D. Del. 1999) (construing "above" as "higher than, but not necessarily directly in contact with"); *Terlep v. Brinkman Corp.*, Case No. 02-cv-5127, 2004 U.S. Dist. LEXIS 28453, at \*12 (W.D. Ark. Mar. 23, 2004) (construing "above" as "in a higher place than or overhead").

As shown below in *Uemoto*'s FIG. 7, *Uemoto* meets the positional requirements of claim 1 because *Uemoto*'s gate electrode 20 is "above" (i.e., higher than) region 15b (the compensated GaN). Tr. (Lebby) 878:24-879:14.

**RDX-0013.53; RX-0073 FIG. 7 (annotated)**

**Second**, EPC's interpretation requiring direct contact between the gate contact and compensated GaN layer to satisfy the "above" limitation is wrong. Previous constructions of the term "above" rejected EPC's requirement. *Infection Prevention Techs.*, *LLC v. Lumalier Corp.*, Case No. 10-cv-12371, 2012 WL 3248232, at \*20 (E.D. Mich. Aug. 8, 2012) (adopting construction of "above" based on plain meaning and rejecting modifications based on horizontal and vertical alignment).

Third, even as voicing disagreement with the positioning disclosed in *Uemoto*, Dr. Schubert admitted *Uemoto*'s gate contact is above its compensated GaN layer 15b, admitting that "a sliver of region 15B" is under gate electrode 20. Tr. (Schubert) 965:3-19; *see also id.* 966:21-24. Or, phrased differently, admitting that gate electrode 20 is above a sliver of region 15b—thus admitting the claim's position requirement is met or at least suggested and rendered obvious.

KDX-0013.54, KX-0075 FTG. 7 (200mcu iii anu annotatet

# g. [2p]: The transistor of claim 1

As discussed in Section II.B.4.a-f, a POSITA would have recognized that *Uemoto* obviates all limitations of claim 1, which are also included in claim 2. *Supra* § II.B.4.a-f.

# h. [2a]: wherein the compensated GaN layer contains acceptor type dopant atoms passivated with hydrogen

*Uemoto* discloses [2a] because *Uemoto* teaches that "acceptor type dopant atoms passivated with hydrogen" in region 15b of semiconductor layer 15, as claim 2 recites. Tr. (Lebby) 880:16-882:1. *Uemoto* discloses a layer 15 doped with magnesium, which a POSITA would have understood to be an acceptor because it is a p-type impurity. RX-0073 ¶ [0046]; Tr. (Lebby) 880:19-881:5. *Uemoto* also explains that, in layer 15 (including specifically **region 15b**), hydrogen inactivates/passivates the magnesium: "hydrogen from the hydrogen diffusion film 17 is supplied during a thermal treatment for selectively inactivating impurities." RX-0073 ¶¶ [0063], [0049]; Tr. (Lebby) 881:10-19. EPC does not dispute that region 15b is "passivated with hydrogen." Tr. (Schubert) 964:1-5; *see also id.* 961:22-962:6. Therefore, *Uemoto* discloses element [2a].

#### i. [3p]: The transistor of claim 2

As discussed in Section II.B.4.g-h, a POSITA would have recognized that *Uemoto* discloses all elements of claim 2, which are also included in claim 3. *Supra* § II.B.4.g-h.

# j. [3a]: where the acceptor type atoms are selected from the group consisting of Mg, Zn, Be and Ca

*Uemoto* discloses [3a] by describing *Uemoto*'s acceptor type dopant atoms are magnesium, disclosing that "layer 15 is . . . doped with magnesium (Mg)." RX-0073 ¶ [0033]; Tr. (Lebby) 882:3-11. EPC does not dispute that *Uemoto* discloses that layer 15b is "doped with magnesium" and "passivated with hydrogen." Tr. (Schubert) 964:1-5; *see also id.* 961:22-962:6.

*Uemoto*, therefore, discloses that region 15b is doped with Mg acceptors.

# 5. Beach 189 Ground: Beach 189 Anticipates Claim 1, and Beach 189 in View of Kigami Renders Claims 2 and 3 Obvious

# a. Claim 1 is anticipated by *Beach189*

# i. [1pre]: A column III Nitride transistor

To the extent [1pre] is limiting, *Beach189* discloses it. Tr. (Lebby) 854:4-13; RDX-0013.19.

Beach 189 discloses a "III-nitride power semiconductor device includes a drain electrode, a source electrode and a gate electrode disposed between the drain electrode and the source electrode" and that the "gate electrode controls the current between the source electrode and the drain electrode." RX-0011 ¶¶ [0002]-[0003]. A POSITA would have understood such a device is a transistor. Tr. (Lebby) 854:9-13. EPC does not dispute Beach 189 discloses [1pre].

EPC wrongly asserts, however, that *Beach189* discloses a hypothetical non-functioning enhancement-mode transistor. Tr. (Lebby) 856:11-18; Tr. (Schubert) 948:22-5. No evidence supports EPC's allegation, and EPC is wrong for three reasons.

**First**, the claim does not require any particular functionality, let alone an enhancement-mode or a depletion-mode, but is instead drawn to a structure of a transistor. JX-0014 Claim 1. In fact, as Dr. Lebby explained, *Beach189* discloses both an enhancement-mode and a depletion-mode device. Tr. (Lebby) 936:7-937:2; RX-0011 ¶ [0044].

**Second**, an anticipatory prior art reference does not need to be fully functional to qualify as prior art; indeed, a prior art reference need not work and may even be inoperative. *Metso*, 526 F. App'x at 995.

**Third**, as explained in Sections II.B.5.a.vi and viii below, *Beach189* device would function properly as an enhancement-mode device. RDX-0100.4-6; Tr. (Lebby) 937:4-944:3.

# ii. [1a]: a substrate

Beach189 discloses [1a]. Tr. (Lebby) 854:15-23; RDX-0013.20. EPC does not dispute Beach189 discloses [1a]. Tr. (Lebby) 856:11-18.

Beach 189 discloses a "support body 12 [that] is a combination of a substrate material." RX-0011 ¶ [0041], [0025]. Figure 4 below highlights the substrate in support body 12.

RDX-0013.20; RX-0011 Fig. 4 (annotated)

## iii. [1b]: a set of III-N transition layers above the substrate

Beach189 discloses [1b]. Tr. (Lebby) 854:24-855:9; RDX-0013.21. EPC does not dispute Beach189 discloses [1b]. Tr. (Lebby) 856:11-18.

Beach189 discloses [1b] because its transistors include "buffer layers" positioned over the substrate. RX-0011 ¶¶ [0041]-[0042]. Beach189 specifies the buffer layers can be implemented with "a multi-layer or graded transitional III-nitride semiconductor body may also be used as a

buffer layer without deviating from the scope and the spirit of the present invention." RX-0011 ¶ [0042]. Figure 4 below shows *Beach189*'s buffer layers above the substrate.

**RDX-0013.21; RX-0011 Fig. 4 (annotated)**

iv. [1c]: a III-N buffer layer above the set of transition layers

Beach189 discloses [1c]. Tr. (Lebby) 855:11-22; RDX-0013.22. EPC does not dispute Beach189 discloses [1c]. Tr. (Lebby) 856:11-18.