# **Computer Busses**

COLLEGE PATH, MARKELAND

· DEC 11 2000

EMORITETE N. 11 TO SOAL EURISTINO DI SORV

# **Computer Busses**

William Buchanan, BSc (Hons), CEng, PhD Napier University, Edinburgh, UK

A member of the Hodder Headline Group LONDON

Co-published in North America by CRC Press Boca Raton • New York • Washington, D.C. First published in Great Britain in 2000 by Arnold, a member of the Hodder Headline Group, 338 Euston Road, London NW1 3BH

### http://www.arnoldpublishers.com

Co-published in North America by CRC Press LLC, 2000 N.W. Corporate Blvd., Boca Raton, Florida 33431 USA

## © 2000 William Buchanan

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronically or mechanically, including photocopying, recording or any information storage or retrieval system, without either prior permission in writing from the publisher or a licence permitting restricted copying. In the United Kingdom such licences are issued by the Copyright Licensing Agency: 90 Tottenham Court Road. London W1P 0LP.

Whilst the advice and information in this book are believed to be true and accurate at the date of going to press, neither the author nor the publisher can accept any legal responsibility or liability for any errors or omissions that may be made.

British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

Library of Congress Cataloging-in-Publication Data

A catalog record for this book is available from the Library of Congress

ISBN 0 340 74076 0 ISBN 0 8493 0825 9 (CRC Press)

12345678910

Printed and bound in Great Britain by J W Arrowsmith Ltd, Bristol

What do you think about this book? Or any other Arnold title? Please send your comments to feedback.arnold@hodder.co.uk

# **Table of Contents**

|   | Prefa | ce                              | xiii  |

|---|-------|---------------------------------|-------|

| 1 | INT   | RODUCTION                       | 1     |

| • | 1.1   | Pre-PC Development              | 1     |

|   | 1.2   | 8008/8080/8085                  | . 6   |

|   | 1.3   | 8086/8088                       | 13    |

|   | 1.4   | 80186/80188                     | 19    |

|   | 1.5   | 80286                           | 20    |

|   | 1.6   | Post-PC development             | 21    |

|   | 1.7   | Exercises                       | 36    |

|   | 1.8   | Notes from the author           | 40    |

|   | 1.9   | DEC                             | 45    |

|   | 1.10  | Open .v. closed systems         | 47    |

|   | 1.11  | RIP, Sinclair Research          | 48    |

|   | 1.12  | How to miss a market            | . 48  |

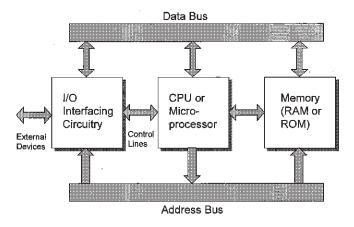

| 2 | BUS   | SSES, INTERRUPTS AND PC SYSTEMS | 49    |

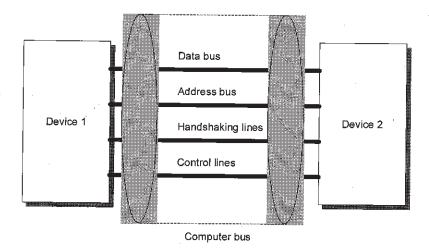

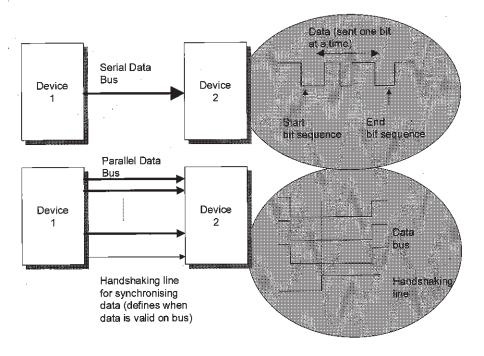

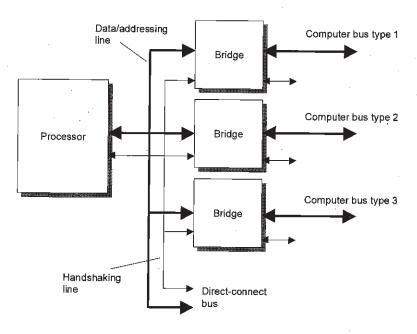

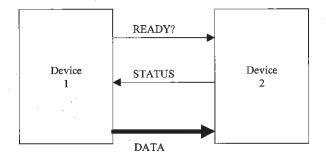

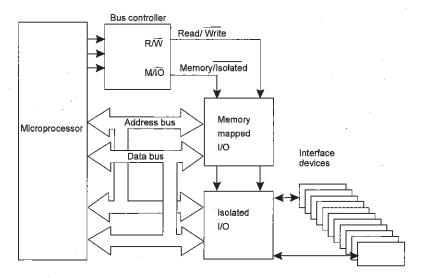

|   | 2.1   | Busses                          | 49    |

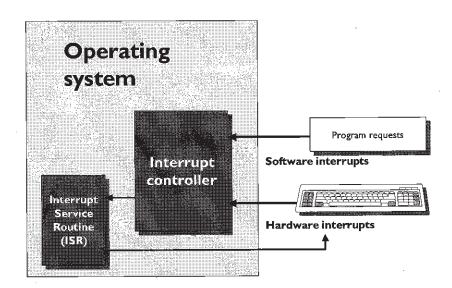

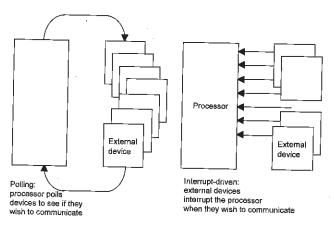

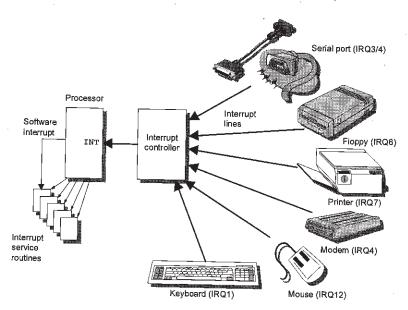

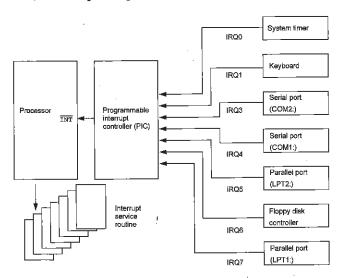

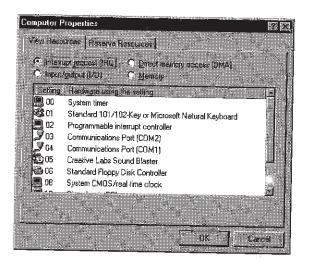

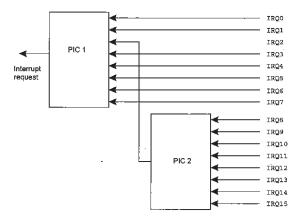

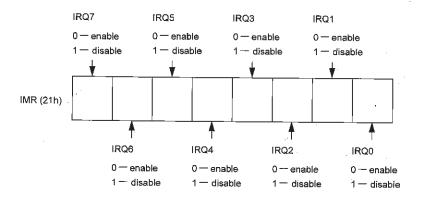

|   | 2.2   | Interrupts                      | 61    |

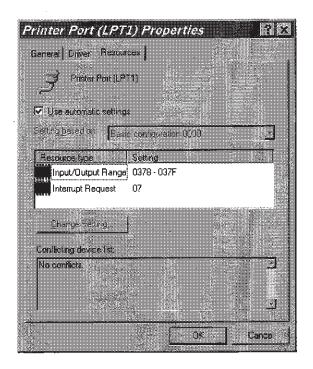

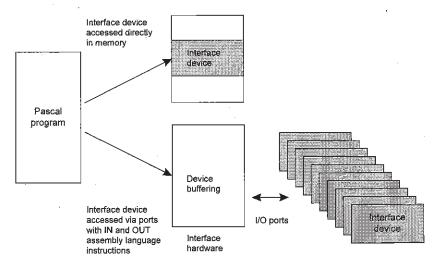

|   | 2.3   | Interfacing                     | 69    |

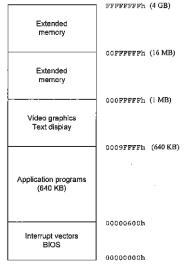

|   | 2.4   | PC Systems                      | 76    |

|   | 2.8   | Practical PC system             | 77    |

|   | 2.5   | Exercises                       | 79    |

|   | 2.6   | Notes from the author           | 82    |

| 3 | INT   | ERFACING STANDARDS              | 85    |

|   | 3.1   | Introduction                    | 85    |

|   | 3.2   | PC bus                          | 85    |

|   | 3.3   | ISA bus                         | 87    |

|   | 3.4   | Other legacy busses             | 91    |

|   | 3.5   | Comparison of different types   | 92    |

|   | 3.6   | Exercises                       | 93    |

|   | 3.7   | Summary of interface bus types  | 95    |

|   | 3.8   | The fall of the MCA bus         | 97    |

|   | 3.9   | Notes from the author           | 98    |

| 4 | PCI   | BUS                             | 103   |

|   | 4.1   | Introduction                    | 103   |

|   | 4.2   | PCI operation                   | 106   |

|   | 4.3   | Bus arbitration                 | 109   |

|   | 4.4   | Other PCI pins                  | . 110 |

|   | 45    | Configuration address space     | 110   |

| vi |            |                                               | Computer busses |

|----|------------|-----------------------------------------------|-----------------|

|    | 4.6        | I/O addressing                                | 112             |

|    | 4.7        | Exercises                                     | 116             |

| •  | 4.8        | Example manufacturer and plug-and-play IDs    | 118             |

|    | 4.9        | Notes from the author                         | 119             |

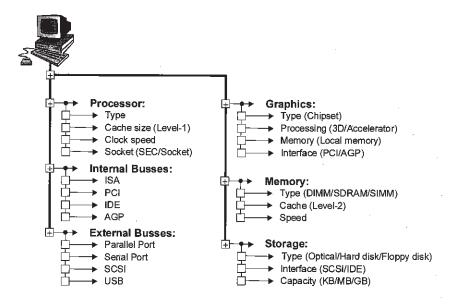

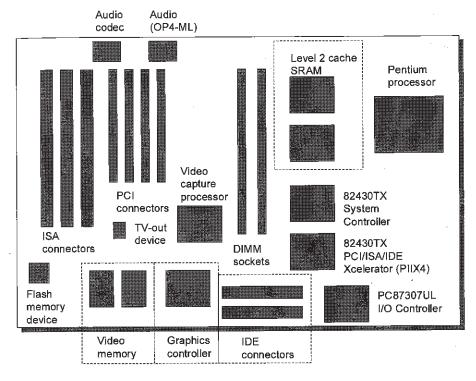

| 5  |            | THERBOARD DESIGN                              | 121             |

|    | 5.1        | Introduction                                  | 121             |

|    | 5.2        | TX motherboard                                | 132             |

|    | 5.3        | Exercises                                     | 136             |

|    | 5.4        | Notes from the author                         | 137             |

| 6  |            | AND MASS STORAGE                              | 139             |

|    | 6.1        | Introduction                                  | 139             |

|    | 6.2        | Tracks and sectors                            | 139             |

|    | 6.3        | Floppy disks                                  | 140             |

|    | 6.4        | Fixed disks                                   | 141             |

|    | 6.5<br>6.6 | Drive specifications                          | 142             |

|    | 6.7        | Hard disk and CD-ROM interfaces IDE interface | 142             |

|    | 6.8        | IDE interface IDE communication               | 143             |

|    | 6.9        | Optical storage                               | 144             |

|    | 6.10       | Magnetic tape                                 | 150             |

|    | 6.11       | Exercises                                     | 153             |

|    |            | Notes from the author                         | . 155<br>156    |

| 7  | SCS        | SI                                            | 157             |

|    | 7.1        | Introduction                                  | 157             |

|    | 7.2        | SCSI types                                    | 157             |

|    | 7.3        | SCSI interface                                | 159             |

|    | 7.4        | SCSI operation                                | 162             |

|    | 7.5        | SCSI pointers                                 | 164             |

|    | 7.6        | Message system description                    | 165             |

|    | 7.7        | SCSI commands                                 | 167             |

|    | 7.8        | Status                                        | 169             |

|    | 7.9        |                                               | 171             |

|    | 7.10       | Notes from the author                         | 172             |

| 8  | PCN        |                                               | 173             |

|    | 8.1        | Introduction                                  | 173             |

|    | 8.2        | PCMCIA signals                                | 173             |

|    | 8.3        | PCMCIA registers                              | 175             |

|    | 8.4<br>8.5 | Exercises Notes from the color                | 179             |

|    | 6.5        | Notes from the author                         | 179             |

| 9  |            | AND FIREWIRE                                  | 181             |

|    |            | Introduction                                  | 181             |

|    | 9.2        | USB                                           | 182             |

| Тирге | oj conten | ius .                                     | . VII |

|-------|-----------|-------------------------------------------|-------|

|       | 9.3       | Firewire                                  | 186   |

|       | 9.4       | Exercises                                 | 190   |

|       | 9.5       | Notes from the author                     | 190   |

| 10    | GA        | MES PORT, KEYBOARD AND MOUSE              | 191   |

|       | 10.1      | Introduction                              | 191   |

|       | 10.2      | Games port                                | 191   |

|       | 10.3      | Keyboard                                  | 195   |

| **    | 10.4      | Mouse and keyboard interface              | 198   |

|       | 10.5      | Mouse                                     | 199   |

|       | 10.6      |                                           | 200   |

|       | 10.7      | Notes from the author                     | 201   |

| 11    | AG        | <b>P</b>                                  | 203   |

|       | 11.1      | Introduction                              | 203   |

|       | 11.2      | PCI and AGP                               | 204   |

|       | 11.3      | Bus transactions                          | 205   |

|       | 11.4      | Pin description                           | 205   |

|       | 11.5      | AGP master configuration                  | 208   |

|       | 11.6      | Bus commands                              | 209   |

|       | 11.7      | Addressing modes and bus operations       | 210   |

|       | 11.8      | Register description                      | 210   |

|       | 11.9      | Exercises                                 | 215   |

|       | 11.10     | 0 Notes from the author                   | 215   |

| 12    | FIB       | RE CHANNEL                                | 217   |

|       | 12.1      | Introduction                              | 217   |

|       | 12.2      | Comparison                                | 217   |

|       | 12.3      | Fibre channel standards                   | 218   |

|       | 12.4      | Cables, hubs, adapters and connectors     | 219   |

|       | 12.5      | Storage Devices and storage area networks | 221   |

|       | 12.6      | Networks                                  | 221   |

|       | 12.7      | Exercises                                 | 222   |

|       | 12.8      | Notes from the author                     | 222   |

| 13    | RS-       | 232                                       | 223   |

|       | 13.1      | Introduction                              | 223   |

|       | 13.2      | Electrical characteristics                | 223   |

|       | 13.3      | Communications between two nodes          | 228   |

|       | 13.4      |                                           | .233  |

| 3     | 13.5      | RS-232 programs                           | 237   |

| ,     | 13.6      | Exercises                                 | 241   |

|       | 13.7      | Notes from the author                     | 246   |

| 14    | RS-       | 422, RS-423 AND RS-485                    | 247   |

|       | 14.1      | Introduction                              | 247   |

|       |           | RS-485 (ISO 8482)                         | 247   |

| viii  |                                           | Computer busses |

|-------|-------------------------------------------|-----------------|

|       | 14.3 Line drivers                         | 240             |

|       | 14.4 RS-232/485 converter                 | 249             |

|       | 14.5 Exercises                            | 250             |

|       | 14.6 Note from the author                 | 251<br>251      |

| 15    | MODEMS                                    |                 |

|       | 15.1 Introduction                         | 253             |

|       | 15.2 RS-232 communications                | 253             |

|       | 15.3 Modern standards                     | 254             |

|       | 15.4 Modem commands                       | 255             |

|       | 15.5 Modem set-ups                        | 256             |

|       | 15.6 Modem indicator                      | 258             |

|       | 15.7 Profile viewing                      | 260             |

|       | 15.8 Test modes                           | . 260           |

|       | 15.9 Digital modulation                   | 261             |

|       | 15.10 Typical modems                      | 264             |

|       | 15.11 Fax transmission                    | 265             |

|       | 15.12 Exercises                           | 267             |

|       | 15.13 Notes from the author               | 268<br>269      |

| 16    | PARALLEL PORT                             |                 |

|       | 16.1 Introduction                         | 271             |

|       | 16.2 PC connections                       | 271             |

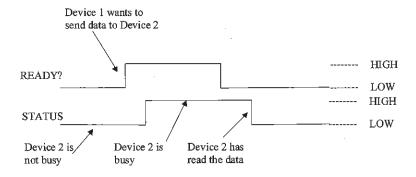

|       | 16.3 Data handshaking                     | 271             |

|       | 16.4 I/O addressing                       | 272             |

|       | 16.5 Interrupt-driven parallel port       | 275             |

|       | 16.6 Exercises                            | 279             |

|       | 16.7 Notes from the author                | 284<br>287      |

| 17    | ENHANCED PARALLEL PORT                    |                 |

| • • • | 17.1 Introduction                         | 289             |

|       | 17.1 Introduction 17.2 Compatibility mode | 289             |

|       | 17.2 Companionity mode  17.3 Nibble mode  | 289             |

|       | 17.4 Byte mode                            | 290             |

|       | 17.5 EPP                                  | 293             |

|       | 17.6 ECP                                  | 294             |

|       | 17.7 Exercises                            | 296             |

|       | 17.8 Note from the author                 | 300<br>300      |

| 18    | MODBUS                                    | 300             |

| 10    |                                           | 301             |

|       | T                                         | 301             |

|       |                                           | 307             |

|       | 8                                         | 309             |

|       |                                           | 311             |

|       | 18.5 Notes from the author                | 312             |

| Table o | of contents |                             |   |                                       | ix  |

|---------|-------------|-----------------------------|---|---------------------------------------|-----|

| 19      | FIEL        | DBUS                        |   |                                       | 313 |

|         | 19.1        | Introduction                |   |                                       | 313 |

|         | 19.2        | Fieldbus types              |   |                                       | 313 |

|         |             | FOUNDATION Fieldbus         |   |                                       | 316 |

|         | 19.4        | Exercises                   |   | •                                     | 323 |

|         | 19.5        | Notes from the author       |   |                                       | 323 |

| 20      | WOF         | RLDFIP                      |   | •                                     | 325 |

|         |             | Introduction                |   |                                       | 325 |

|         |             | Physical layer              |   | · · · · · · · · · · · · · · · · · · · | 325 |

|         |             | Data link layer             |   |                                       | 326 |

|         |             | Exercises                   |   |                                       | 330 |

|         | 20.5        | Notes from the author       |   |                                       | 331 |

| 21      | CAN         | BUS                         |   |                                       | 333 |

|         | 21.1        | Introduction                |   |                                       | 333 |

|         |             | CAN physical                |   |                                       | 335 |

|         |             | CAN bus basics              |   |                                       | 336 |

|         |             | Message transfer            |   |                                       | 337 |

|         |             | Fault confinement           |   |                                       | 340 |

|         | 21.6        | Bit timing                  |   |                                       | 341 |

|         |             | CAN open                    |   | 1                                     | 342 |

|         |             | Exercises                   |   |                                       | 342 |

|         | 21.9        | Notes from the author       |   |                                       | 343 |

| 22      | IEEE        | -488, VME AND VXI           |   |                                       | 345 |

|         | 22.1        | Introduction                |   |                                       | 345 |

|         | 22.2        | IEEE-488 bus                |   |                                       | 345 |

|         | 22.3        | VME bus                     |   |                                       | 348 |

|         | 22.4        | VXI bus                     |   |                                       | 349 |

|         | 22.5        | Exercises                   |   |                                       | 352 |

|         | 22.6        | Notes from the author       |   |                                       | 353 |

| 23      | TCP         | /IP                         |   |                                       | 355 |

|         | 23.1        | Introduction                |   |                                       | 355 |

|         | 23.2        | TCP/IP gateways and hosts   |   |                                       | 356 |

|         | 23.3        | Function of the IP protocol |   |                                       | 356 |

|         | 23.4        | Internet datagram           |   | 9 - <b>1</b>                          | 357 |

|         | 23.5        | ICMP                        | • |                                       | 359 |

|         | 23.6        | TCP/IP internets            |   |                                       | 362 |

|         | 23.7        | Domain name system          |   |                                       | 366 |

|         |             | Internet naming structure   |   |                                       | 367 |

|         |             | Domain name server          |   |                                       | 368 |

|         |             | Bootp protocol              |   |                                       | 369 |

|         |             | Example network             |   |                                       | 371 |

|         | 23.12       |                             |   |                                       | 373 |

|         | 23.13       | IP multicasting             |   |                                       | 373 |

ix

|    |                                                                                                                 | Computer busse |

|----|-----------------------------------------------------------------------------------------------------------------|----------------|

|    | 23.14 Exercises                                                                                                 | 37:            |

|    | 23.15 Notes from the author                                                                                     | 37             |

|    | 23.16 Additional material                                                                                       | 378            |

| 24 | TCP AND UDP                                                                                                     | 385            |

|    | 24.1 Introduction                                                                                               | 385            |

|    | 24.2 Transmission control protocol                                                                              | 385            |

|    | 24.3 UDP                                                                                                        | 389            |

|    | 24.4 TCP specification                                                                                          | 390            |

|    | 24.5 TCB parameters                                                                                             | 392            |

|    | 24.6 Connection states                                                                                          | 392            |

|    | 24.7 Opening and closing a connection                                                                           | 395            |

|    | 24.8 TCP user commands                                                                                          | 397            |

|    | 24.9 WinSock                                                                                                    | 399            |

|    | 24.10 Visual Basic socket implementation                                                                        | 408            |

|    | 24.11 Exercises                                                                                                 | 414            |

|    | 24.12 TCP/IP services reference                                                                                 | 416            |

|    | 24.13 Notes from the author                                                                                     | 416            |

| 25 | NETWORKS                                                                                                        | 440            |

|    | 25.1 Introduction                                                                                               | 419            |

|    | 25.2 Network topologies                                                                                         | 419            |

|    | 25.3 OSI model                                                                                                  | 421            |

|    | 25.4 Routers, bridges and repeaters                                                                             | 424            |

|    | 25.5 Network cable types                                                                                        | 426            |

|    | 25.6 Exercises                                                                                                  | 429            |

|    | 25.7 Notes from the author                                                                                      | 431<br>432     |

| 26 | ETHERNET                                                                                                        |                |

| 20 | 26.1 Introduction                                                                                               | 435            |

|    | 26.2 IEEE standards                                                                                             | 435            |

|    | 26.3 Ethornot modinarios                                                                                        | 436            |

|    | <ul> <li>26.3 Ethernet – media access control (MAC) layer</li> <li>26.4 IEEE 802.2 and Ethernet SNAP</li> </ul> | . 437          |

|    | 26.5 OSI and the IEEE 802.3 standard                                                                            | 439            |

|    | 26.6 Ethernet transceivers                                                                                      | 441            |

|    | 26.7 Ethernet types                                                                                             | 442            |

|    | 26.8 Twisted-pair hubs                                                                                          | 443            |

|    | 26.9 100 Mbps Ethernet                                                                                          | 445            |

|    | 26.10 Comparison of fast Ethernet other technologies                                                            | 445            |

|    | 26.11 Switches and switching hubs                                                                               | 450            |

|    | 26.12 Network interface card design                                                                             | 451            |

|    | 26.13 Gigabit Ethernet                                                                                          | 453            |

|    | 26.14 Exercises                                                                                                 | 457            |

|    | 26.15 Ethernet crossover connections                                                                            | 462            |

|    | 26.16 Notes from the author                                                                                     | 464<br>465     |

| 7  | DC 222 PDCCDAMMING                                                                                              | ,              |

| 27 | RS-232 PROGRAMMING USING VISUAL BASIC 27.1 Introduction                                                         | 467            |

|    | 21.1 Introduction                                                                                               | 467            |

| Table ( | of content. |                                                   | Л     |

|---------|-------------|---------------------------------------------------|-------|

|         | 27.2        | Properties                                        | 467   |

|         | 27.3        | Events                                            | 473   |

|         | 27.4        | Example program                                   | 474   |

|         | 27.5        | Error messages                                    | 475   |

|         | 27.6        | RS-232 polling                                    | 476   |

|         | 27.7        | Exercises                                         | 477   |

| 28      | INTE        | ERRUPT-DRIVEN RS-232                              | 479   |

|         | 28.1        | Interrupt-driven RS-232                           | 479   |

|         | 28.2        | DOS-based RS-232 program                          | 479   |

|         | 28.3        | Exercises                                         | 486   |

| Α       | PC I        | PROCESSORS                                        | 489   |

|         | A.1         | Introduction                                      | 489   |

|         | A.2         | 8086/88                                           | 490   |

|         | A.3         | 80386/80486                                       | 495   |

|         | A.4         | Pentium/Pentium Pro                               | 501   |

|         | A.5         | Exercises                                         | . 505 |

| В       | VES         | SA VL-LOCAL BUS                                   | 509   |

| С       | МОІ         | DEM CODES                                         | 511   |

| _       | C.1         | AT commands                                       | 511   |

|         | C.2         | Result codes                                      | 513   |

|         | C.3         | S-registers                                       | 514   |

| D       | RED         | DUNDANCY CHECKING                                 | 519   |

|         | D.1         | Cyclic redundancy check (CRC)                     | 519   |

|         | D.2         | Longitudinal/vertical redundancy checks (LRC/VRC) | 523   |

| E       | ASC         | CII CHARACTER CODE                                | 525   |

|         | E.1         |                                                   | 525   |

|         | E.2         | Extended ASCII code                               | 527   |

| F       | OH          | CK REFERENCE                                      | 529   |

| •       | F.1         | Notes from the author                             | 531   |

| G       | ISD         | Ni                                                | 533   |

| 3       | G.1         | Introduction                                      | 533   |

|         | G.1<br>G.2  | ISDN channels                                     | 534   |

|         | G.2<br>G.3  | ISDN physical layer interfacing                   | 535   |

|         | G.3<br>G.4  | ISDN data link layer                              | 538   |

|         | G.5         | ISDN network layer                                | 541   |

|         | G.6         | Speech sampling                                   | 543   |

|         | G.7         | Exercises                                         | 544   |

|         |             |                                                   |       |

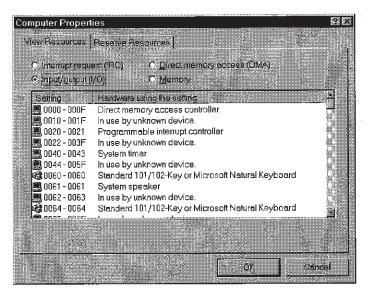

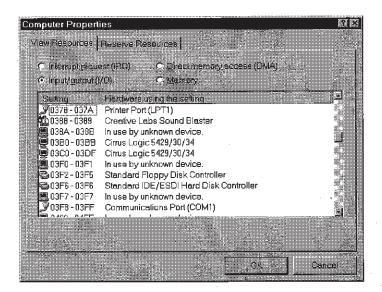

| Н | MI    | CROSOFT WINDOWS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 547        |

|---|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   | H.1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54         |

|   | H.2   | Windows registry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 548        |

|   | H.3   | Device drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55(        |

|   | H.4   | Configuration manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 551        |

|   | H.5   | Virtual machine manager (VMM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 552        |

|   | H.6   | Multiple file systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 552<br>555 |

|   | H.7   | Core system components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 557<br>557 |

|   | H.8   | Multitasking and threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 559        |

|   | H.9   | Plug-and-play process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 561        |

|   | H.10  | - The state of the | 561        |

|   | H.11  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 564        |

|   | H.12  | Fundamentals of Operating Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 565        |

|   | H.13  | Exercises                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 567        |

| 1 | HDI   | LC .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 500        |

|   | I.1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 569        |

|   | I.2   | HDLC protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 569        |

|   | I.3   | Transparency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 570        |

|   | I.4   | Flow control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 574        |

|   | 1.5   | Derivatives of HDLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 574        |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 576        |

| J | EXA   | MPLE WINSOCK CODE FOR VISUAL BASIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|   | J.1   | My client (myClient.frm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 579        |