### UNITED STATES PATENT AND TRADEMARK OFFICE

### **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

## BOE Technology Group Co., Ltd. Petitioner

v.

Optronic Sciences LLC Patent Owner

#### Inter Partes Review No.: IPR2025-00239

## DECLARATION OF DR. R. JACOB BAKER IN REGARDING CLAIMS 1-21 OF U.S. PATENT NO. 8,502,757

I hereby declare under penalty of perjury under the laws of the United States of America that the following is true and correct, and that all statements made of my own knowledge are true and that all statements made on information and belief are believed to be true. I understand that willful false statements are punishable by fine or imprisonment or both under Section 1001 of Title 18 of the United States Code.

<u>March 7, 2025</u> Date

A.J. Date

Dr. R. Jacob Baker

# TABLE OF CONTENTS

#### I. BACKGROUND AND QUALIFICATION ......1 II. A. Β. C. III. DOCUMENTS AND OTHER MATERIALS RELIED UPON ......10 IV. V. RELEVANT PATENT LAW AND LEGAL STANDARDS......11 A. Date of Invention......11 Β. C. Obviousness......12 D. Section 112(f) Means Plus Function ......16 E. F. Section 112 Definiteness......17 G. VI A. Overview of the 757 patent's File History......19 Β. C. Claim Construction Under 37 C.F.R. § 42.104(b)(3) ......20 D. a. b. c. d. e. f. g.

Page

|       |                                                                                  | h. Abridged Claim Listing Summary               | .28 |  |  |

|-------|----------------------------------------------------------------------------------|-------------------------------------------------|-----|--|--|

|       |                                                                                  | a. Primary Construction                         | .29 |  |  |

|       |                                                                                  | b. Alternative Construction                     | .31 |  |  |

| VII.  | VII. OVERVIEW OF THE PRIOR ART REFERENCES                                        |                                                 |     |  |  |

|       | A.                                                                               | EX1004 – Kim406                                 | .31 |  |  |

|       | B.                                                                               | EX1005 – Kim730                                 | .31 |  |  |

|       | C.                                                                               | EX1006 – Senda                                  | .31 |  |  |

|       | D.                                                                               | Analogous Art                                   | .31 |  |  |

| VIII. | GRO                                                                              | UND 1: CLAIMS 1-12 AND 14-19 ARE ANTICIPATED BY |     |  |  |

|       | KIM4                                                                             | 406                                             | .32 |  |  |

|       | A.                                                                               | Claim 1                                         | .32 |  |  |

|       | В.                                                                               | Claim 2:                                        | .48 |  |  |

|       | C.                                                                               | Claim 3:                                        | .48 |  |  |

|       | D.                                                                               | Claim 4:                                        | .49 |  |  |

|       | E.                                                                               | Claim 5:                                        | .49 |  |  |

|       | F.                                                                               | Claim 6:                                        | .49 |  |  |

|       | G.                                                                               | Claim 7:                                        | .49 |  |  |

|       | H.                                                                               | Claim 8:                                        | .49 |  |  |

|       | I.                                                                               | Claim 9:                                        | .50 |  |  |

|       | J.                                                                               | Claim 10:                                       | .50 |  |  |

|       | K.                                                                               | Claim 11:                                       | .50 |  |  |

|       | L.                                                                               | Claim 12:                                       | .50 |  |  |

|       | M.                                                                               | Claim 14:                                       | .50 |  |  |

|       | N.                                                                               | Claim 15:                                       | .51 |  |  |

|       | О.                                                                               | Claim 16:                                       | .51 |  |  |

|       | P.                                                                               | Claim 17:                                       | .51 |  |  |

|       | Q.                                                                               | Claim 18:                                       | .59 |  |  |

|       | R.                                                                               | Claim 19:                                       | .60 |  |  |

| IX.   | GROUND 2: CLAIMS 1-20 ARE OBVIOUS OVER THE<br>COMBINATION OF KIM406 AND KIM73061 |                                                 |     |  |  |

|     | A.  | Combination Rationale6                    |    |  |  |

|-----|-----|-------------------------------------------|----|--|--|

|     | B.  | Claims 13, 20                             |    |  |  |

|     | C.  | Claims 1-20                               |    |  |  |

| X.  | GRO | 64                                        |    |  |  |

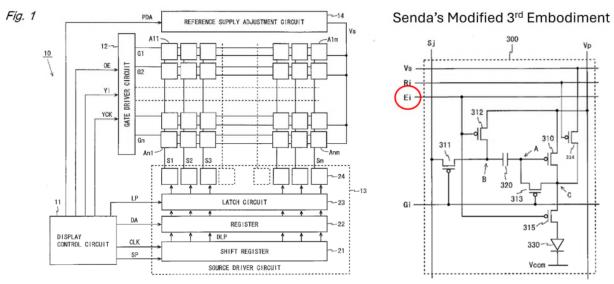

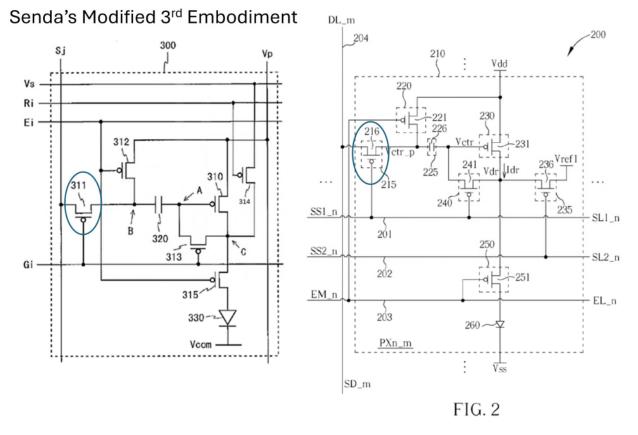

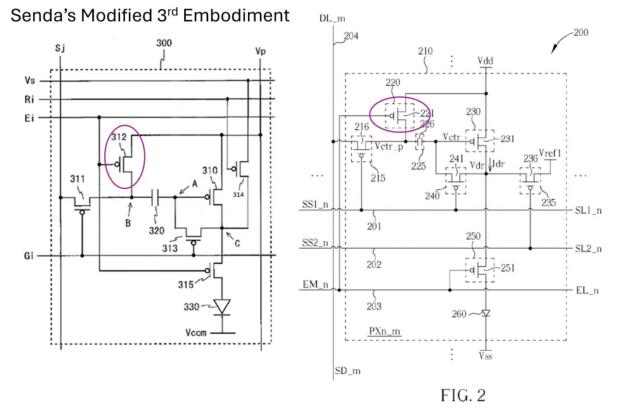

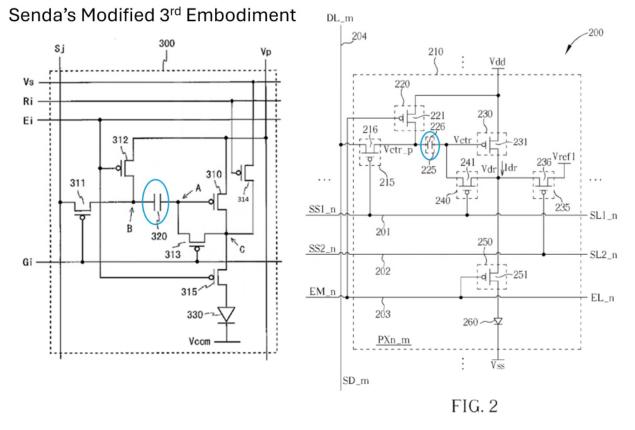

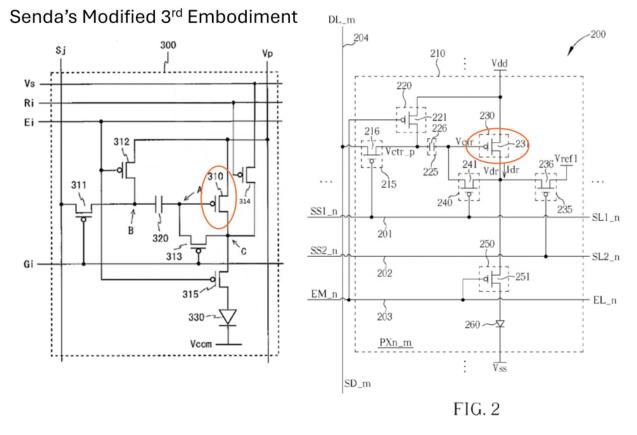

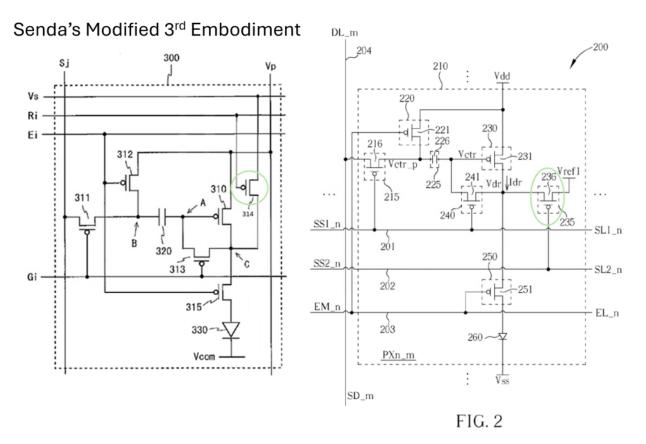

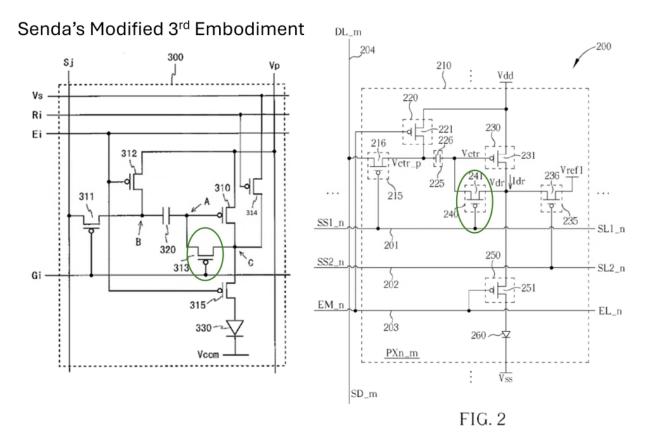

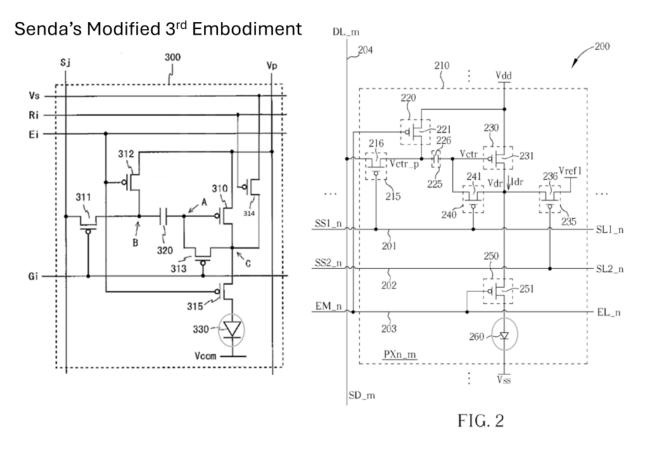

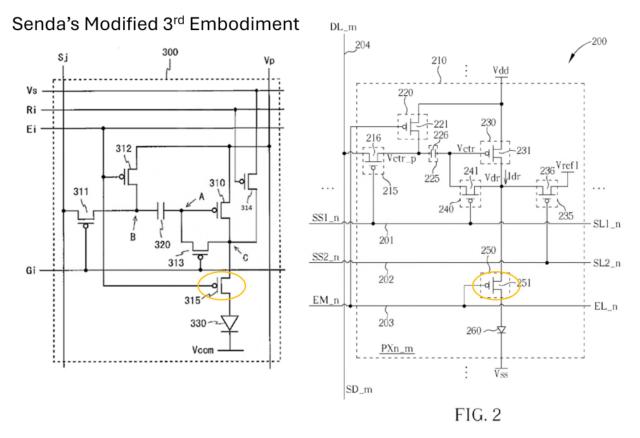

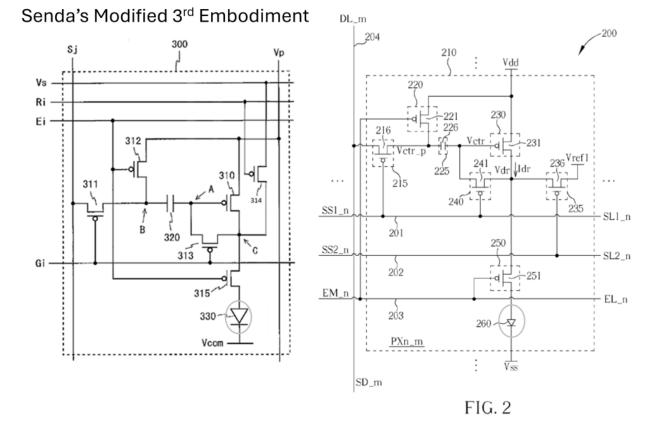

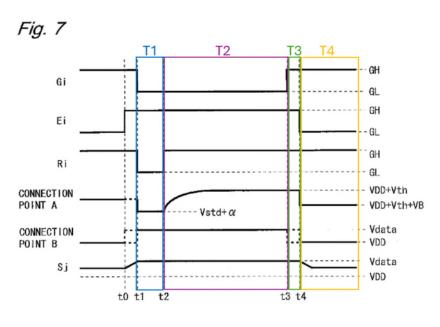

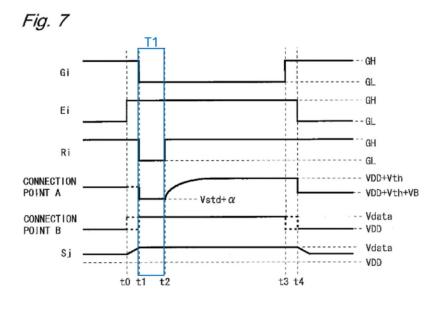

|     | A.  | Senda's Modified Third Embodiment         | 64 |  |  |

|     | B.  | Claim 1                                   | 70 |  |  |

|     | C.  | Claim 2:                                  | 90 |  |  |

|     | D.  | Claim 3:                                  | 90 |  |  |

|     | E.  | Claim 4:                                  | 91 |  |  |

|     | F.  | Claim 5:                                  | 91 |  |  |

|     | G.  | Claim 6:                                  | 91 |  |  |

|     | H.  | Claim 7:                                  | 91 |  |  |

|     | I.  | Claim 8:                                  | 91 |  |  |

|     | J.  | Claim 9:                                  |    |  |  |

|     | K.  | Claim 10:                                 | 92 |  |  |

|     | L.  | Claim 11:                                 |    |  |  |

|     | M.  | Claim 12:                                 | 92 |  |  |

|     | N.  | Claim 13:                                 | 93 |  |  |

|     | О.  | Claim 14:                                 | 93 |  |  |

|     | P.  | Claim 15:                                 |    |  |  |

|     | Q.  | Claim 16:                                 |    |  |  |

|     | R.  | Claim 17:                                 |    |  |  |

|     | S.  | Claim 18:                                 |    |  |  |

|     | Τ.  | Claim 19:                                 |    |  |  |

|     | U.  | Claim 20                                  |    |  |  |

|     | V.  | Claim 21                                  |    |  |  |

| XI. | GRO | UND 4: CLAIMS 1-21 ARE OBVIOUS OVER SENDA |    |  |  |

|     | A.  | Claims 1-21                               |    |  |  |

|     | B.  | Claim 21                                  |    |  |  |

## **INDEX OF EXHIBITS**

| Exhibit No. | Description                                                      |  |  |

|-------------|------------------------------------------------------------------|--|--|

| 1001        | U.S. Patent No. 8,502,757 (" <b>757 patent</b> ")                |  |  |

| 1002        | Declaration of R. Jacob Baker, Ph.D., P.E.                       |  |  |

| 1003        | File History of U.S. Patent No. 8,502,757                        |  |  |

| 1004        | U.S. 2007/0103406 (" <b>Kim406</b> ")                            |  |  |

| 1005        | U.S. 2005/0110730 (" <b>Kim730</b> ")                            |  |  |

| 1006        | U.S. 2009/0040150 ("Senda")                                      |  |  |

| 1007        | R. Jacob Baker, et al., CMOS Circuit Design, Layout, and         |  |  |

|             | Simulations (1st ed. 1998)                                       |  |  |

| 1008        | U.S. Pat. App. Pub. No. 2007/0170990 ("Park")                    |  |  |

| 1009        | Order Setting Jury Selection for May 4, 2026                     |  |  |

| 1010        | Patent Owner's Infringement Contentions for the 757 patent dated |  |  |

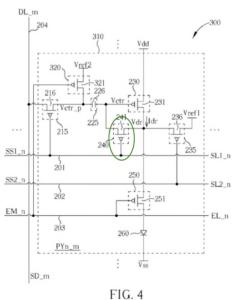

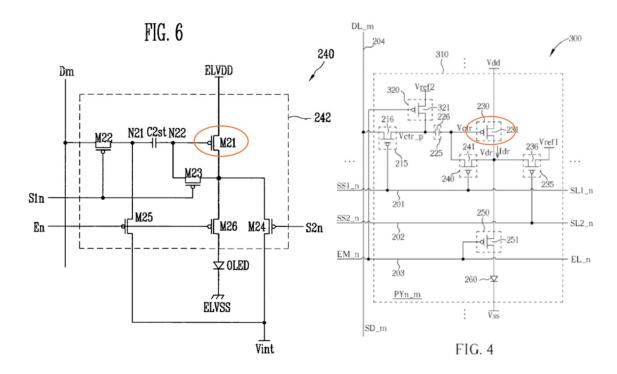

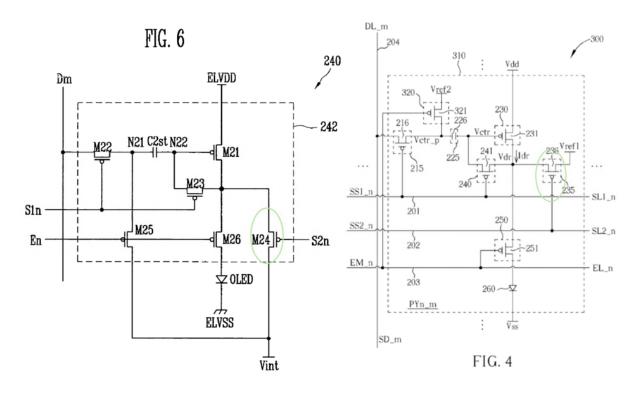

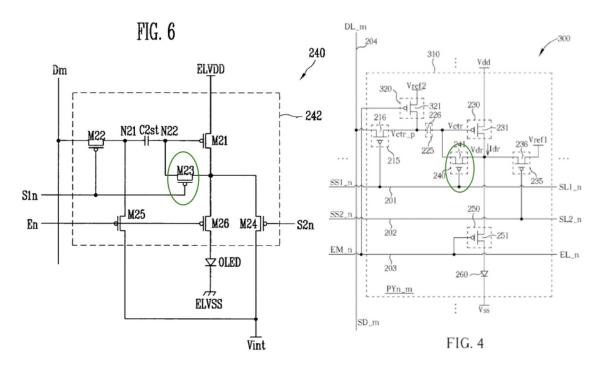

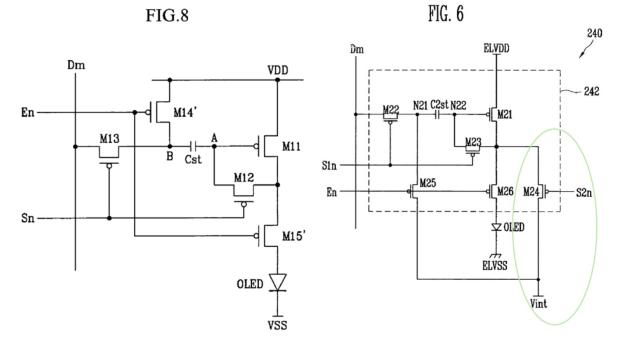

|             | January 21, 2025                                                 |  |  |

| 1011        | Dong-Wook Park, et. al., 53.5: High-Speed AMOLED Pixel           |  |  |

|             | Circuit and Driving Scheme, SID 10 Digest (2010).                |  |  |

| 1012        | Jung Chul Kim, et. al., A Novel OLED Pixel Circuit with          |  |  |

|             | Controllable Threshold Voltage Compensation Time, IDW '19        |  |  |

|             | (2019).                                                          |  |  |

| 1013        | Chih-Lung Lin, et. al., Compensation Pixel Circuit to Improve    |  |  |

|             | Image Quality for Mobile AMOLED Displays, IEEE Journal of        |  |  |

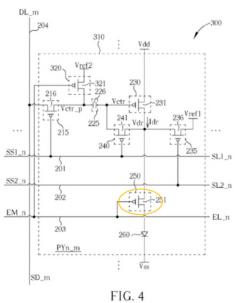

|             | Solid-State Circuits (2018).                                     |  |  |

| 1014        | Docket Sheets Search                                             |  |  |

| 1015        | Curriculum Vitae of Dr. R. Jacob Baker                           |  |  |

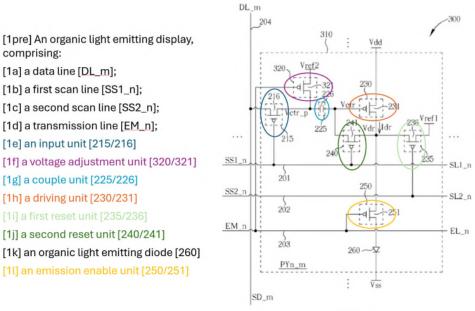

[1pre] An organic light emitting display, comprising:

[1a] a data line for transmitting a data signal;

[1b] a first scan line for transmitting a first scan signal;

[1c] a second scan line for transmitting a second scan signal;

[1d] a transmission line for transmitting an emission signal;

[1e] an input unit, electrically connected to the data line and the first scan line,

for outputting a preliminary control voltage according to the data signal and the first scan signal;

[1f] a voltage adjustment unit, electrically connected to the transmission line and the input unit, for adjusting the preliminary control voltage according to the emission signal and a second reference voltage;

[1g] a couple unit, electrically connected to the input unit and the voltage adjustment unit, for adjusting a control voltage through coupling a change of the preliminary control voltage;

[1h] a driving unit, electrically connected to the couple unit, for providing a driving current and a driving voltage according to the control voltage and a first power voltage;

[1i] a first reset unit, electrically connected to the driving unit and the second scan line, for resetting the driving voltage according to the second scan signal and a first reference voltage;

[1j] a second reset unit, electrically connected to the driving unit, the first reset unit and the first scan line, for resetting the control voltage according to the first scan signal and the driving voltage;

[1k] an organic light emitting diode for generating output light according to the driving current; and

[11] an emission enable unit, electrically connected to the transmission line, the driving unit and the organic light emitting diode, for providing a control of furnishing the driving current to the organic light emitting diode according to the emission signal.

[2] The organic light emitting display of claim 1, wherein the input unit comprises a first transistor, the first transistor having a first end electrically connected to the data line, a gate end electrically connected to the first scan line, and a second end electrically connected to the voltage adjustment unit and the couple unit.

[3] The organic light emitting display of claim 2, wherein the first transistor comprises a thin film transistor or a field effect transistor.

[4] The organic light emitting display of claim 1, wherein the driving unit comprises a second transistor, the second transistor having a first end for receiving the first power voltage, a gate end for receiving the control voltage, and a second end for outputting the driving current and the driving voltage.

[5] The organic light emitting display of claim 4, wherein the second transistor comprises a thin film transistor or a field effect transistor.

[6] The organic light emitting display of claim 1, wherein the couple unit comprises a capacitor electrically connected between the input unit and the driving unit.

[7] The organic light emitting display of claim 1, wherein the first reset unit comprises a third transistor, the third transistor having a first end for receiving the first reference voltage, a gate end electrically connected to the second scan line, and a second end electrically connected to the driving unit, the second reset unit and the emission enable unit.

[8] The organic light emitting display of claim 7, wherein the third transistor comprises a thin film transistor or a field effect transistor.

[9] The organic light emitting display of claim 1, wherein the second reset unit comprises a fourth transistor, the fourth transistor having a first end electrically connected to the driving unit, the first reset unit and the emission enable unit, a gate end electrically connected to the first scan line, and a second end electrically connected to the couple unit and the driving unit.

[10] The organic light emitting display of claim 9, wherein the fourth transistor comprises a thin film transistor or a field effect transistor.

[11] The organic light emitting display of claim 1, wherein the voltage adjustment unit comprises a fifth transistor, the fifth transistor having a first end for receiving the second reference voltage, a gate end electrically connected to the transmission line, and a second end electrically connected to the input unit and the couple unit.

[12] The organic light emitting display of claim 11, wherein the fifth transistor comprises a thin film transistor or a field effect transistor.

[13] The organic light emitting display of claim 11, wherein the second reference voltage is the first power voltage.

[14] The organic light emitting display of claim 1, wherein the emission enable unit comprises a sixth transistor, the sixth transistor having a first end electrically connected to the driving unit, the first reset unit and the second reset unit, a gate end electrically connected to the transmission line, and a second end electrically connected to the organic light emitting diode.

[15] The organic light emitting display of claim 14, wherein the sixth transistor comprises a thin film transistor or a field effect transistor.

[16] The organic light emitting display of claim 1, wherein the organic light emitting diode comprises an anode electrically connected to the emission enable unit and a cathode for receiving a second power voltage.

[17pre] A driving method, comprising:

[17a] outputting a preliminary control voltage by an input unit according to a data signal and a first scan signal;

[17b] adjusting the preliminary control voltage by a voltage adjustment unit according to an emission signal and a second reference voltage;

[17c] adjusting a control voltage by a couple unit through coupling a change of the preliminary control voltage;

[17d] providing a driving current and a driving voltage by a driving unit according to the control voltage and a power voltage;

[17e] resetting the driving voltage by a first reset unit according to a second scan signal and a first reference voltage;

[17f] resetting the control voltage by a second reset unit according to the first scan signal and the driving voltage;

[17g] generating output light by an organic light emitting diode according to the driving current;

[17h] providing a control of furnishing the driving current to the organic light emitting diode by an emission enable unit according to the emission signal;

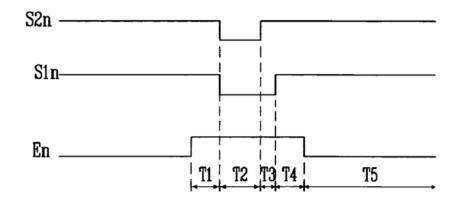

[17i] providing the first scan signal with a first level to the input unit and the second reset unit, providing the second scan signal with the first level to the first reset unit, providing the emission signal with a second level different from the first level for disabling a voltage adjusting operation of the voltage adjustment unit and disabling a current furnishing operation of the emission enable unit, and providing the data signal to the input unit during a first interval;

[17j] outputting the preliminary control voltage by the input unit according to the data signal and the first scan signal during the first interval;

[17k] resetting the driving voltage by the first reset unit according to the second scan signal and the first reference voltage during the first interval;

[171] resetting the control voltage by the second reset unit according to the first scan signal and the driving voltage during the first interval;

[17m] switching the second scan signal from the first level to the second level for disabling a resetting operation of the first reset unit during a second interval following the first interval;

[17n] performing a threshold voltage compensation operation on the control voltage by the second reset unit and the driving unit according to the first scan signal and the power voltage during the second interval;

[170] switching the first scan signal from the first level to the second level for disabling a resetting operation of the second reset unit and disabling an inputting operation of the input unit during a third interval following the second interval;

[17p] switching the emission signal from the second level to the first level during a fourth interval following the third interval;

[17q] adjusting the preliminary control voltage by the voltage adjustment unit according to the emission signal and the second reference voltage during the fourth interval;

[17r] adjusting the control voltage by the couple unit through coupling a change of the preliminary control voltage during the fourth interval;

[17s] providing the driving current by the driving unit according to the control voltage and the power voltage during the fourth interval;

[17t] furnishing the driving current to the organic light emitting diode by the emission enable unit according to the emission signal during the fourth interval; and

[17u] generating output light by the organic light emitting diode according to the driving current during the fourth interval.

[18] The driving method of claim 17, wherein the second level is greater than the first level.

[19] The driving method of claim 17, wherein the first level is greater than the second level.

[20] The driving method of claim 17, wherein the second reference voltage is the power voltage.

[21] The driving method of claim 17, wherein a length of the second interval is greater than a length of the first interval.

### I. INTRODUCTION

I, R. Jacob Baker, declare as follows:

1. My name is R. Jacob Baker. I have been asked by Petitioner BOE Technology Group Co. Ltd. ("Petitioner") to provide my expert opinions in support of the above-identified petition for *inter partes* review of claims 1-21 ("Challenged Claims") of U.S. Patent No. 8,502,757 ("757 patent," EX1001), owned by Optronic Sciences LLP ("PO"), pursuant to 35 U.S.C. §§311–19 and 37 C.F.R. §42.100.

2. I currently hold the opinions set forth in this declaration.

3. In summary, it is my opinion that the references cited below render obvious the Challenged Claims. My detailed opinions on the claims are set forth below.

I am being compensated for my time at the rate of \$765 per hour.

This compensation is not contingent upon my performance, the outcome of this matter, or any issues involved in or related to this matter.

### II. BACKGROUND AND QUALIFICATION

5. My qualifications generally are set forth in my Curriculum Vitae, which is attached as EX1015 and also includes a list of the publications I have authored and a list of the other cases in which I have testified during the last four years.

IPR2025-00239 - BOE Exhibit 1002 - Page 10

6. I have been working as an Engineer since 1985 and I have been teaching Electrical and Computer Engineering courses since 1991. I am currently a Professor Emeritus of Electrical and Computer Engineering at the University of Nevada, Las Vegas ("UNLV").

I received B.S. and M.S. degrees in Electrical Engineering from UNLV in 1986 and 1988, respectively. I received my Ph.D. in Electrical Engineering from the University of Nevada, Reno, in 1993.

8. My doctoral research, culminating in the award of a Ph.D., investigated the use of power MOSFETs in the design of very high peak power, and high-speed, instrumentation. I developed techniques to reliably stack power MOSFETs to switch higher voltages, that is, greater than 1,000 V and 100 Amps of current with nanosecond switching times. This work was reported in the paper entitled "Transformerless Capacitive Coupling of Gate Signals for Series Operation of Power MOSFET Devices," published in the IEEE Transactions on Power Electronics. The paper received the Best Paper Award in 2000.

#### A. Industry Experience

9. I have done technical and expert witness consulting for over 200 companies and their subsidiaries since I started working as an engineer in 1985. From 1985 to 1993, I worked for EG&G Energy Measurements and the Lawrence Livermore National Laboratory designing nuclear diagnostic instrumentation for

underground nuclear weapon tests at the Nevada test site. During this time, I designed, and oversaw the fabrication of, over 30 electronic and electro-optic instruments, including high-speed cable and fiber-optic receiver/transmitters, PLLs, frame and bit-syncs, data converters, streak-camera sweep circuits, Pockel's cell drivers, micro-channel plate gating circuits, charging circuits for battery backup of equipment for recording test data, and analog oscilloscope electronics.

10. My work during this time, as one example, had a direct impact on my doctoral research work using power MOSFETs, subsequent publishing efforts, and industry designs. In addition to the 2000 Best Paper Award from the IEEE Power Electronics Society, I published several other papers in related areas while working in industry. I hold a patent, Patent No. 5,874,830, in the area of power supply design, titled, "Adaptively biased voltage regulator and operating method," which was issued on February 23, 1999. I have designed dozens of linear and switching power supplies for commercial products and scientific instrumentation.

11. I am a licensed Professional Engineer and have extensive industry experience in circuit design, fabrication, and manufacture of Dynamic Random Access Memory (DRAM) semiconductor integrated circuit chips, Phase-Change Random Access Memory (PCRAM) chips, and CMOS Image Sensors (CISs) at Micron Technology, Inc. ("MTI") in Boise, Idaho. I spent considerable time working on the development of flash memory chips while at MTI. My efforts

IPR2025-00239 - BOE Exhibit 1002 - Page 12

resulted in more than a dozen patents relating to flash memory. One of my projects at MTI included the development, design, and testing of circuit design techniques for a multi-level cell (MLC) flash memory using signal processing. This effort resulted in higher-density memories for use in solid-state drives and flash memory cards having an ATA interface that are ubiquitous in consumer electronics, including cameras and data storage systems. Further, the use of higher-density memory can result in fewer changes in the flash translation layer for logical-tophysical addressing, less need for garbage collection, and larger data segments that can improve a computing system's performance. Another project I worked on at MTI focused on the design of buffers for high-speed double-data rate DRAM, which resulted in around 10 U.S. patents in buffer design. Among many other experiences, I led the development of the delay locked loop (DLL) in the late 1990s so that MTI DRAM products could transition to the DDR memory protocol, used in mobile and non-mobile (server, desktop, cell phones, tablets, etc.) computing systems as main computer memory, for addressing and controlling accesses to memory via interprocess communications (IPC) with the memory controller (MC). I provided technical assistance with MTI's acquisition of Photobit during 2001 and 2002, including transitioning the manufacture of CIS products into MTI's process technology. Further, I did consulting work at Sun Microsystems and then Oracle on the design of memory modules during 2009 and

IPR2025-00239 - BOE Exhibit 1002 - Page 13

2010. This work entailed the design of low-power, high-speed, and wide interconnection methods with the goal of transmitting data to/from the memory module and the MC at higher speeds.

12. I have extensive experience in the development of instrumentation and commercial products in a multitude of areas including: integrated electrical/biological circuits and systems, array (memory, imagers, and displays) circuit design, CMOS analog and digital circuit design, diagnostic electrical and electro-optic instrumentation for scientific research, CAD tool development and online tutorials, low-power interconnect and packaging techniques, design of communication/interface circuits (to meet commercial standards such as USB, firewire, DDR, PCIe, SPI, etc.), circuit design for the use and storage of renewable energy, and power electronics. For example, a part of my research at Boise State, for many years, focused on the use of Thru-Silicon-Vias (TSVs), aka Thru-Wafer Vias (TWVs), for high-density 3D packaging. These packaging techniques were utilized in the memory module development work I did with Sun Microsystems and Oracle. As another example, I designed circuitry for use in implementing Universal Serial Bus (USB) interface circuits while I did consulting at Tower Semiconductor. I designed PCI communication circuits for IPC between a Graphics Processor Unit (GPU) and memory while consulting for Rendition, Inc. From 1994 to 1996, I worked on the design of displays at Micron Display and

IPR2025-00239 - BOE Exhibit 1002 - Page 14

Micron Technology, Inc. ("Micron") in Boise, Idaho. This work was at a time when cathode ray tubes (CRTs) were still the dominant type of display. Flat panel displays were being developed with the hope of replacing CRTs in the consumer market. I worked on flat panel displays which resulted in 5 patents: 5,598,156, 5,638,085, 5,818,365, 5,894,293, and 5,909,201. I worked on the design of the pixels, both active and passive, as well as the supporting electronics for processing video signals. I was also involved with the evaluation of display technologies including liquid crystal displays (LCDs), light-emitting diodes, plasma displays, and organic light emitting diode (OLED) displays; the display technologies that were looking to displace CRTs in the consumer market. I was involved with the packaging of the displays including the vacuum sealing and deposition of the phosphors for light wavelength conversion. I also taught display design as a topic in my courses and did display design consulting again in industry for Cirque in 2013.

13. My current research work is focused in part on the design of integrated circuits for wireless sensing using LIDAR (LIght Detection And Ranging). I have worked with several companies in the development of these circuits and systems including Freedom Photonics, Aerius Photonics, and FLIR. In the early 1990s, I worked on wireless systems for wideband impulse radar while at Lawrence Livermore Laboratory. Further, part of my research for several years

IPR2025-00239 - BOE Exhibit 1002 - Page 15

focused on the digitization of IQ channels using delta-sigma modulation. The knowledge and experience gained from this effort are reflected in my textbook CMOS Mixed-Signal Circuit Design and a presentation, which I have present-ed at several universities and companies,

http://cmosedu.com/jbaker/papers/talks/BP\_DSM\_talk.pdf.

### **B.** Academic Experience

14. I was an adjunct faculty member in the Electrical Engineering departments of UNLV and UNR from 1991-1993. From 1993 to 2000, I served on the faculty at the University of Idaho as an Assistant Professor and then as a tenured Associate Professor of Electrical Engineering. In 2000, I joined a new Electrical and Computer Engineering program at Boise State University ("BSU"), where I served as department chair from 2004 to 2007. At BSU, I helped establish graduate programs in Electrical and Computer Engineering including, in 2006, the university's second Ph.D. degree. In 2012, I re-joined the faculty at UNLV. Over the course of my career as a professor, I have advised more than 100 masters and doctoral students.

15. I have been recognized for my contributions as an educator in the field. While at Boise State University, I received the President's Research and Scholarship Award (2005), Honored Faculty Member recognition (2003), and Outstanding Department of Electrical Engineering Faculty recognition (2001). In

IPR2025-00239 - BOE Exhibit 1002 - Page 16

2007, I received the Frederick Emmons Terman Award (the "Father of Silicon Valley"). The Terman Award is bestowed annually upon an outstanding young electrical/computer engineering educator in recognition of the educator's contributions to the profession. In 2011, I received the IEEE Circuits and Systems Education Award. I received the Tau Beta Pi Outstanding Electrical and Computer Engineering Professor Award every year it was awarded while I have been back at UNLV.

16. I have authored several books and papers in the electrical and computer engineering area. My published books include CMOS Circuit Design, Layout, and Simulation (Baker, R.J., Wiley-IEEE, ISBN: 9781119481515 (4th ed., 2019)) and CMOS Mixed-Signal Circuit Design (Baker, R.J., Wiley-IEEE, ISBN: 9780470290262 (2nd ed., 2009) and ISBN: 9780471227540 (1st ed., 2002)). I coauthored DRAM Circuit Design: Fundamental and High-Speed Topics (Keeth, B., Baker, R.J., Johnson, B., and Lin, F., Wiley-IEEE, ISBN: 9780470184752 (2008)), DRAM Circuit Design: A Tutorial (Keeth, B. and Baker, R.J., Wiley-IEEE, ISBN: 0-7803-6014-1 (2001)), and CMOS Circuit Design, Layout and Simulation (Baker, R.J., Li, H.W., and Boyce, D.E., Wiley - IEEE, ISBN: 9780780334168 (1998)). I contributed as an editor and co-author on several other electrical and computer engineering books.

IPR2025-00239 - BOE Exhibit 1002 - Page 17

### C. Other Relevant Experience

17. I have performed technical and expert witness consulting for more than 200 companies and their subsidiaries and given more than 50 invited talks at conferences, companies, and universities. Further, I am the author or co-author of more than 100 papers and presentations in the areas of electrical and computer engineering design, fabrication, and packaging.

18. I currently serve, or have served, as a volunteer on the IEEE Press Editorial Board (1999-2004); as editor for the Wiley-IEEE Press Book Series on Microelectronic Systems (2010-2018); as the Technical Program Chair of the 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS 2015); on the IEEE Solid-State Circuits Society (SSCS) Administrative Committee (2011-2016); as a Distinguished Lecturer for the SSCS (2012-2015); the Technology Editor (2012-2014) and Editor-in-Chief (2015-2020) for IEEE Solid-State Circuits Magazine; IEEE Kirchhoff Award Committee (2020-2023); and advisor for the student branch of the IEEE at UNLV (2013-2024). These meetings, groups, and publications are intended to allow researchers to share and coordinate research. My active participation in these meetings, groups, and publications allowed me to *See* what other researchers in the field have been doing.

19. In addition to the above, I am an IEEE Fellow for contributions to

semi-conductor memory design and a member of the honor societies Eta Kappa Nu

and Tau Beta Pi.

## **III. DOCUMENTS AND OTHER MATERIALS RELIED UPON**

20. In forming the opinions set forth in this declaration, I have reviewed

the documents in the following table:

| Exhibit No. | Description                                                      |  |  |  |  |

|-------------|------------------------------------------------------------------|--|--|--|--|

| 1001        | U.S. Patent No. 8,502,757 (" <b>757 patent</b> ")                |  |  |  |  |

| 1002        | Declaration of R. Jacob Baker, Ph.D., P.E.                       |  |  |  |  |

| 1003        | File History of U.S. Patent No. 8,502,757                        |  |  |  |  |

| 1004        | U.S. 2007/0103406 (" <b>Kim406</b> ")                            |  |  |  |  |

| 1005        | U.S. 2005/0110730 (" <b>Kim730</b> ")                            |  |  |  |  |

| 1006        | U.S. 2009/0040150 ("Senda")                                      |  |  |  |  |

| 1007        | R. Jacob Baker, et al., CMOS Circuit Design, Layout, and         |  |  |  |  |

|             | Simulations (1 <sup>st</sup> ed. 1998)                           |  |  |  |  |

| 1008        | U.S. Pat. App. Pub. No. 2007/0170990 ("Park")                    |  |  |  |  |

| 1009        | Order Setting Jury Selection for May 4, 2026                     |  |  |  |  |

| 1010        | Patent Owner's Infringement Contentions for the 757 patent dated |  |  |  |  |

|             | January 21, 2025                                                 |  |  |  |  |

| 1011        | Dong-Wook Park, et. al., 53.5: High-Speed AMOLED Pixel           |  |  |  |  |

|             | Circuit and Driving Scheme, SID 10 Digest (2010).                |  |  |  |  |

| 1012        | Jung Chul Kim, et. al., A Novel OLED Pixel Circuit with          |  |  |  |  |

|             | Controllable Threshold Voltage Compensation Time, IDW '19        |  |  |  |  |

|             | (2019).                                                          |  |  |  |  |

| 1013        | Chih-Lung Lin, et. al., Compensation Pixel Circuit to Improve    |  |  |  |  |

|             | Image Quality for Mobile AMOLED Displays, IEEE Journal of        |  |  |  |  |

|             | Solid-State Circuits (2018).                                     |  |  |  |  |

| 1014        | Docket Sheets Search                                             |  |  |  |  |

| 1015        | 015 Curriculum Vitae of Dr. R. Jacob Baker                       |  |  |  |  |

21. Additionally, I have utilized my own experience and expertise,

including regarding the knowledge and capabilities of a person of ordinary skill in the relevant art in the timeframe of the claimed priority date of the 757 patent.

### IV. STATUTORY GROUNDS FOR CHALLENGE

22. In this declaration, I offer opinions on the following grounds that are

the basis for this IPR proceeding:

| Ground | Claims      | Stat. Basis     | Prior Art                |

|--------|-------------|-----------------|--------------------------|

| 1      | 1-12, 14-19 | 35 U.S.C. § 102 | Kim406                   |

| 2      | 1-20        | 35 U.S.C. § 103 | Kim406 in view of Kim730 |

| 3      | 1-21        | 35 U.S.C. § 102 | Senda                    |

| 4      | 1-21        | 35 U.S.C. § 103 | Senda                    |

### V. RELEVANT PATENT LAW AND LEGAL STANDARDS

#### A. Date of Invention

23. I have been asked to use the date of the filing of the earliest application to which priority is claimed (i.e., March 17, 2011) as the date of invention for purposes of my analysis.

### **B.** Anticipation

24. I am informed and understand that a patent claim is invalid under 35

U.S.C. § 102 if a prior art disclosure teaches every element required by the claim,

either expressly or inherently. The identical invention must be shown in as

complete detail as is contained in the claim. When a claim covers several structures

or compositions, either generically or as alternatives, the claim is deemed

anticipated if any of the structures or compositions within the scope of the claim is known in the prior art.

### C. Obviousness

25. I am informed and understand that a patent claim is invalid under 35 U.S.C. § 103 if the differences between the invention and the prior art are such that the subject matter as a whole would have been obvious at the time of the invention to a person having ordinary skill in the art to which the subject matter pertains. Obviousness, as has been explained to me, is based on (i) the scope and content of the prior art, (ii) the differences between the prior art and the claim, (iii) the level of ordinary skill in the art, and (iv) any secondary indicia of non-obviousness (*e.g.*, "secondary considerations" such as commercial success in the marketplace of the claimed invention), to the extent that they exist.

26. I further understand that obviousness may be demonstrated by showing that it would have been obvious to combine the teachings of more than one item of prior art. In determining whether a piece of prior art could have been combined with other prior art or with other information within the knowledge of a person having ordinary skill in the art, the following are examples of approaches and rationales that may be considered:

• Combining prior art elements according to known methods to yield predictable results;

- Simple substitution of one known element for another to obtain predictable results;

- Use of a known technique to improve similar devices (methods, or products) in the same way;

- Applying a known technique to a known device (method or product) ready for improvement to yield predictable results;

- Applying a technique or approach that would have been obvious to try (choosing from a finite number of identified, predictable solutions, with a reasonable expectation of success);

- Known work in one field of endeavor may prompt variations of it for use in either the same field or a different one based on design incentives or other market forces if the variations would have been predictable to a person having ordinary skill in the art; and

- Some teaching, suggestion, or motivation in the prior art that would have led one of ordinary skill to modify the prior art reference or to combine prior art reference teachings to arrive at the claimed invention.

27. I further understand that an invention may be obvious if one of ordinary skill in the art, facing a wide range of needs created by developments in the field, would have *See*n an obvious benefit to the solutions tried by the applicant. When there is a design need or market pressure to solve a problem and there are a finite number of identified, predictable solutions, it may be obvious to a person of ordinary skill to try the known options. If a technique has been used to improve one device, and a person of ordinary skill in the art would recognize that it

would improve similar devices in the same way, using the technique would have been obvious.

28. I further understand that a person of ordinary skill in the art is a hypothetical person who is presumed to be aware of all of the relevant art at the time of the invention. The person of ordinary skill may be able to fit together the teachings of multiple patents and/or printed publications employing ordinary creativity and the common sense that familiar items may have uses in another context or beyond their primary purposes.

29. I also understand that when considering the obviousness of a patent claim, one should consider whether a teaching, suggestion, or motivation to combine the references exists so as to avoid impermissibly applying hindsight when combining or modifying the prior art. I understand this test should not be applied rigidly, but that the test can be important to avoid such hindsight.

30. I also understand that one of ordinary skill in the art must have a reasonable expectation of success in combining or modifying prior art references.

31. I also understand that all elements of a claim must be considered in an obviousness analysis.

### **D.** Claim Construction

32. I understand that claims are construed from the perspective of a person of ordinary skill as of the effective filing date of the patent application. A

"person of ordinary skill in the art" is a hypothetical person who is presumed to have known the relevant art at the time of the invention.

33. I understand that persons of ordinary skill in the art are deemed to read the claims in the context of the entire patent, including the specification and prosecution history. In other words, the terms are not considered in a vacuum.

34. I understand that the claims define the invention and the terms used in the claims are generally given the plain and ordinary meanings they would have to a person of ordinary skill in the art at the time of the effective filing date of the application. The context of a claim can be particularly helpful, and other claims may inform the meaning of a term in a particular claim.

35. I understand that claim terms are normally used consistently throughout a patent. Thus, the meaning of a term may help inform the meaning of the same term in other claims. Differences between claims may also help define the terms, although this may not be the case where the specification or prosecution history indicate that such differences do not impact the scope of the claims.

36. I understand that a patentee can act as its own lexicographer by defining a term, in the patent specification, to have specific meaning. It is my understanding that statements made to the patent office by the patentee or its legal representative during prosecution can serve to illuminate, or possibly narrow the proper scope of claim terms, and that such statements must be considered when

construing the claim terms. This is sometimes referred to as disclaimer. I have taken into account these principles in my analysis.

37. I understand that reference materials that were publicly available at the time that the patent application was filed, such as dictionaries, treatises or other technical references, may provide context and background for deciphering how one of ordinary skill in the art would have considered the terms used in the claims.

38. However, I understand that such references, as well as testimony (including this report) are generally known as "extrinsic evidence," and are accorded less weight than evidence found within the patent and prosecution history. In addition, I understand that extrinsic evidence that is inconsistent with the claims, specification, or prosecution history should not be considered in the claim construction process.

#### E. Section 112(f) Means Plus Function

39. I understand that under pre-America Invents Act (AIA) 35 U.S.C. § 112(6) and post-AIA § 112(f) "An element in a claim for a combination may be expressed as a means or step for performing a specified function without the recital of structure, material, or acts in support thereof, and such claim shall be construed to cover the corresponding structure, material, or acts described in the specification and equivalents thereof." The structure disclosed in the written description of the specification is the corresponding structure only if the written description of the

specification or the prosecution history clearly links or associates that structure to the function recited in a means-plus-function claim limitation.

40. I understand that when claim terms use the words "means . . for" and recites a function, and the term does not recite any structure for performing that function, the term should be construed pursuant to Section 112(f) looking for a corresponding structure, material, or act described in the specification and equivalents.

41. I also understand that when claim terms that lack the use of the term "means" presumably are not construed pursuant to Section 112(f) looking for a corresponding structure, material, or act described in the specification and equivalents, but if the claim terms recite any function without any structure, then these claim terms will be construed pursuant to Section 112(f).

#### F. Section 112 Definiteness

42. I understand that "[t]he specification shall conclude with one or more claims particularly pointing out and distinctly claiming the subject matter which the applicant regards as his invention."<sup>1</sup>

43. I understand that that claims must be definite. This means that the claims must particularly point out and distinctly claim the subject matter that the

<sup>&</sup>lt;sup>1</sup> I understand that the quoted text comes from the patent statute, 35 U.S.C.  $\$ 112 \ \ 2.$

applicant regards as her invention. I understand that indefiniteness is evaluated from the perspective of a person of ordinary skill in the art at the time of a patent's filing. I understand that a patent claim is indefinite if the claim, when read in light of the specification and the prosecution history, fails to inform, with reasonable certainty, a person of ordinary skill in the art of the scope of the invention. Absolute or mathematical precision in claim language is not required and even if more than one interpretation is presented for a claim term, the term may still be definite if an informed and confident choice is available among the contending alternative definitions.

### G. Standard of Proof

44. I understand that the standard to prove unpatentability in an *inter partes* review proceeding is by a preponderance of the evidence, which means more likely than not.

## VI. THE 757 PATENT

## A. Overview of the 757 Patent

45. The 757 patent was filed on November 15, 2011, and issued on August 6, 2013. EX1001, Face of Patent.

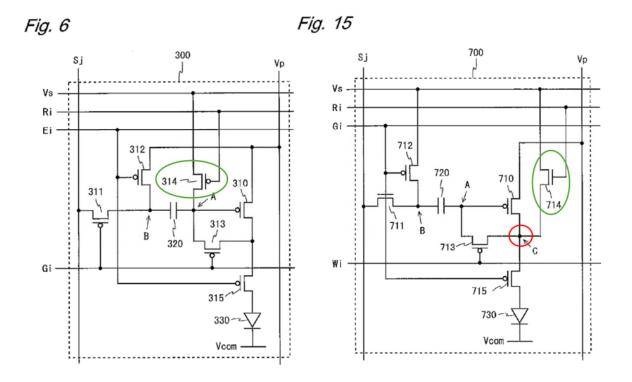

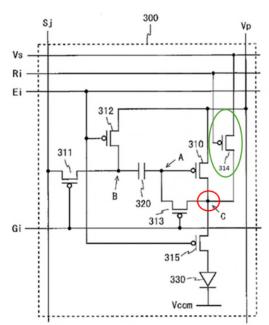

46. The 757 patent purports to improve on a prior art pixel driving circuit (Figure 1) by adding reset and threshold voltage compensation mechanisms to avoid image retention and pixel brightness distortion. EX1001, 7:4-9.

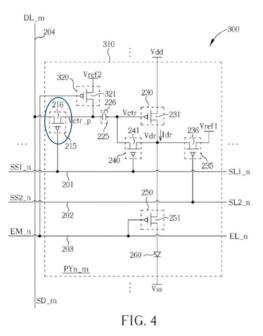

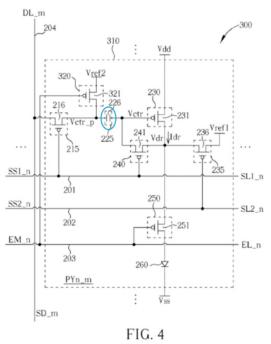

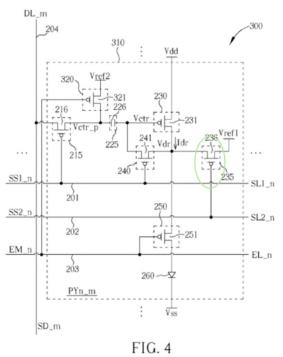

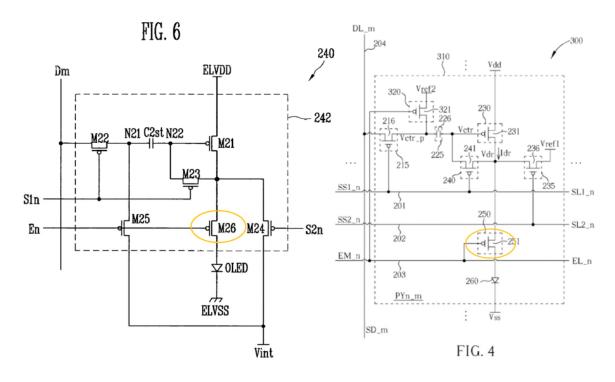

47. The 757 patent discloses a pixel driving circuit as shown in the embodiments in Figures 2 and 4. In the embodiment in Figure 2, the voltage adjustment unit uses Vdd as the second reference voltage. *See* Fig. 2 (unit 220 is transistor 221 with electrode connected to Vdd). In the embodiment in Figure 4, the voltage adjustment unit uses Vref2. *See* Fig. 4 (unit 320 is transistor 321 with electrode connected to Vref2). The embodiments are otherwise identical and the timing of the circuit is provided in Figure 3 and accompanying text.

### **B.** Overview of the 757 patent's File History

48. The claims of the 757 patent were allowed on the first office action (with amendments to claim 17 under *Ex Parte Quayle*). EX1003, 80-92 (April 25, 2013 Office Action). The Examiner found none of the prior art of record disclosed the voltage adjustment unit and first reset unit in combination with the other limitations of the claims. *Id.* The prior art asserted herein discloses those limitations as shown below.

### C. Person of Ordinary Skill in the Art

49. A person of ordinary skill in the art ("POSITA") at the time of the alleged invention of the 757 patent (November 15, 2011), and for that matter, at all subsequent times through the present, would have had a Bachelors' degree in electrical engineering or a comparable field of study, plus approximately one or more years of professional experience with electronic and optoelectronic system

design. Additional graduate education could substitute for professional experience, and significant experience in the field could substitute for formal education.

## D. Claim Construction Under 37 C.F.R. § 42.104(b)(3)

50. Any claim terms not listed below should be construed according to their plain and ordinary meaning to a POSITA at the time of the 757 patent.

## 1. Means-Plus-Function Limitations

51. Claim 1 recites several limitations as "... unit ... for" performing a claimed function. The lack of the word "means" raises the presumption that these terms are not subject to Section 112f, but that presumption is rebutted because none of the terms recite sufficient structure for performing the claimed function.

52. Each term follows the same format: a functional qualifier, the nonce word "unit," an appositive reciting connections, and "for" followed by a function. The "voltage adjustment unit" in limitation [1f] is reproduced below as an example.

a voltage adjustment unit, electrically connected to the transmission line and the input unit, for adjusting the preliminary control voltage according to the emission signal and a second reference voltage

EX1001, [1f].

53. In each limitation, the initial functional qualifier is merely a shorthand paraphrasing of the function and does not impart structure to a POSITA. The word

"unit" does not recite structure because it is merely a nonce word for any circuitry that would perform the function. The claimed connections add some limitations as to how the structure is connected but is not sufficient structure for performing the claimed function. The "for" clause then recites the function without any structure for performing the function. Thus, each limitation would not be recognized by one of ordinary skill in the art as reciting sufficiently definite structure for performing the claimed function.

54. I will apply the prior art under both the ordinary meaning of the claim and under the correct means-plus-function constructions. The prior art invalidates the claims under each construction.

55. Each limitation subject to 112f is presented below with its <u>function</u> <u>underlined</u> (the functions are entitled to their ordinary meaning and do not require further construction) followed by the corresponding structure disclosed and linked in the specification for performing the claimed function.

## a. [1e] "an input unit…"

56. "An input unit, electrically connected to the data line and the first scan line, <u>for outputting a preliminary control voltage according to the data signal and</u> <u>the first scan signal</u>" has the corresponding structure: transistor 216 connected as disclosed in Figures 2, 4 and 4:34-38.

57. This structure is linked to this function. EX1001, Fig. 3, 3:54-57, 5:13-15.

## b. [1f] "a voltage adjustment unit..."

58. "A voltage adjustment unit, electrically connected to the transmission line and the input unit, <u>for adjusting the preliminary control voltage according to</u> <u>the emission signal and a second reference voltage</u>" has the corresponding structure:

- a) transistor 221 connected as disclosed in Figure 2 and 4:34-38 (to Vdd), or

- b) transistor 321 connected as disclosed in Figure 4 and 6:36-42 (to Vref2).

59. Each of these structures is linked to this function. EX1001, Fig. 3, 3:58-61 (221), 5:45-55 (Vdd), 6:31-63 (321), 6:43-51 (Vref2).

## c. [1g] "a couple unit…"

60. "A couple unit, electrically connected to the input unit and the voltage adjustment unit, <u>for adjusting a control voltage through coupling a change of the</u> <u>preliminary control voltage</u>" has the corresponding structure: capacitor 226 connected as disclosed in Figures 2 and 4 and 4:42-44.

61. This structure is linked to this function. EX1001, Fig. 3, 3:62-65, 5:50-55, 6:46-51.

## d. [1h] "a driving unit…"

62. "A driving unit, electrically connected to the couple unit, <u>for</u> <u>providing a driving current and a driving voltage according to the control voltage</u> <u>and a first power voltage</u>" has the corresponding structure: transistor 231 connected as disclosed in Figures 2, 4 and 4:38-41.

63. This structure is linked to this function. EX1001, 3:65-4:2, 5:56-60,6:53-64.

## e. [1i] "a first reset unit…"

64. "A first reset unit, electrically connected to the driving unit and the second scan line, <u>for resetting the driving voltage according to the second scan</u> <u>signal and a first reference voltage</u>" has the corresponding structure: transistor 236 connected as disclosed in Figures 2, 4 and 4:44-48.

65. This structure is linked to this function. EX1001, 4:2-5.

## f. [1j] "a second reset unit..."

66. "A second reset unit, electrically connected to the driving unit, the first reset unit and the first scan line, for resetting the control voltage according to the first scan signal and the driving voltage" has the corresponding structure: transistor 241 connected as disclosed in Figures 2, 4 and 4:48-52.

67. This structure is linked to this function. EX1001, 4:5-9.

## g. [11] "an emission enable unit..."

68. "An emission enable unit, electrically connected to the transmission line, the driving unit and the organic light emitting diode, <u>for providing a control of</u> <u>furnishing the driving current to the organic light emitting diode according to the</u> <u>emission signal</u>" has the corresponding structure: transistor 221 connected as disclosed in Figures 2, 4 and 4:54-58.

69. This structure is linked to this function. EX1001, 4:9-14.

# h. Abridged Claim Listing Summary

70. An abridged claim listing summarizing the 112f terms is reproduced below next to the corresponding structure as shown in Figure 4 (the alternative structure of 220/221 for the voltage adjustment unit in Figure 2 is not shown).

#### 2. "first/second reference voltage"

#### a. **Primary Construction**

71. The claims encompass first and second reference voltages that are the same or different from each other. The claims use "first" and "second" as labels to refer to two reference voltages in the independent claims. The claims themselves make clear that differently labelled voltages in the independent claims can be the same voltage. For example, claim 1 recites a "second reference voltage" and a "first power voltage" and then dependent claim 13 recites "wherein the second reference voltage is the first power voltage." EX1001, claims 1, 13. There is no definition or disclaimer in the specification or file history that would require limiting the "first" and "second" reference voltages to only the same voltage or to only different voltages. The disclosed embodiments do not explicitly state, or

implicitly require, that the reference voltages be different from each other, so it is not possible to read such a limitation in from the specification (which would be legally improper, even if it were possible). For example, a POSITA would have understood that a large and overlapping range of suitable voltage potentials could serve as the first reference voltage to put the driving transistor into a conductive state and the second reference voltage to adjust the preliminary control voltage as disclosed. The patent discloses that in one example Vref2 could be Vdd but does not otherwise disclose ranges for Vref1 or Vref2, confirming the selection of an appropriate reference voltage is within the knowledge and skill of a POSITA. As shown below for Kim406, it was known in the art to use the same reference voltage (Vint) for both disclosed functions. EX1004, Fig. 6, [0064], [0067]. Thus, A POSITA would have known that Vref 1 and Vref2 could have been the same or different from each other. Finally, the ordinary meaning of "first" and "second" reference voltages encompasses reference voltages that are the same or different. See. e.g., EX1007 (Fig. 29.30); EX1008, [0039] (VREF1 and VREF2 may be the same or different voltage values). Thus, the claims encompass "first" and "second" reference voltages that are the same or different.

## b. Alternative Construction

72. I have been asked to also consider the validity of the claims under an alternative construction, wherein the "first" and "second" voltages are limited to different voltages.

## VII. OVERVIEW OF THE PRIOR ART REFERENCES

## A. EX1004 – Kim406

73. U.S. Pat. App. Pub. 2007/0103406 to Kim406 was published on May10, 2007 and is prior art under pre-AIA Section 102(b).

# B. EX1005 – Kim730

74. U.S. Pat. App. Pub. 2005/0110730 to Kim730 was published on May 26, 2005 and is prior art under pre-AIA Section 102(b).

## C. EX1006 – Senda

75. U.S. Pat. App. Pub. 2009/0040150 to Senda was published on

February 12, 2000 and is prior art under pre-AIA Section 102(b).

## **D.** Analogous Art

76. Each of the references is analogous art to the 757 patent because each

relates to an OLED display with threshold voltage compensation and driving method.

# VIII. GROUND 1: CLAIMS 1-12 AND 14-19 ARE ANTICIPATED BY KIM406

- A. Claim 1

- 1. [1pre]

- 77. Kim406 discloses "An organic light emitting display, comprising (see

following limitations)."

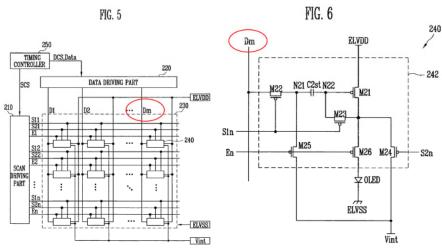

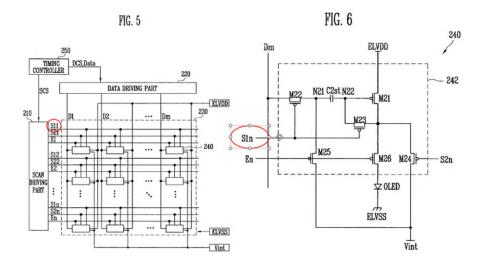

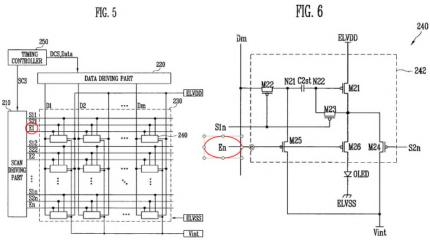

78. EX1004, Title ("Pixel and Organic Light Emitting Display Device using the Same"), Figs. 5-7, [0003], [0045] ("organic light emitting display device"), [0046]-[0072], claims 1-20.

# 2. [1a]

79. Kim406 discloses "a data line (Dm) for transmitting a data signal (data signal)."

80. EX1004, Figs. 5 (Data Driving Part 220 and lines D1 to Dm), Fig. 6 (line Dm), [0049] (Data Driving Part 220 sends data signals on data lines Dm), [0054] (pixel receives data signals from data lines Dm), [0064] (data signal supplied on Dm).

## 3. [1b]

81. Kim406 discloses "a first scan line (S1n) for transmitting a first scan signal (first scan signal)."

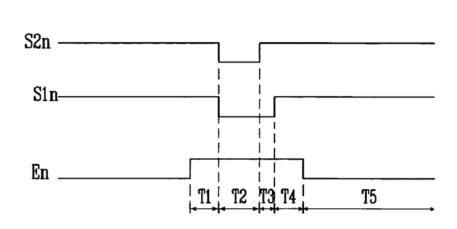

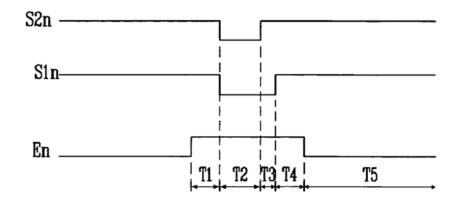

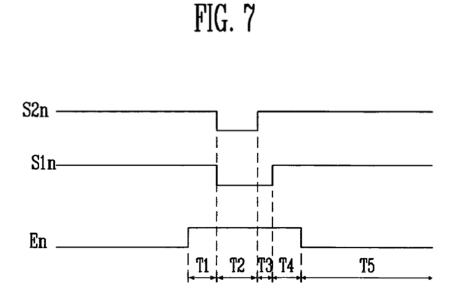

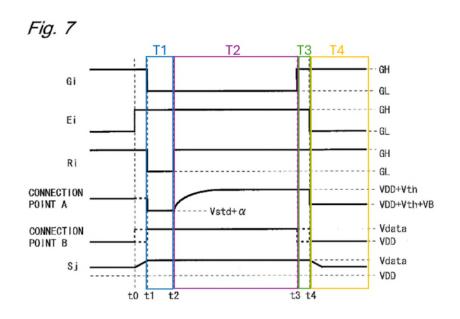

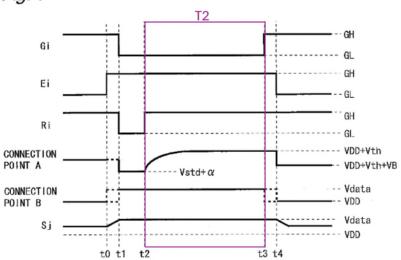

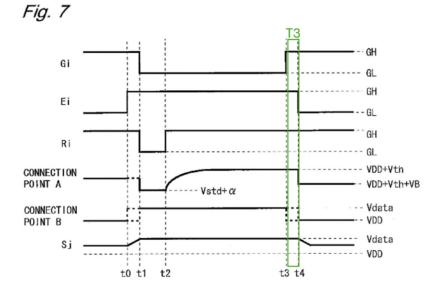

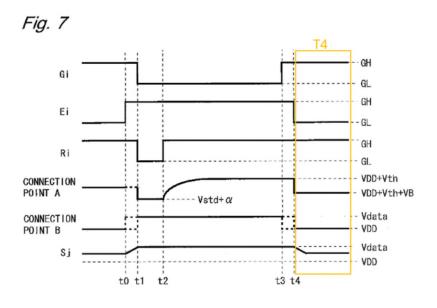

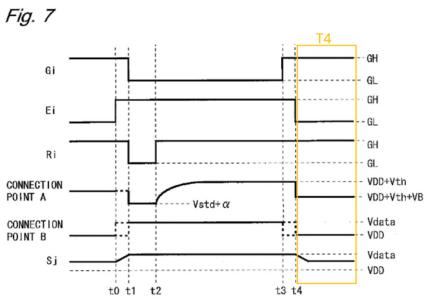

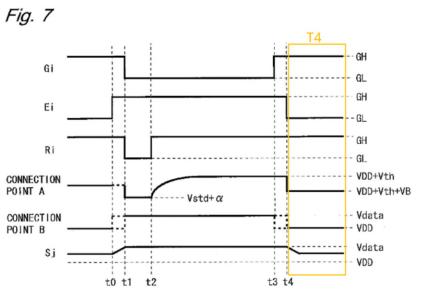

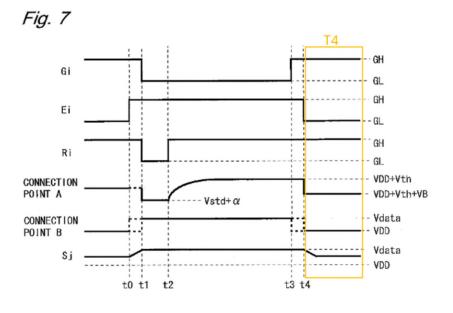

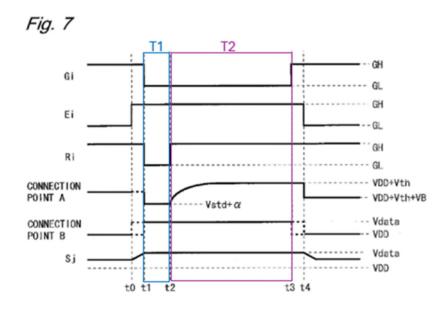

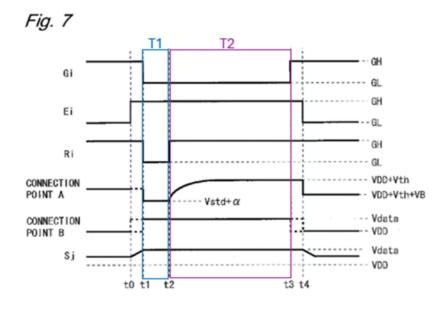

IPR2025-00239 - BOE Exhibit 1002 - Page 42 Declaration of Dr. R. Jacob Baker U.S. Patent No. 8,502,757 82. EX1004, Figs. 5 (Scan Driving Part 210), Fig. 6 (S1n), Fig. 7 (S1n), [0048] (scan driving part 210 transmits first scan signal on S1n), [0054] (pixel receives first scan signal on S1n), [0062]-[0064] (first scan signal supplied on S1n).

#### 4. [1c]

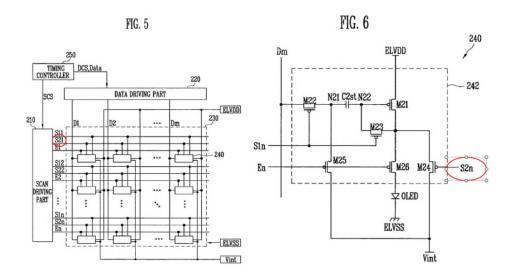

83. Kim406 discloses "a second scan line (S2n) for transmitting a second scan signal (second scan signal)."

84. EX1004, Fig. 5 (Scan Driving Part 210), Fig. 6 (S2n), Fig. 7 (S2n), [0048] (scan driving part 210 transmits second scan signal on S2n), [0054] (pixel receives second scan signal on S2n), [0062]-[0064] (second scan signal supplied on S2n).

# 5. [1d]

85. Kim406 discloses "a transmission line (En) for transmitting an emission signal (emission control signal)."

1616995180

86. EX1004, Fig. 5 (Scan Driving Part 210), Fig. 6 (En), Fig. 7 (En),

[0048] (scan driving part 210 transmits emission control signal on En), [0062][0063], [0067] (emission control signal).

# 6. [1e]

87. Kim406 discloses "an input unit (M22), electrically connected to the data line (Dm) and the first scan line (S1n), for outputting a preliminary control voltage (outputting preliminary control voltage to node N21) according to the data signal (data signal on Dm) and the first scan signal (first scan signal on S1n)."

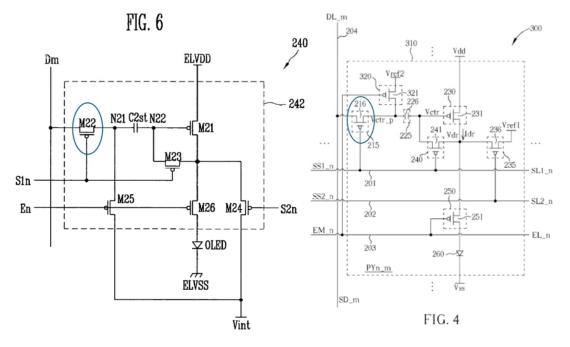

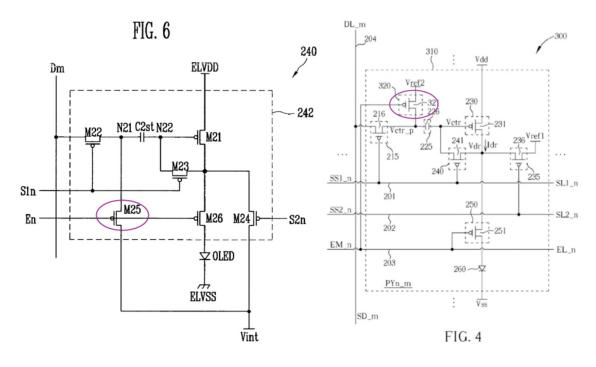

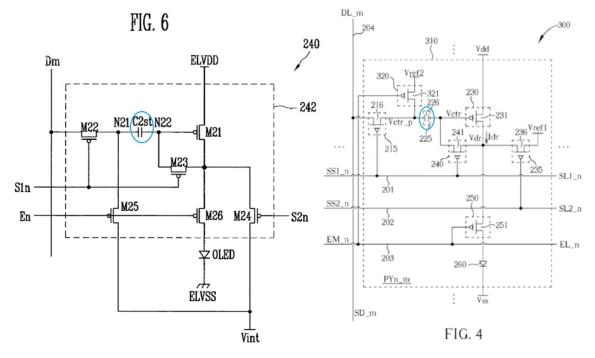

88. Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M22 is a PMOS transistor with a gate coupled to S1n, a first electrode coupled to the data line Dm, and a second electrode coupled to first node N21, such that during T2 and T3, M22 outputs a preliminary control voltage to the first node N21 according to the data signal on Dm and the low first scan signal on S1n. EX1004, Figs. 6-7, [0055], [0063] (PMOS), [0064] (T2 and T3). The second electrode of M22 is electrically connected to the voltage adjustment unit (M25) and couple unit (C2st). *Id.*, Fig. 6, [0055], [0059], [0061]. Under 112f, Kim406's PMOS transistor M22 as connected performs the claimed function and is identical to the corresponding structure for the input unit 215 (PMOS transistor 216 as connected). EX1001, Fig. 4, 4:34-38.

1616995180

#### 7. [1f]

89. Kim406 discloses "a voltage adjustment unit (M25), electrically connected to the transmission line (En) and the input unit (M22), for adjusting the preliminary control voltage (voltage at N21) according to the emission signal (emission control signal on En) and a second reference voltage (Vint)."

90. Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M25 is a PMOS transistor with a gate coupled to En, a first electrode connected to M22 and C2st (first node N21), and a second electrode coupled to initialization power source Vint, such that during T5, M25 adjusts the preliminary control voltage (voltage on first node N21) according to the low emission control signal on En and Vint. EX1004, Figs. 6-7, [0059], [0063] (PMOS), [0067] (when the fifth transistor M25 is turned on, the voltage value of

the first node N21 is reduced to the voltage value of the initialization power source Vint). *See* EX1001, 5:47-52, 6:43-48. Under 112f, Kim406's PMOS transistor M25 as connected performs the claimed function and is identical to the corresponding structure for the voltage adjustment unit 320 disclosed in the 757 patent (PMOS transistor 321 as connected). EX1001, Fig. 4, 6:36-42.

91. Kim406 discloses M25 is connected to "Vint" while the corresponding structure 321 is connected to "Vref2," but this difference in naming convention is not relevant. Vint in Kim406 is a reference voltage, which is all that is required under the primary construction. Under the alternative construction, see below for [1i].

## 8. [1g]

92. Kim406 discloses "a couple unit (C2st), electrically connected to the input unit (M22) and the voltage adjustment unit (M25), for adjusting a control voltage (voltage on N22) through coupling a change of the preliminary control voltage (capacitor C2st couples the change of the preliminary control voltage at N21 to adjust the voltage at N22)."

93. Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses storage capacitor C2st is between N21 and N22 and is charged during T3 to the voltage difference between N21 and N22. EX1004, Fig. 6, [0061], [0065]. N22 is floated in T4 and T5 by turning off M23, and in T5 when the preliminary control voltage at N21 is changed from the preliminary data signal voltage by application of Vint (*see* [1f]), capacitor C2st couples that change in voltage to N22, causing the voltage on N22 to change by the same amount. *Id.*, Fig. 7, [0066] (T4 turns off M22 and M23), [0067] (reducing voltage of N21 from data to Vint, and adjusting voltage of N22 with a reduction corresponding to the reduction of N21 to maintain a difference in C2st), [0069], claims 7 (second terminal (N22) floats), 8 (explaining how voltage at second terminal of capacitor (N22) is reduced corresponding to the voltage drop at first terminal (N21)).

94. Under 112f, Kim406's capacitor C2st as connected performs the claimed function and is identical to the corresponding structure for the couple unit 225 in the 757 patent (capacitor 226 as connected). EX1001, Fig. 4, 4:42-44.

#### 9. [1h]

95. Kim406 discloses "a driving unit (M21), electrically connected to the couple unit (C2st), for providing a driving current and a driving voltage (current and voltage at second electrode of M21), according to the control voltage (voltage at N22) and a first power voltage (ELVDD)."

96. Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M21 is a PMOS transistor with a gate coupled to C2st via node N22, a first electrode coupled to ELVDD, and a second electrode coupled to an unlabeled node with M23, M24, and M26, such that during T5 when

M21 is turned on by the control voltage at N22 and EN turns on M26, M21 provides a driving current and driving voltage at its second electrode. EX1004, Figs. 6-7, [0056], [0063] (PMOS), [0067]-[0070] (describing M21 driving OLED through M26). Under 112f, Kim406's PMOS transistor M21 as connected performs the claimed function and is identical to the corresponding structure for the driving unit disclosed in the 757 patent (PMOS transistor 231 as connected). EX1001, Fig. 4, 4:38-41.

97. Kim406 explicitly discloses that M21 provides a driving current at its second electrode which, during T5 when M26 is on, will drive the OLED. EX1004, Fig. 7, [0056], [0067]-[0070]. And Kim406 discloses that driving current provided by M21 is provided according to ELVDD and the control voltage at N22 applied to the gate of M21. *Id*.

98. Kim406 inherently discloses that M21 provides a "driving voltage." A POSITA would have known it was inherent from the electrical properties of Kim406's circuit that M21 is also providing a driving voltage with the driving current. To provide a driving current as disclosed in Kim406 a POSITA would have known that there must also be a driving voltage, i.e., the difference in potential between the second electrode of M21 and ELVSS. A POSITA would have known that without that difference in potential, there would be no driving current as disclosed in Kim406 and the OLED would not emit light. A POSITA

would have known that no current will flow through an LED without a driving voltage. A POSITA would have known that the relationship between the voltage and current across the diode is defined by the diode equation. A POSITA would have known that the precise magnitude of the driving voltage provided by M21 would be ELVDD minus the voltage drop across M21. EX1004, [0065], [0069].

## 10. [1i]

99. Kim406 discloses "a first reset unit (M24), electrically connected to the driving unit (M21) and the second scan line (S2n), for resetting the driving voltage (voltage at second electrode of M21) according to the second scan signal (S2n) and a first reference voltage (Vint)."

100. Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M24 is a PMOS transistor with a gate coupled to S2n, a first electrode coupled to the second electrode of M21 (and first electrode of M23 and first electrode of M26), and a second electrode coupled to the initialization power source Vint, such that during T2 when M24 is turned on by the second scan signal on S2n, it resets the driving voltage at the second electrode of M21 to Vint. EX1004, Figs. 6-7, [0058], [0063] (PMOS), [0064] (disclosing how during T2 M24 provides Vint to the node including the second electrode of M21, so that M23 can provide Vint to N22). See EX1001, 5:16-22. Vint provides a first reference voltage for M24 and a second reference voltage for M25 under the primary construction that encompasses the same voltage. Under 112f, Kim406's PMOS transistor M24 as connected performs the claimed function and is identical to the corresponding structure for the first reset unit disclosed in the 757 patent (PMOS transistor 236 as connected). EX1001, Fig. 4, 4:44-48.

101. Kim406 discloses M24 is connected to "Vint" while the corresponding structure 326 is connected to "Vref1," but this difference in naming convention is not relevant. Vint in Kim406 is a reference voltage, which is all that is required under the primary construction.

#### 11. [1j]

102. Kim406 discloses "a second reset unit (M23), electrically connected to the driving unit (M21), the first reset unit (M24), and the first scan line (S1n), for resetting the control voltage (voltage at N22) according to the first scan signal (S1n) and the driving voltage (voltage at second electrode of M21)."

103. Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M23 is a PMOS transistor with a gate coupled to S1n, a first electrode coupled to the second electrode of M21 (and M24 and M26), and a second electrode coupled to the gate of the M21 and C2st (N22), such that when M23 is turned on by the first scan signal on S1n, the driving voltage (voltage at second electrode of M21) is applied to reset the control voltage at N22. EX1004, Figs. 6-7, [0057], [0063]-[0065].

104. During T2, the control voltage (N22) is reset according to low scan signal (S1n) and the driving voltage Vint (voltage at second electrode of M21). Specifically, S1n and S2n are supplied turning M23 and M24 on, such that the voltage on Node N22 is reset to Vint. EX1004, Figs. 6-7, [0064].

105. During T3, the control voltage (N22) is reset according to low scan signal (S1n) and the driving voltage ELVDD-|Vth| (voltage at second electrode of M21). Specifically, S1n is still supplied keeping M23 on, but S2n is not supplied and M24 is turned off, such that the voltage on Node N22 is reset to ELVDD-|Vth|. EX1004, Figs. 6-7, [0065] (disclosing how current flows through M21 as a diode until "the voltage value of the second node N22 is obtained by subtracting the threshold voltage value of the first transistor M21 from the voltage value of the first power source ELVDD"). Kim406 discloses this reset is performed to compensate for the threshold voltage of M21. *Id.*, [0067]-[0069].

106. Kim406's disclosure in this regard is identical to the disclosure of the 757 patent wherein during T1, Vctrl is reset to Vref1 through 236 and 241 to ensure the driving transistor is in a conductive state, and during T2, Vctrl is reset to VDD-|Vth| through 241 to compensate for the threshold voltage of the driving transistor. EX1001, Fig. 3, 5:15-22 (T1), 5:23-38 (T2).

107. Under 112f, Kim406's PMOS transistor M23 as connected performs the claimed function and is identical to the corresponding structure for the second

reset unit disclosed in the 757 patent (PMOS transistor 241 as connected).

EX1001, Fig. 4, 4:48-52.

## 12. [1k]

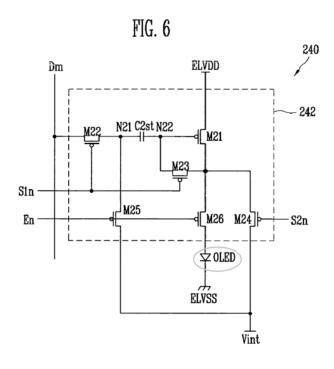

108. Kim406 discloses "an organic light emitting diode (OLED) for generating output light according to the driving current."

109. Kim406 discloses that the OLED is driven by the driving current provided by M21 to generate output light. EX1004, Fig. 6, [0052]-[0054], [0056], [0060], [0067]-[0070]. The amount of control voltage at N22 on the gate of M21 determines the amount of driving current M21 provides and, therefore, the brightness of the OLED. *Id.*

#### 13. [1l]

110. Kim406 discloses "an emission enable unit (M26), electrically connected to the transmission line (En), the driving unit (M21), and the organic light emitting diode (OLED), for providing a control of furnishing the driving current to the organic light emitting diode according to the emission signal (En)."

111. Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M26 is a PMOS transistor with a gate coupled to En, a first electrode coupled to the second electrode of M21 (and M23 and M24), and a second electrode coupled to the anode of the OLED, such that during T5 when M26 is turned on by the emission control signal on En, it furnishes the driving current from the second electrode of M21 to the OLED. EX1004, Figs. 6-7, [0060], [0063] (PMOS), [0067]-[0070] (disclosing how during T5 the low emission control signal causes M26 to turn on such that the driving current from the second electrode of M21 flows through M26 and drives the OLED). Under 112f, Kim406's PMOS transistor M26 as connected performs the claimed function and is identical to the corresponding structure for the emission enable unit disclosed in the 757 patent (PMOS transistor 251 as connected). EX1001, Fig. 4, 4:54-58.

#### **B.** Claim 2:

112. Kim406 discloses claim 1 "wherein the input unit (M22) comprises a first transistor (M22), the first transistor having a first end (first electrode) electrically connected to the data line (Dm), a gate end electrically connected to the first scan line (S1n), and a second end (second electrode) electrically connected to the voltage adjustment unit (M25) and the couple unit (C2st)." *See* [1e].

#### C. Claim 3:

113. Kim406 discloses claim 2, "wherein the first transistor (M22) comprises a thin film transistor or a field effect transistor (PMOS or NMOS)."

114. Kim406 discloses its transistors are PMOS or NMOS transistors. EX1004, [0026], [0063]. A POSITA would have known that PMOS and NMOS transistors are types of field effect transistors (FETs). Specifically, a POSITA would have known that PMOS and NMOS transistors are types of MOSFETs. EX1007, page 23.

## D. Claim 4:

115. Kim406 discloses claim 1, "wherein the driving unit (M21) comprises a second transistor (M21), the second transistor (M21) having a first end (first electrode) for receiving the first power voltage (ELVDD), a gate end for receive the control voltage (N22), and a second end (second electrode) for outputting the driving current and the driving voltage. *See* [1h].

## E. Claim 5:

116. See Claim 3, 4.

## F. Claim 6:

117. Kim406 discloses claim 1 "wherein the couple unit (C2st) comprises a capacitor (C2st) electrically connected between the input unit (M22) and the driving unit (M21). *See* [1g].

## G. Claim 7:

118. Kim406 discloses claim 1 "wherein the first reset unit (M24) comprises a third transistor (M24), the third transistor having a first end (second electrode) for receiving the first reference voltage (Vint), a gate end electrically connected to the second scan line (S2n), and a second end (first electrode) electrically connected to the drive unit (M21), the second reset unit (M23) and the emission enable unit (M26). *See* [1i], [1j]-[11].

## H. Claim 8:

119. See Claim 3, 7.

## I. Claim 9:

120. Kim406 discloses claim 1 "wherein the second reset unit (M23) comprises a fourth transistor (M23), the fourth transistor having a first end (first electrode) electrically connected to the driving unit (second electrode of M21), the first reset unit (M24) and the emission enable unit (M26), a gate end electrically connected to the first scan line (S1n), and a second end (second electrode) electrically connected to the couple unit (C2st) and the driving unit (gate of M21). *See* [1j], 1[h]-[11].

## J. Claim 10:

121. See Claim 3, 9.

## K. Claim 11:

122. Kim406 discloses claim 1 "wherein the voltage adjustment unit (M25) comprises a fifth transistor (M25), the fifth transistor having a first end for receiving the second reference voltage (Vint), a gate end electrically connected to the transmission line (En), and a second end electrically connected to the input unit (M22) and the couple unit (C2st)." *See* [1f], [1e]-[1g].

## L. Claim 12:

123. See Claim 3, 11.

# M. Claim 14:

124. Kim406 discloses claim 1 "wherein the emission enable unit (M26) comprises a sixth transistor (M26), the sixth transistor having a first end

electrically connected to the driving unit (M21), the first reset unit (M24) and the second reset unit (M23), a gate end electrically connected to the transmission line (En), and a second end electrically connected to the organic light emitting diode (OLED). *See* [11], [1e]-[1h], 7, 9.

#### N. Claim 15:

125. See Claim 3, 14.

#### **O.** Claim 16:

126. Kim406 discloses claim 1 "wherein the organic light emitting diode (OLED) comprises an anode electrically connected to the emission enable unit (M26) and a cathode for receiving a second power voltage (ELVSS)." *See* [1k]; EX1004, Fig. 6, [0053] ("The anode electrode of the OLED is coupled to the pixel circuit 242 and the cathode electrode of the OLED is coupled to the second power source ELVSS.").

#### **P.** Claim 17:

## 1. [17pre]

127. Kim406 discloses "a driving method, comprising." Kim406 discloses the pixel circuit in Figure 6 to drive an OLED as shown above. *See* Claim 1. Kim406 discloses in Figure 7 "a method of driving the pixel" of Figure 6. EX1004, Fig. 7, [0021].

## **2.** [17a]

128. Kim406 discloses "outputting a preliminary control voltage (voltage at N21) by an input unit (M22) according to a data signal (data signal on Dm) and a first scan signal (first scan signal on S1n)." *See* [1e].

## 3. [17b]

129. Kim406 discloses "adjusting the preliminary control voltage (voltage on N21) by a voltage adjustment unit (M25) according to an emission signal (emission control signal on En) and a second reference voltage (Vint)." *See* [1f].

## 4. [17c]

130. Kim406 discloses "adjusting a control voltage (adjusting voltage on N22) by a couple unit (C2st) through coupling a change of the preliminary control voltage (capacitor C2st couples the change of the preliminary control voltage at N21 to the voltage at N22)." *See* [1g].

# 5. [17d]

131. Kim406 discloses "providing a driving current and a driving voltage (current and voltage at second electrode of M21) by a driving unit (M21) according to the control voltage (voltage at N22) and a power voltage (ELVDD)." *See* [1h].

# 6. [17e]

132. Kim406 discloses "resetting the driving voltage (voltage at second electrode of M21) by a first reset unit (M24) according to a second scan signal (S2n) and a first reference voltage (Vint)." *See* [1i].

#### 7. [17f]

133. Kim406 discloses "resetting the control voltage (voltage at N22) by a second reset unit (M23) according to the first scan signal (S1n) and the driving voltage (voltage at second electrode of M21)." *See* [1j].

#### 8. [17g]

134. Kim406 discloses "generating output light by an organic light emitting diode (OLED) according to the driving current (current at second electrode of M21)." *See* [1k].

#### 9. [17h]

135. Kim406 discloses "providing a control of furnishing the driving current to the organic light emitting diode (OLED) by an emission enable unit (M26) according to the emission signal (En)." *See* [11].

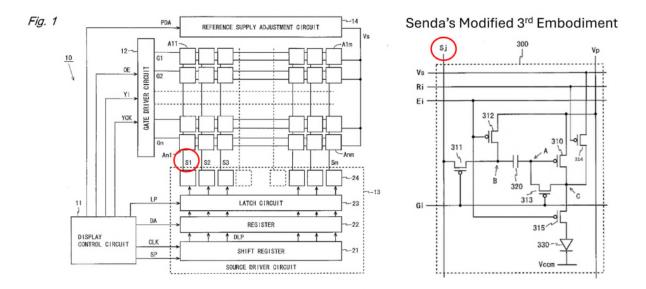

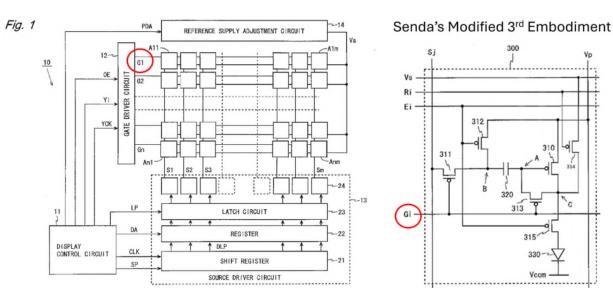

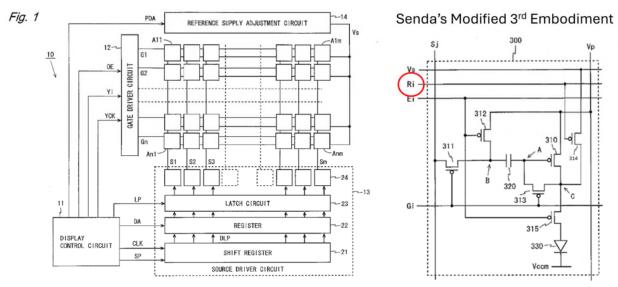

#### 10. [17i]