# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD

SAMSUNG ELECTRONICS CO., LTD., SAMSUNG ELECTRONICS AMERICA, INC., SAMSUNG SEMICONDUCTOR, INC., and SAMSUNG AUSTIN SEMICONDUCTOR LLC,

Petitioner,

v.

**W&WSENS DEVICES INC.,**

Patent Owner.

Case IPR2025-00995 Patent No. 10,468,543

\_\_\_\_

PETITION FOR INTER PARTES REVIEW

# TABLE OF CONTENTS

| I.   | Preli                                  | minary  | nary Statement1 |                                                                                                                                                                                                  |    |

|------|----------------------------------------|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| II.  | State                                  | of the  | Art             |                                                                                                                                                                                                  | 2  |

|      | A.                                     | Photo   | odetect         | ors                                                                                                                                                                                              | 2  |

|      | B.                                     | Micr    | ostruct         | ure-Enhanced Photodetectors                                                                                                                                                                      | 3  |

| III. | The                                    | '543 P  | atent           |                                                                                                                                                                                                  | 5  |

|      | A.                                     | Spec    | ificatio        | n                                                                                                                                                                                                | 5  |

|      | B.                                     | Clair   | n Cons          | truction                                                                                                                                                                                         | 6  |

| IV.  | State                                  | ment o  | of Preci        | se Relief Requested                                                                                                                                                                              | 7  |

|      | A.                                     | Prior   | Art             |                                                                                                                                                                                                  | 7  |

|      | B.                                     | Chal    | lenges          |                                                                                                                                                                                                  | 7  |

| V.   | Leve                                   | l of Oı | dinary          | Skill in the Art                                                                                                                                                                                 | 8  |

| VI.  | The Challenged Claims Are Unpatentable |         |                 |                                                                                                                                                                                                  | 8  |

|      | A.                                     | 30, 3   | 2, and          | A/1B: Claims 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-35 Are Anticipated by <i>Kuboi</i> (Ground 1A) and er <i>Kuboi</i> (Ground 1B)                                                                | 8  |

|      |                                        | 1.      | Over            | view of <i>Kuboi</i>                                                                                                                                                                             | 8  |

|      |                                        | 2.      | Indep           | pendent Claim 1                                                                                                                                                                                  | 14 |

|      |                                        |         | a.              | [1pre(a)]: "A single-chip device comprising an integrated combination of a microstructure-enhanced photodetector (MSPD) configured for reverse-bias operation and an active electronic circuit," | 14 |

|      |                                        |         | b.              | [1pre(b)]: "both formed on or in a single substrate"                                                                                                                                             | 22 |

| c. | input that in cross-section is substantially continuous spatially, convert the optical input to an electrical output, and process the electrical output into a processed output, wherein:"                                                         | 25 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| d. | [1a]: "the MSPD on or in said single substrate comprises an intermediate region, a first region at one side of the intermediate region, and a second region at an opposite side of the intermediate region, wherein:"                              | 32 |

| e. | [1b]: "each of the regions comprises Silicon,<br>Germanium, or an alloy thereof;"                                                                                                                                                                  | 33 |

| f. | [1c]: "at least one of said regions, and an optional overlying covering region, have holes intentionally formed therein"                                                                                                                           | 34 |

| g. | [1d]: "each of the first and second regions comprises a doped material;"                                                                                                                                                                           | 39 |

| h. | [1e]: "the intermediate region comprises a material that is less doped than at least one of the first and second regions or is undoped, wherein the degree of doping is the same or different for different positions in the intermediate region;" | 40 |

| i. | [1f]: "an input portion configured to concurrently receive at a plurality of said holes said optical input that has said substantially continuous crosssection; and"                                                                               | 42 |

| j. | [1g]: "an output portion configured to provide said electrical output from the MSPD;"                                                                                                                                                              | 45 |

| k. | [1h]: "the MSPD includes reverse-bias contacts coupled therewith to establish an electrical field therein when energized to thereby sweep in a selected direction electrical charges generated in the MSPD by said optical input:"                 | 47 |

|    | 1.    | [1i]: "the active electronic circuit on or in said single substrate is configured to process the electrical output from the MSPD by applying thereto:"                                     | 50 |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | m.    | [1j]: "amplification to form said processed output from the single-chip device;"                                                                                                           | 53 |

|    | n.    | [1k]: "processing other than or in addition to amplification to form said processed output from the single-chip device; and"                                                               | 56 |

|    | 0.    | [11]: "routing to one or more selected destinations; and"                                                                                                                                  | 57 |

|    | p.    | [1m]: "a communication channel on or in said single-chip device, configured to deliver the electrical output from the MSPD to the active electronic circuit."                              | 61 |

| 3. | Claim | 2                                                                                                                                                                                          | 63 |

|    | a.    | [2]: "The single-chip device of claim 1, in which said active electronic circuit at least partly extends beyond said substrate."                                                           | 63 |

| 4. | Claim | 3                                                                                                                                                                                          | 66 |

|    | a.    | [3]: "The single-chip device of claim 1, in which said active electronic circuit is at least partly inside said substrate."                                                                | 66 |

| 5. | Claim | ı 4                                                                                                                                                                                        | 67 |

|    | a.    | [4]: "The single-chip device of claim 1, in which said overlying region is present as a superstrate at one side of said first, intermediate, and second regions, and contains said holes." | 67 |

| 6. | Claim | ı 7                                                                                                                                                                                        | 68 |

|     | a.    | [7]: "The single-chip device of claim 1, further including a region of a dielectric material that covers the holes and is in the propagation path of said optical input."                                                                                                                                                                                                                | 68 |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.  | Clain | 1 9                                                                                                                                                                                                                                                                                                                                                                                      | 72 |

|     | a.    | [9]: "The single-chip device of claim 1, in which said holes are present in said intermediate region."                                                                                                                                                                                                                                                                                   | 72 |

| 8.  | Clain | ı 10                                                                                                                                                                                                                                                                                                                                                                                     | 73 |

|     | a.    | [10]: "The single-chip device of claim 1, in which said holes are present in said intermediate region as well as in at least one of the first and second regions."                                                                                                                                                                                                                       | 73 |

| 9.  | Claim | n 11                                                                                                                                                                                                                                                                                                                                                                                     | 75 |

|     | a.    | [11]: "The single-chip device of claim 1, in which said holes are present in each of the first, second, and intermediate region."                                                                                                                                                                                                                                                        | 75 |

| 10. | Claim | n 12                                                                                                                                                                                                                                                                                                                                                                                     | 75 |

|     | a.    | [12]: "The single-chip device of claim 1, in which each of said first and second regions and said intermediate region has a thickness and at least some of said holes extend through the entire thickness of said intermediate region and of one of said first region and second region and through at least a part of the thickness of the other one of said first and second regions." | 75 |

| 11. | Clain | ı 16                                                                                                                                                                                                                                                                                                                                                                                     | 78 |

|     | a.    | [16]: "The single-chip device of claim 1, in which at least some of said holes have sidewalls that slope in planes transverse to said regions."                                                                                                                                                                                                                                          | 78 |

| 12  | Clair | . 17                                                                                                                                                                                                                                                                                                                                                                                     | 82 |

|     | a.    | [17]: "The single-chip device of claim 1, in which at least some of said holes have sidewalls with plural different slopes along the inside walls of the holes."                                            | 82 |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 13. | Claim | ı 20                                                                                                                                                                                                        | 83 |

|     | a.    | [20]: "The single-chip device of claim 1, in which the holes are at least partly filled with a dielectric material."                                                                                        | 83 |

| 14. | Claim | n 21                                                                                                                                                                                                        | 85 |

|     | a.    | [21]: "The single-chip device of claim 1, in which the holes are entirely filled with a dielectric material."                                                                                               | 85 |

| 15. | Claim | ı 24                                                                                                                                                                                                        | 87 |

|     | a.    | [24]: "The single-chip device of claim 1, in which said MSPD further comprises ohmic contacts configured for reverse-biasing the MSPD."                                                                     | 87 |

| 16. | Claim | n 25                                                                                                                                                                                                        | 89 |

|     | a.    | [25]: "The single-chip device of claim 1, in which the MSPD further includes ohmic contacts to said first and second regions, at least one of said ohmic contact[s] being through a via in said substrate." | 89 |

| 17. | Claim | n 26                                                                                                                                                                                                        | 94 |

|     | a.    | [26a]: "The single-chip device of claim 1, further comprising a light guide to said MSPD for directing said optical input thereto,"                                                                         | 94 |

|     | b.    | [26b]: "and electrical contacts from the active electronic circuit configured to carry said processed output out of the single-chip device."                                                                | 96 |

| 18  | Claim | 1.28                                                                                                                                                                                                        | 98 |

|     | a.    | [28a]: "The single-chip device of claim 1, further comprising one or more additional MSPD on or in the same substrate,"                                                                                                                                                                                                                                                         | 98   |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|     | b.    | [28b]: "and respective different optical bandpass filters coupled with at least two of the MSPDs on or in said single substrate, whereby at least two of said MSPDs are configured to respond to different wavelength ranges that are within said optical input."                                                                                                               | 101  |

| 19. | Claim | ı 29                                                                                                                                                                                                                                                                                                                                                                            | 103  |

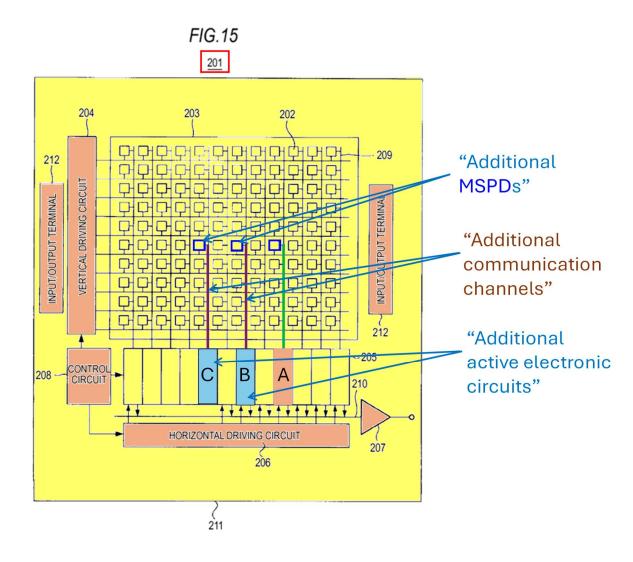

|     | a.    | [29]: "The single-chip device of claim 1, further comprising one or more additional MSPDs on or in said single substrate, one or more additional active electronic circuits on or in the said single substrate, and one or more additional communication channels configured to supply electrical outputs from the MSPDs to the one or more of the active electronic circuits." | 103  |

| 20. | Claim | n 30                                                                                                                                                                                                                                                                                                                                                                            | 107  |

|     | a.    | [30]: "The single-chip device of claim 1, further comprising one or more additional active electronic circuits that are formed on or in the said single substrate."                                                                                                                                                                                                             | 107  |

| 21. | Claim | n 32                                                                                                                                                                                                                                                                                                                                                                            | 107  |

|     | a.    | [32]: "The single-chip device of claim 1, further comprising one or more additional active electronic circuits that are formed on or in the said single substrate and comprise one or more of CMOS, BiCMOS, and bipolar active devices."                                                                                                                                        | 107  |

| 22. | Claim | n 35                                                                                                                                                                                                                                                                                                                                                                            | .108 |

|     | a.    | [35]: "The single-chip device of claim 1, further including a region of selected material that is over                                                                                                                                                                                                                                                                          |      |

|       |      | a side of one of the first and second regions facing away from the intermediate region and is configured to reduce sheet resistance." | 108 |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| VII.  | Mand | latory Notices                                                                                                                        | 110 |

|       | A.   | Real Parties-in-Interest.                                                                                                             | 110 |

|       | B.   | Related Matters                                                                                                                       | 110 |

|       | C.   | Lead and Backup Counsel, and Service Information                                                                                      | 111 |

| VIII. | Grou | nds for Standing                                                                                                                      | 112 |

| IX.   | Conc | lusionlusion                                                                                                                          | 113 |

# PETITIONER'S EXHIBIT LIST

| Exhibit | Description                                                                                                                                                                                |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ex-1001 | U.S. Patent No. 10,446,700 B2 to Wang et al. ("'700 Patent")                                                                                                                               |  |  |

| Ex-1002 | Reserved                                                                                                                                                                                   |  |  |

| Ex-1003 | Prosecution History of the '700 Patent (downloaded from Public PAIR)                                                                                                                       |  |  |

| Ex-1004 | U.S. Patent Application Publication No. 2012/0049044 A1 to Kuboi (" <i>Kuboi</i> ")                                                                                                        |  |  |

| Ex-1005 | U.S. Patent Application Publication No. 2012/0033119 A1 to Shinohara ("Shinohara")                                                                                                         |  |  |

| Ex-1006 | European Patent Application EP 2 172 974 A1 to NXP B.V. ("NXP")                                                                                                                            |  |  |

| Ex-1007 | U.S. Patent Application Publication No. 2008/0259981 A1 to Wang et al. ("Wang")                                                                                                            |  |  |

| Ex-1008 | U.S. Patent Application Publication No. 2009/0133741 A1 to Higuchi et al. ("Higuchi")                                                                                                      |  |  |

| Ex-1009 | Tapan K. Gupta, <i>Copper Interconnect Technology</i> , (Springer Science+Business Media, LLC 2009), pp. 67-71.                                                                            |  |  |

| Ex-1010 | Zhihong Huang et al., <i>Microstructured silicon photodetector</i> , Applied Physics Letter, Vol. 89 (2006), pp. 033506-1 to -3.                                                           |  |  |

| Ex-1011 | Richard A. Myers et al., <i>Enhancing near-infrared avalanche photodiode performance by femtosecond laser microstructuring</i> , Applied Optics, Vol. 45, No. 35 (Dec. 2006), pp. 8825-31. |  |  |

| Ex-1012 | Abbas El Gamal et al., <i>CMOS Image Sensors</i> , IEEE Circuits & Devices Magazine (2005), pp. 6-20.                                                                                      |  |  |

| Ex-1013 | Eric R. Fossum, <i>CMOS Image Sensors: Electronic Camera-On-A-Chip</i> , IEEE Transactions on Electron Devices, Vol. 44, No. 10 (Oct. 1997), pp. 1689-98.                                  |  |  |

| Ex-1014 | Sunetra Mendis et al., <i>CMOS Active Pixel Image Sensor</i> , IEEE Transactions on Electron Devices, Vol. 41, No. 3 (Mar. 1994), pp. 452-53.                                              |  |  |

| Exhibit | Description                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ex-1015 | Renato Turchetta et al., <i>Introduction to CMOS Image Sensors</i> , Molecular Expressions <sup>TM</sup> Optical Microscopy Primer: Digital Imaging in Optical Microscopy - Introduction to CMOS Image Sensors (July 16, 2004), pp. 1-9, <i>available at</i> https://web.archive.org/web/20120508153832/https://micro.magne t.fsu.edu/primer/digitalimaging/cmosimagesensors.html |  |

| Ex-1016 | Ming-Dou Ker et al., <i>Investigation on Device Characteristics of MOSFET Transistor Placed Under Bond Pad for High-Pin-Count SOC Applications</i> , IEEE Transactions on Components and Packaging Technologies, Vol. 27, No. 3 (Sept. 2004), pp. 452-60.                                                                                                                         |  |

| Ex-1017 | Paul Horowitz et al., <i>The Art of Electronics</i> (Cambridge University Press, New York 3d ed. 2016), pp. 1, 11, 52, 71.                                                                                                                                                                                                                                                        |  |

| EX-1018 | Electrical Engineering Dictionary - CRCnetBase (Phillip A. Laplante editor-in-chief, CRC Press LLC 2000), pp. 1-6.                                                                                                                                                                                                                                                                |  |

| Ex-1019 | S.M. Sze et al., <i>Semiconductor Devices - Physics and Technology</i> (John Wiley & Sons, Inc. 3d ed. 2012), pp. 205-10, 325-26, 392-400, 416-417, 466-67.                                                                                                                                                                                                                       |  |

| Ex-1020 | John P. Uyemura, <i>CMOS Logic Circuit Design</i> (Kluwer Academic Publishers 2002), pp. 64, 74-102, 315-17, 458-60.                                                                                                                                                                                                                                                              |  |

| Ex-1021 | Khalil Jumah Tawfiq Hamam, Organic Solar Cells Based on High Dielectric Constant Materials: An Approach to Increase Efficiency (June 2013) (Ph.D. dissertation, Western Michigan University), pp. 1-122.                                                                                                                                                                          |  |

| Ex-1022 | P. Kalugasalam et al., <i>Dielectric and AC Conduction Studies of Lead Phthalocyanine Thin Film</i> , Chalcogenide Letters, Vol. 6, No. 9 (Sept. 2009), pp. 469-76.                                                                                                                                                                                                               |  |

| Ex-1023 | Gopal G. Pethuraja et al., <i>Current-Voltage Characteristics of ITO/p-Si and ITO/n-Si Contact Interfaces</i> , Advances in Materials Physics and Chemistry, Vol. 2 (2012), pp. 59-62.                                                                                                                                                                                            |  |

| Ex-1024 | Giampiero de Cesare et al., Electrical Properties of ITO/Crystalline-Silicon Contact at Different Deposition Temperatures, IEEE Electron Device Letters, Vol. 33, No. 3 (Mar. 2012), pp. 327-29.                                                                                                                                                                                  |  |

| Exhibit | Description                                                                                                                                                                                                           |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ex-1025 | Wen-Jang Jiang et al., <i>The effect of indium tin oxide as an ohmic contact for the 850 nm GaAs oxide-confined VCSELs</i> , Solid-State Electronics, Vol. 46 (2002), pp. 1945-48.                                    |  |  |

| Ex-1026 | IEEE 100 - The Authoritative Dictionary of IEEE Standard Terms, IEEE (7th ed. 2000), pp. 333, 1205.                                                                                                                   |  |  |

| Ex-1027 | Christian C. Fesenmaier et al., <i>Optical confinement methods for continued scaling of CMOS image sensor pixels</i> , Optics Express, Vol. 16, No. 25 (Dec. 2008), pp. 20457-64.                                     |  |  |

| Ex-1028 | Leonard Rubin et al., <i>Ion Implantation in Silicon Technology</i> , Industrial Physicist, 9(3), (Jun/July 2003), pp. 12-15.                                                                                         |  |  |

| Ex-1029 | Jurgen Michel et al., <i>Advances in fully CMOS integrated photonic devices</i> , Proceedings of SPIE, Vol. 6477 (2007), pp. 64770P-1 to -11.                                                                         |  |  |

| Ex-1030 | Mark Beals et al., <i>Process Flow Innovations for Photonic Device Integration in CMOS</i> , Proceedings of SPIE, Vol. 6898 (2008), pp. 689804-1 to -14.                                                              |  |  |

| Ex-1031 | Donald A. Neaman, <i>Semiconductor Physics and Devices – Basic Principles</i> (McGraw Hill 3d ed. 2003), pp. 247-50, 260-61.                                                                                          |  |  |

| Ex-1032 | Adel S. Sedra et al., <i>Microelectronic Circuits</i> (Oxford University Press 7th ed. 2015), pp. 155-56.                                                                                                             |  |  |

| Ex-1033 | Chung-Wei Chang et al., <i>High Sensitivity of Dielectric films</i> Structure for Advanced CMOS Image Sensor Technology, 2007  International Image Sensor Workshop, IEEE Electron Devices Society (2007), pp. 207-10. |  |  |

| Ex-1034 | Matthew Sauceda, <i>Porphyrin Thin Film Dielectrics</i> , SUNFEST Technical Report TR-CST01NOV04, Center for Sensor Technologies, Univ. of Pennsylvania, Philadelphia, PA (2004), pp. 181-98.                         |  |  |

| Ex-1035 | N. Venkatramaiah et al., Spectroscopic and dielectric studies of meso-tetrakis(p-sulfonatophenyl) porphyrin doped hybrid borate glasses, Journal of Alloys and Compounds, Vol. 509 (2011), pp. 2797-803.              |  |  |

| Exhibit | Description                                                                                                                                                                                                                                      |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ex-1036 | Tom J. Savenije, <i>Photogeneration and transport of charge carriers in a porphyrin p/n heterojunction</i> , Physical Review B, Vol. 55, No. 15 (Apr. 1997), pp. 9685-92.                                                                        |  |

| Ex-1037 | Ümit Salan et al., Synthesis, characterization, electrical and dielectric permittivity measurements of 2,9,16,23-tetra(4-ferrocenylimino-3-nitrophenoxy)phthalocyanines, Journal of Porphyrins and Phthalocyanines, Vol. 10 (2006), pp. 1263-70. |  |

| Ex-1038 | Teresa M. Figueira-Duarte et al., <i>Pyrene-Based Materials for Organic Electronics</i> , Chemical Reviews, Vol. 111 (2011), pp. 7260-314.                                                                                                       |  |

| Ex-1039 | Handbook of Wafer Bonding (Peter Ramm et al. eds., Wiley-VCH Verlag & Co. KGaA (2012), pp. 52-54, 63-64, 112-15.                                                                                                                                 |  |

| Ex-1040 | Reserved                                                                                                                                                                                                                                         |  |

| Ex-1041 | Reserved                                                                                                                                                                                                                                         |  |

| Ex-1042 | U.S. Patent No. 10,468,543 B2 to Wang et al. ("'543 Patent")                                                                                                                                                                                     |  |

| Ex-1043 | Declaration of Dr. Michael Lebby                                                                                                                                                                                                                 |  |

| Ex-1044 | Prosecution History of the '543 Patent (downloaded from Public PAIR)                                                                                                                                                                             |  |

| Ex-1045 | J. W. Levell et al., <i>A hybrid organic semiconductor/silicon photodiode for efficient ultraviolet photodetection</i> , Optics Express, Vol. 18, No. 4 (2010), pp. 3219-3225.                                                                   |  |

| Ex-1046 | W&Wsens Devices Inc. v. Samsung Electronics Co. Ltd. et al.,<br>Case No. 2:24-cv-00854, Plaintiff's Infringement Contentions,<br>Appendix C-1 (Jan. 7, 2025)                                                                                     |  |

| Ex-1047 | W&Wsens Devices Inc. v. Samsung Electronics Co. Ltd. et al.,<br>Case No. 2:24-cv-00854, Plaintiff's Infringement Contentions,<br>Appendix C-2 (Jan. 7, 2025)                                                                                     |  |

## I. Preliminary Statement

Petitioner Samsung Electronics Co., Ltd.; Samsung Electronics America, Inc.; Samsung Semiconductor, Inc.; and Samsung Austin Semiconductor LLC (collectively, "Samsung") requests *inter partes* review of U.S. Patent No. 10,468,543 (Ex-1042) and cancellation of claims 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35.

The challenged claims pertain to a single-chip device with a photodetector with CMOS signal processing circuitry on a single substrate. This photodetector, called a microstructure-enhanced photodetector (alternatively, "MSPD") in the '543 Patent, features etched holes to increase light absorption. However, integration of photodetectors (even MSPDs) with CMOS signal processing circuitry on the same substrate was widely known and was a common characteristic of CMOS image sensors well before the alleged invention date. For example, *Kuboi* (Ex-1004), which was not considered by the Examiner during prosecution, discloses and renders obvious all recited features of the claimed single-chip device.

As detailed below and in the supporting declaration of Dr. Michael Lebby, Ph.D. ("Lebby") (Ex-1043), the challenged claims are unpatentable over *Kuboi*. Lebby, ¶¶1-248. The Board should institute review and cancel all challenged claims.

## II. State of the Art

#### A. Photodetectors

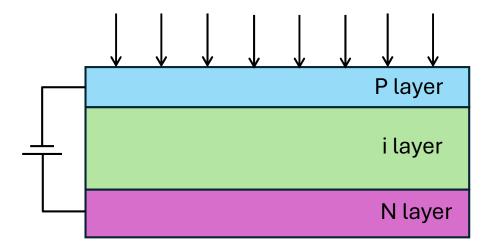

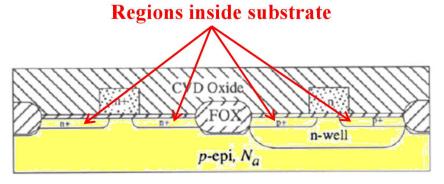

A photodetector is a semiconductor device that transforms photons into electrical signals, enabling electrical circuits to detect and measure incident light. Lebby, ¶51. As illustrated below, a PiN photodetector is a specific type of photodiode characterized by an intrinsic (undoped) layer positioned between highly doped P-type and N-type semiconductor layers (hence the name "PIN"):

Lebby, ¶51. When light enters the photodetector, photons are absorbed in the intrinsic layer, generating electron-hole pairs. Lebby, ¶52. Applying a negative bias across the photodetector causes the separated electrons to move towards the N-type layer and the holes towards the P-type layer, producing a measurable photocurrent. Lebby, ¶52.

#### **B.** Microstructure-Enhanced Photodetectors

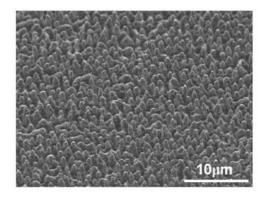

Conventional silicon photodetectors exhibit high responsivity at wavelengths of light less than about 850 nm. Ex-1010, 1; Lebby, ¶53. The prior art recognized that tailoring the microstructure of silicon can extend the operability of these photodetectors to longer wavelengths, such as infrared. Lebby, ¶53. For instance, etching the surface of a silicon photodetector to create micron-sized pillars/ grooves was known to enhance a photodetector's responsiveness at longer wavelengths. Ex-1010, 1-2; Ex-1011, 1-6; Lebby, ¶53. The images below illustrate photodiodes with laser-etched microstructures designed to enhance responsiveness at longer wavelengths. Lebby, ¶¶53-54.

FIG. 1. Scanning electron micrographs of microstructured Si surface.

Fig. 1. (Color online) Picture of two microstructured APD arrays prior to packaging. Structuring was performed with an 800 nm fs laser operating at a fluence of 3.5 kJ/m² in an atmosphere of SF<sub>6</sub>. The array on the right had four different structured regions with a pulse number ranging from 0 to 300. The shiny area is the bare silicon.

Ex-1010, 1 (left); Ex-1011, 2 (right).

Photodetectors featuring microstructures enhanced by etched holes were widely known and utilized well before the purported invention. Lebby, ¶¶54-56.

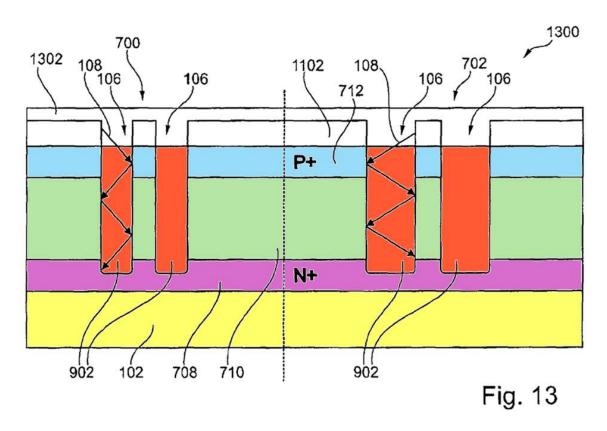

For example, *NXP* (Ex-1006) discloses a single-chip device 1300 where a silicon PiN photodiode is integrated with CMOS signal processing circuitry (not shown below) on the same substrate 102. *NXP*, ¶¶[15], [32], [42], [85].

*NXP*, Fig. 13.<sup>1</sup> The PiN photodiode above includes an intrinsic layer 710 disposed between an N<sup>+</sup> layer 708 and a P<sup>+</sup> layer 712 and holes or pores 106 formed on the PiN layers by etching. *NXP*, ¶¶[77]-[78]. *NXP* discloses that the presence of pores 106 increases the quantum efficiency of the photodiode. *NXP*, ¶¶[13], [38]; Lebby, ¶55.

<sup>&</sup>lt;sup>1</sup> All color and colored annotations in figures have been added.

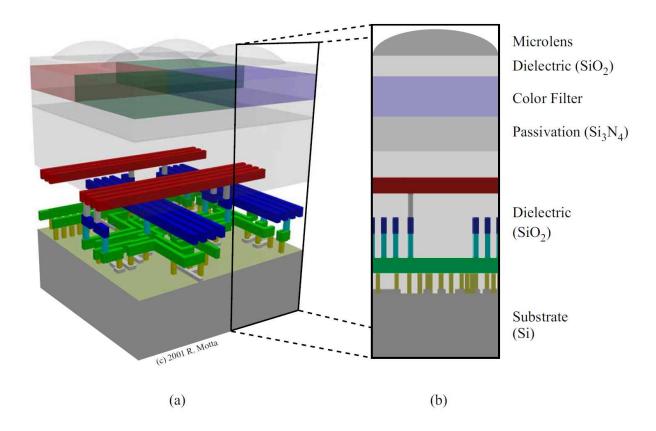

The integration of photodetectors and signal processing circuitry on a single substrate to form a single-chip device was also known long before the purported invention date of the '543 Patent. Lebby, ¶¶57-65; Ex-1012, 1-14; Ex-1013, 1-8; Ex-1014, 1-2; Ex-1015, 1-5; *NXP*, ¶¶[16], [32]-[37].

#### III. The '543 Patent

## A. Specification

The '543 Patent details a single-chip device that integrates photodetectors (referred to as MSPDs and MSAPDs) with CMOS active electronic circuits on a single substrate. '543 Patent, 2:64-67, 4:65-5:5, 6:24-29; Lebby, ¶¶66-68.

The disclosed photodetectors include a silicon substrate with a first layer (a P layer), a very low doped N or P layer called the intermediate layer (or I layer), and a second layer (an N layer) with holes etched in one or more of the PiN layers. '543 Patent, 16:38-42, 22:9-41, 26:42-27:4. Optical signals impinge on the top and/or bottom surfaces of the photodetectors. '543 Patent, 16:23-27. According to the '543 Patent, because of the holes, light interacts with the absorbing layer(s) for a longer length of time, resulting in enhanced light absorption and a larger external quantum efficiency over a similar structure without holes. '543 Patent, 15:48-56, Abstract.

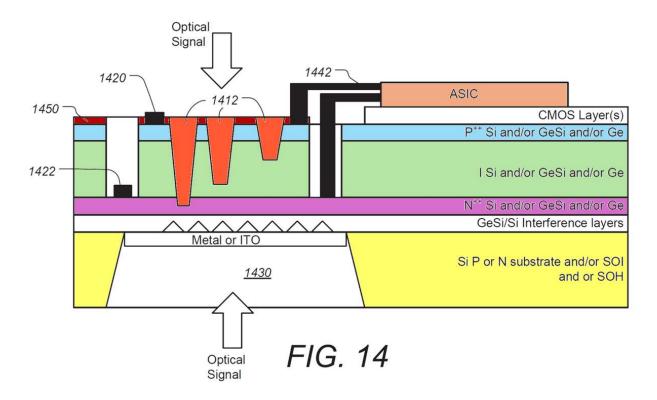

Figure 14, reproduced below, illustrates the disclosed photodetector:

'543 Patent, Fig. 14, 10:60-62, 26:42-44. The photodetector is monolithically integrated with signal processing circuits (such as ASIC) on the same substrate to form a single-chip device. '543 Patent, 19:2-6, 23:43-46, 26:42-44, Lebby, ¶68. Notably, the '543 Patent acknowledges that it was well known to integrate photodetectors with signal processing circuits on a single silicon substrate to reduce cost and improve performance. '543 Patent, 28:58-29:3, 32:50-67, 47:11-21.

#### **B.** Claim Construction

The Board construes claims per *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005) (en banc). 37 C.F.R. §42.100(b). Claims must be construed only to the extent necessary to resolve a controversy. *Nidec Motor Corp. v. Zhongshan Broad*

*Ocean Motor Co.*, 868 F.3d 1013, 1017 (Fed. Cir. 2017). Here, no terms need construction to resolve the controversy.<sup>2</sup>

## IV. Statement of Precise Relief Requested

#### A. Prior Art

The application that resulted in the '543 Patent was filed on March 8, 2019, claiming priority to multiple patent applications, the earliest of which was filed on May 22, 2013.<sup>3</sup> Thus, the earliest claimed priority date is May 22, 2013.

Kuboi (Ex-1004), U.S. Patent Publication No. 2012/0049044, which published on March 1, 2012, is prior art under 35 U.S.C. §102(a)(1) and §102(a)(2).

## B. Challenges

| Ground | Challenged Claims                                    | Basis | Prior Art |

|--------|------------------------------------------------------|-------|-----------|

| 1A     | 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35 | §102  | Kuboi     |

| 1B     | 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35 | §103  | Kuboi     |

<sup>&</sup>lt;sup>2</sup> Petitioner retains the right to contend in another proceeding that certain limitations are indefinite.

<sup>&</sup>lt;sup>3</sup> Petitioner retains the right to dispute the claimed priority in another proceeding.

## V. Level of Ordinary Skill in the Art

A person of ordinary skill in the art ("POSITA") would have had at least a master's degree in electrical engineering or a similar field and at least five years of experience working with semiconductor systems and semiconductor devices.

Lebby, ¶¶85-87. Additional relevant work experience can compensate for less education and vice versa. Lebby, ¶86.

## VI. The Challenged Claims Are Unpatentable

A. Grounds 1A/1B: Claims 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35 Are Anticipated by *Kuboi* (Ground 1A) and Obvious over *Kuboi* (Ground 1B)

#### 1. Overview of *Kuboi*

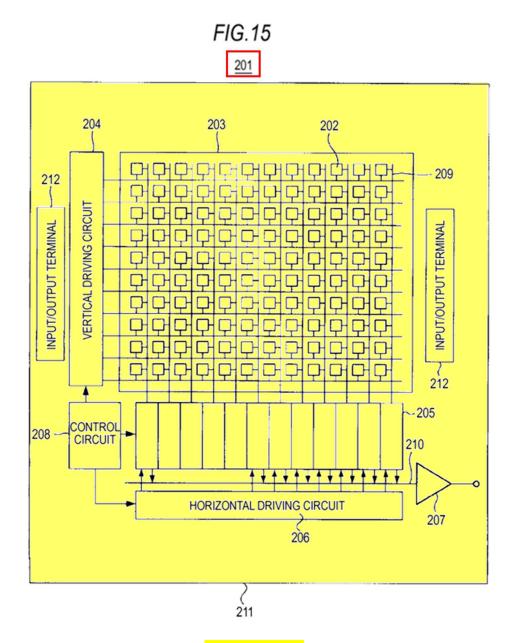

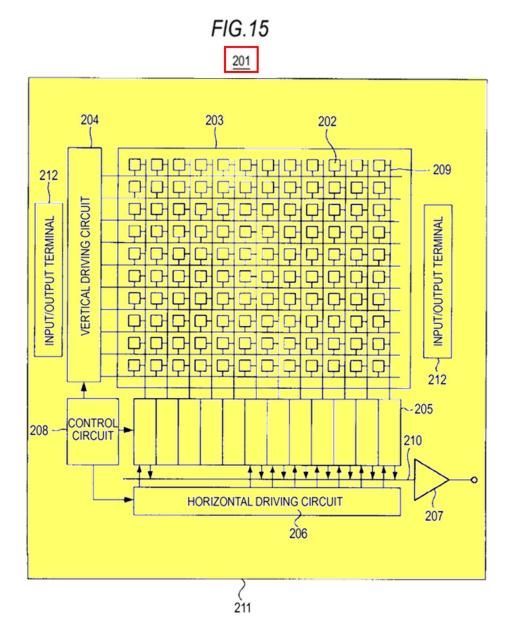

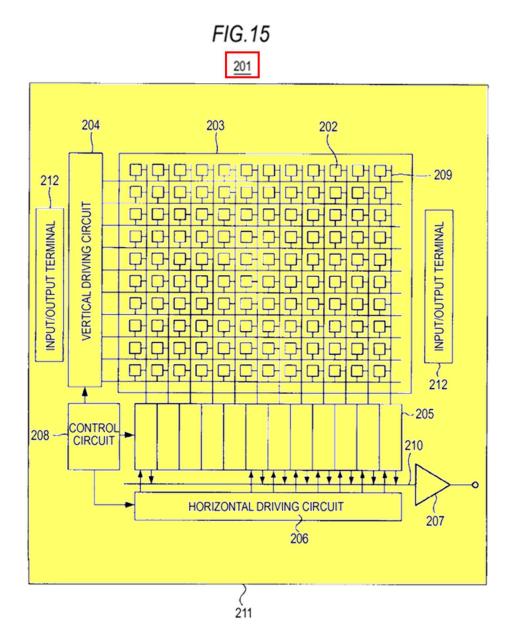

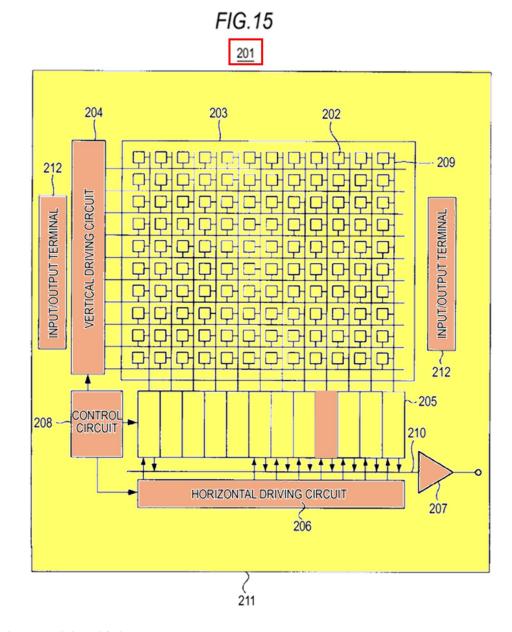

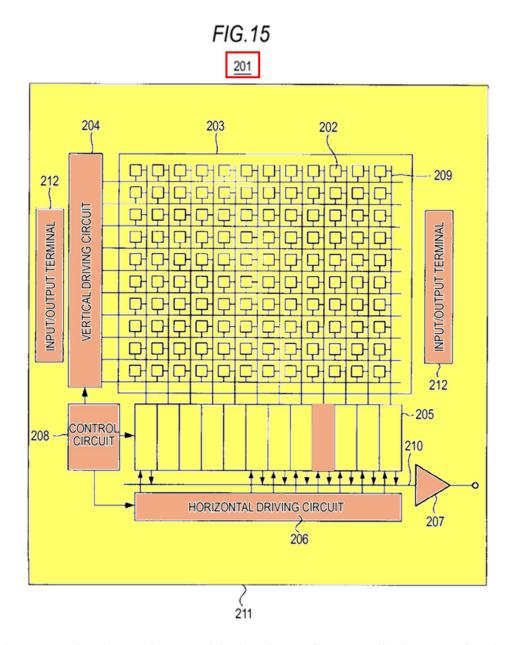

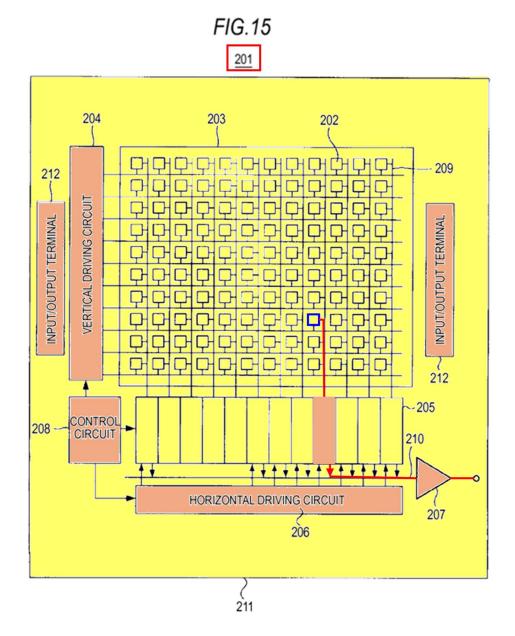

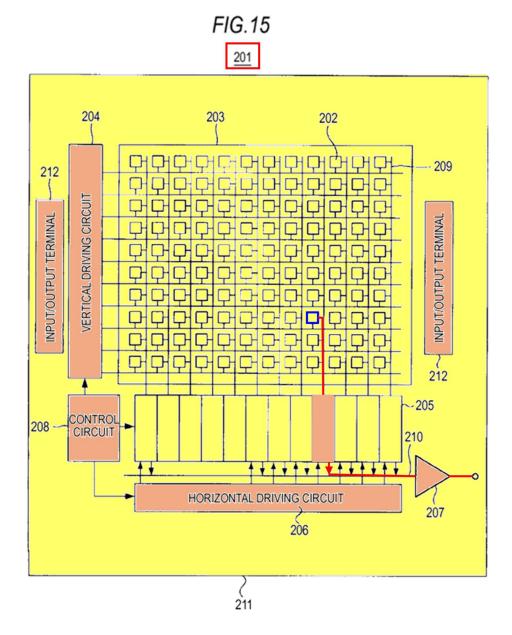

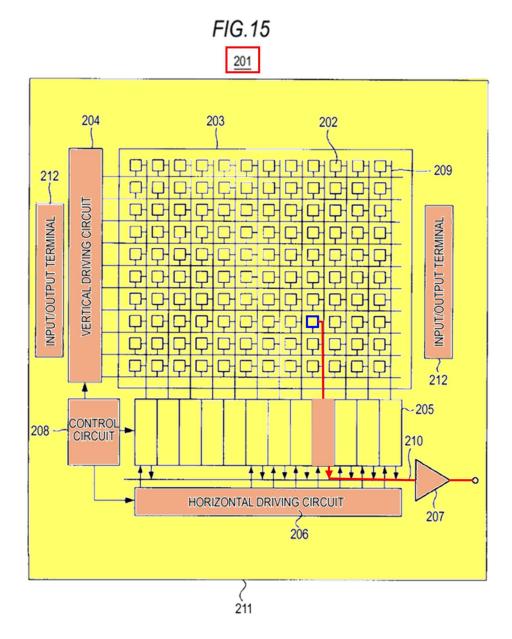

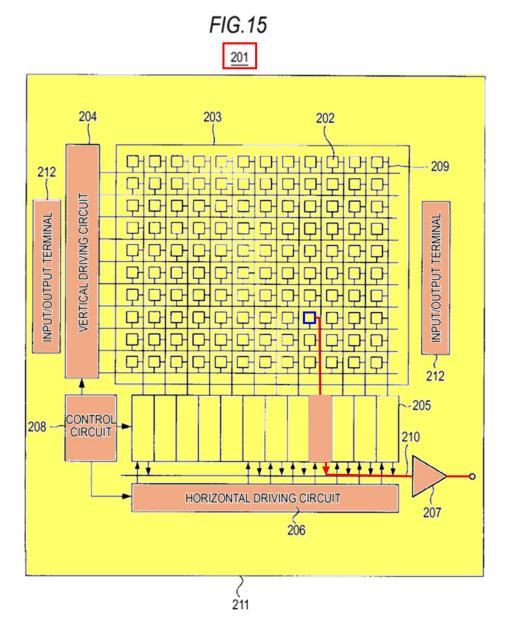

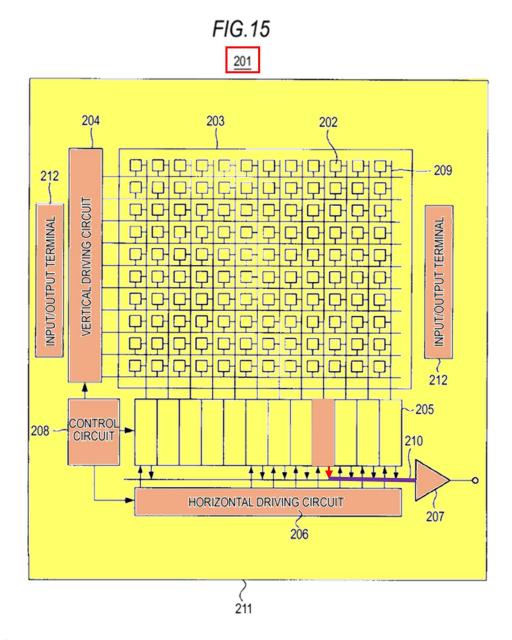

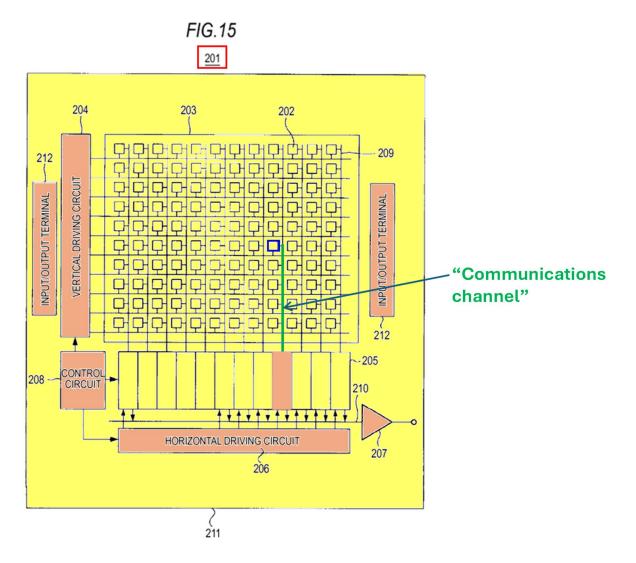

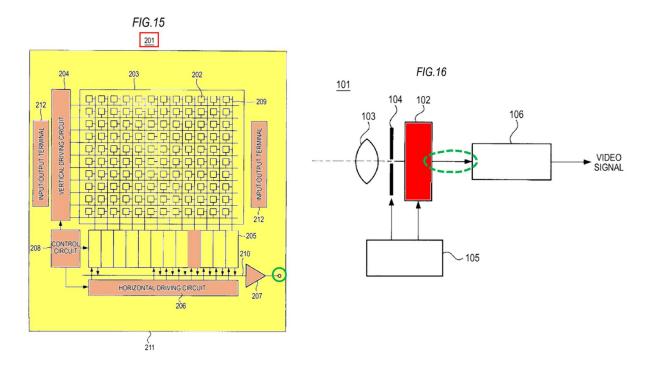

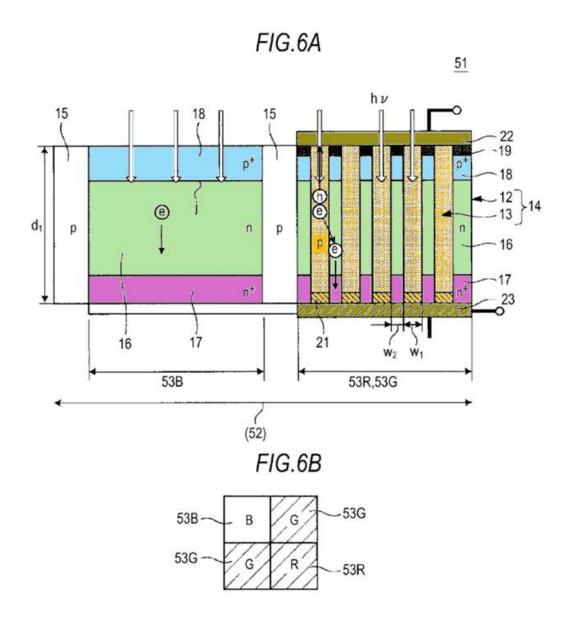

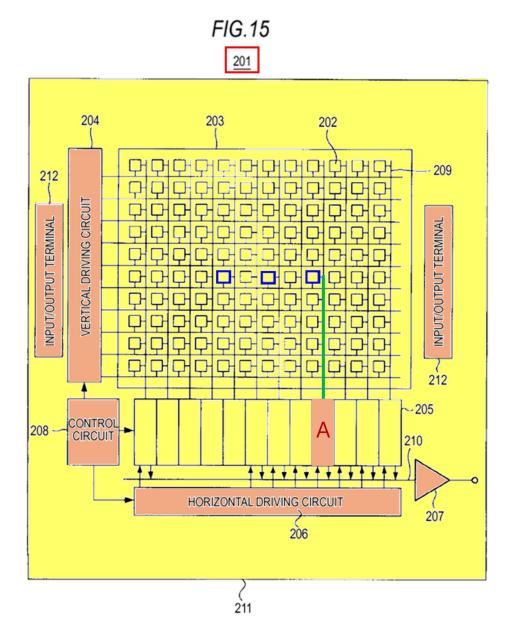

Kuboi discloses a CMOS solid-state imaging device 201 that includes a pixel region 203 and a peripheral circuit portion on a single semiconductor substrate 211. Kuboi, ¶[48], Fig. 15.

*Kuboi*, Fig. 15. Pixel region 203 of substrate 211 comprises a plurality of pixels 202 arranged in a two-dimensional array. *Kuboi*, ¶[48]. Each pixel 202 contains one photoelectric conversion portion (or a photodiode) and four pixel transistors. *Kuboi*, ¶[48]. The peripheral circuit portion includes "logic[] circuits" (such as a vertical driving circuit 204, column signal processing circuits 205, horizontal

driving circuit 206, output circuit 207, and control circuit 208), which process the electrical output of the pixels and then output it. Kuboi, ¶¶[49]-[54]; Lebby, ¶¶76-78. The pixels and the peripheral circuit portion are fabricated on a single substrate, and the pixel transistors are fabricated on another substrate and the two substrates are bonded together. Kuboi, ¶¶[62], [70], [78]; Lebby, ¶78.

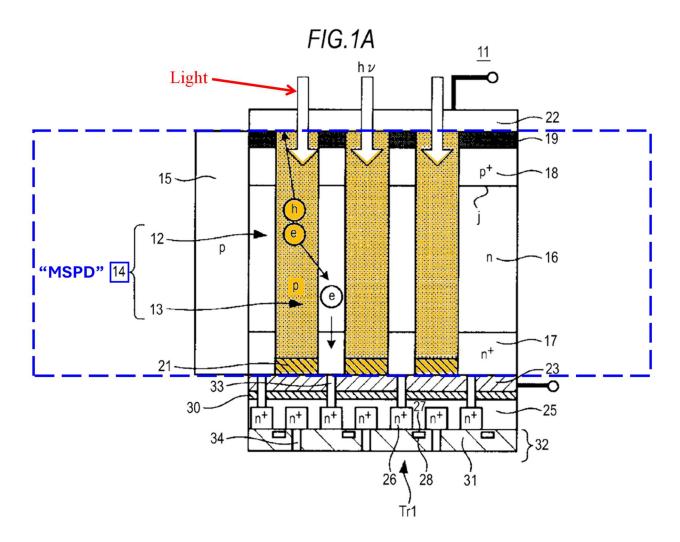

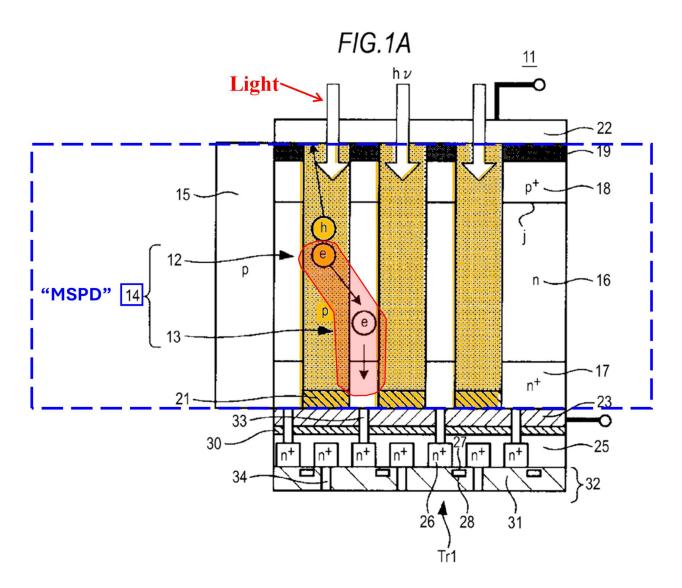

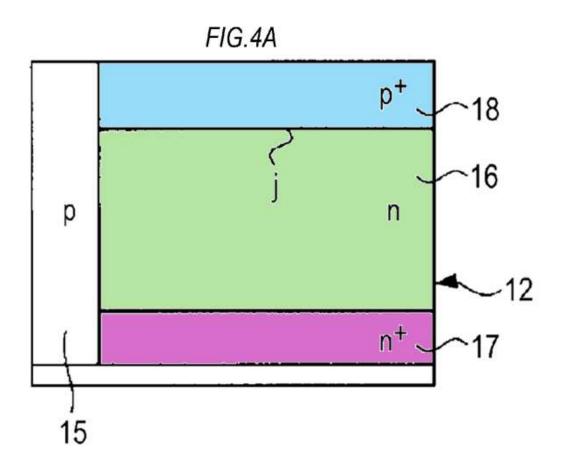

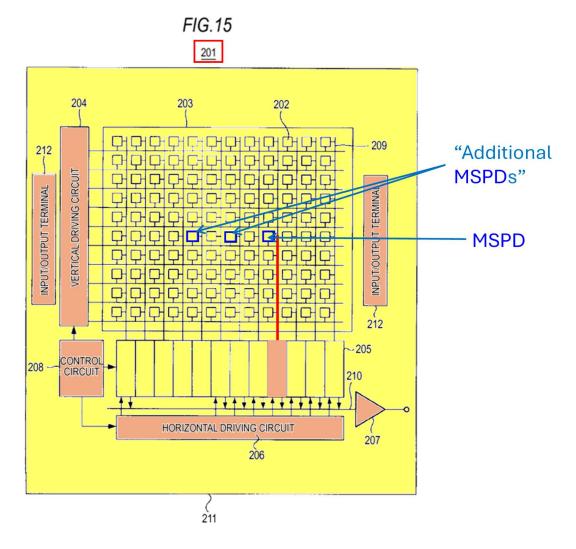

Kuboi describes photoelectric conversion portions suitable for use in imaging device 201. Kuboi, ¶[48]; Lebby, ¶79. For example, Kuboi discloses a basic pixel configuration with reference to Figures 1A/1B. Kuboi, ¶[55]. Kuboi likewise discloses a pixel configuration in Figures 6A/6B, explaining that the disclosed red and green pixels 53R and 53G have a structure that is the same as the basic configuration of Figures 1A/1B. *Kuboi*, ¶¶[90], [95], [69]. *Kuboi* also discloses that Figure 13 includes pixels 53R, 53G, and 53B, having configurations that are the same as the pixels of Figures 1A/1B. Kuboi, ¶[181]. Similarly, Kuboi describes Figure 15 as applicable to all of *Kuboi*'s embodiments. *Kuboi*, ¶¶[35], [48]. Further, Kuboi's Figures 4A-4F show a method of manufacturing the basic pixel configuration of Figures 1A/1B. *Kuboi*, ¶¶[69]-[76]. Thus, Figures 1A/1B, 6A/6B, 13, and 15 all disclose the pixel configuration of the same imaging device, and Figures 4A-4F disclose methods of manufacturing that same pixel configuration. Lebby, ¶79. Accordingly, this Petition relies on *Kuboi*'s Figures

1A/1B, 4A-4F, 6A/6B, 13, and 15, and associated disclosures as representative of the pixel configuration of the same imaging device 201. Lebby, ¶79.

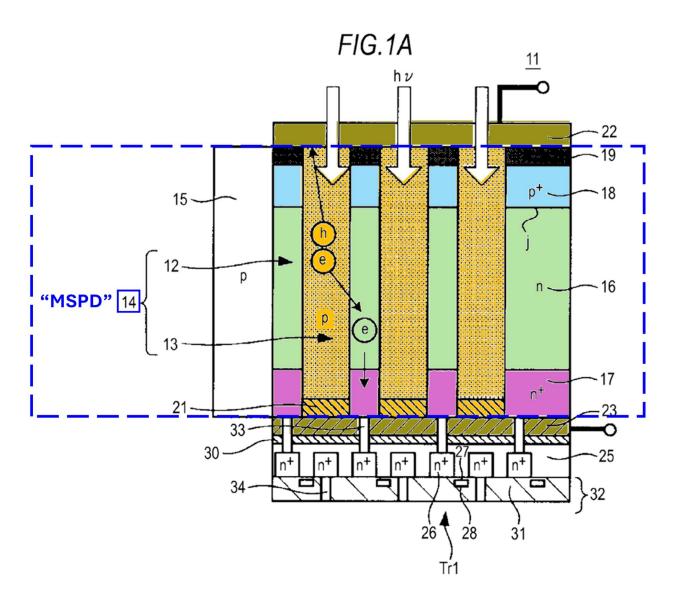

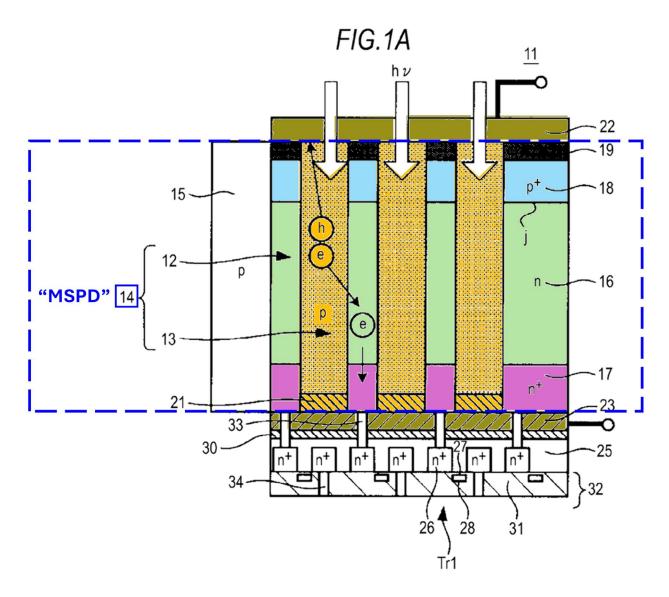

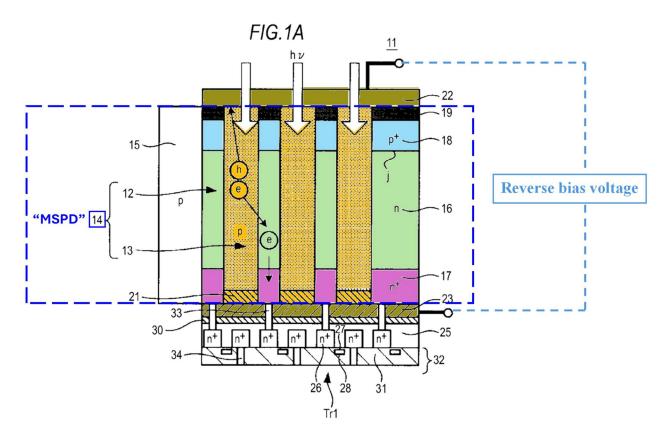

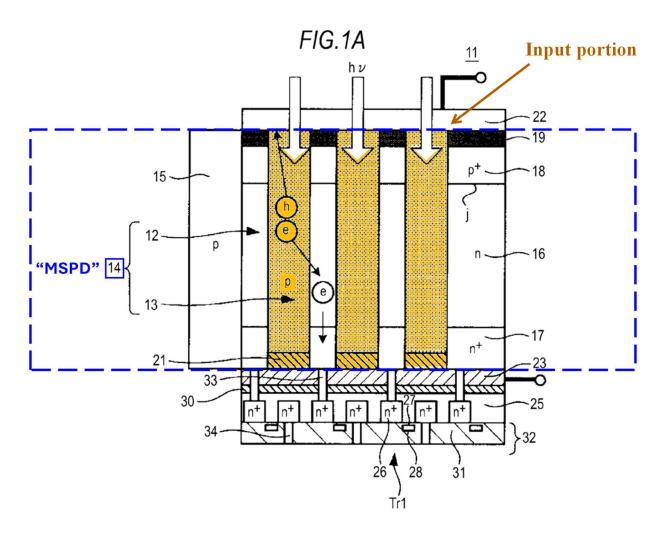

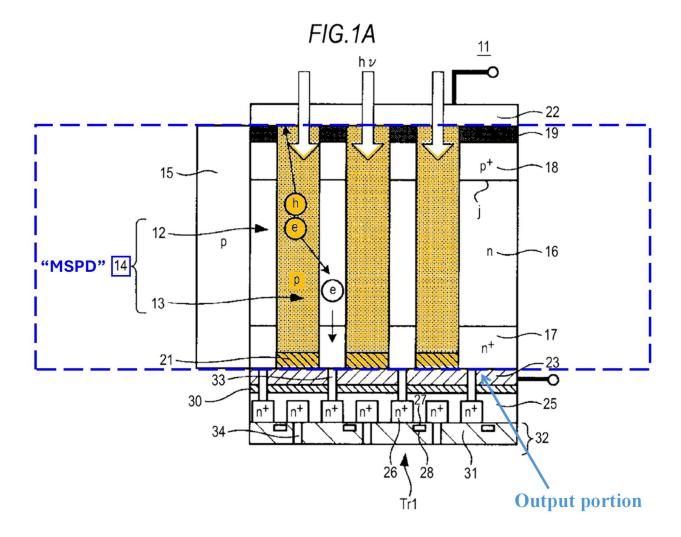

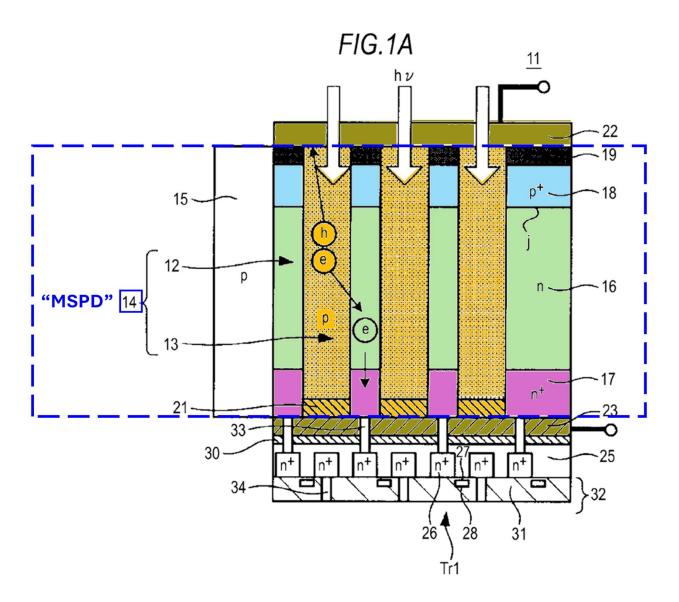

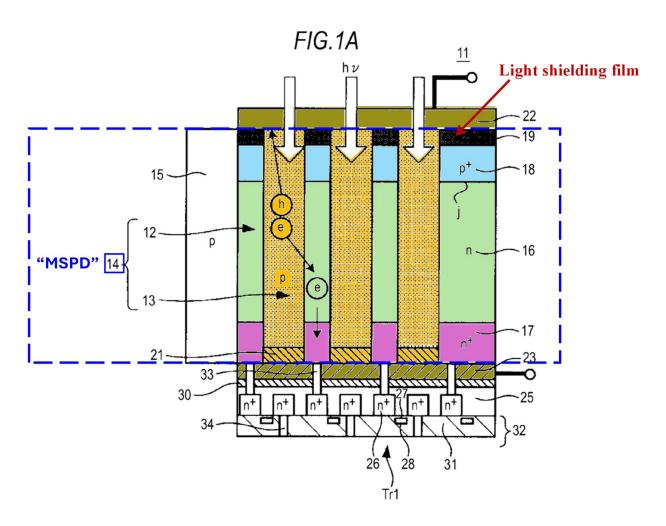

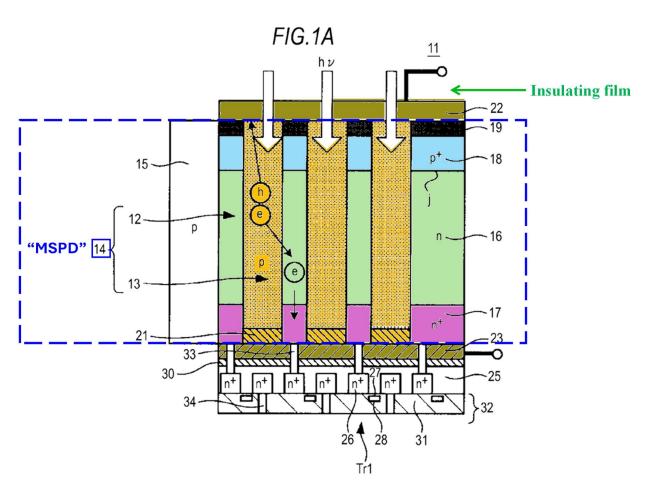

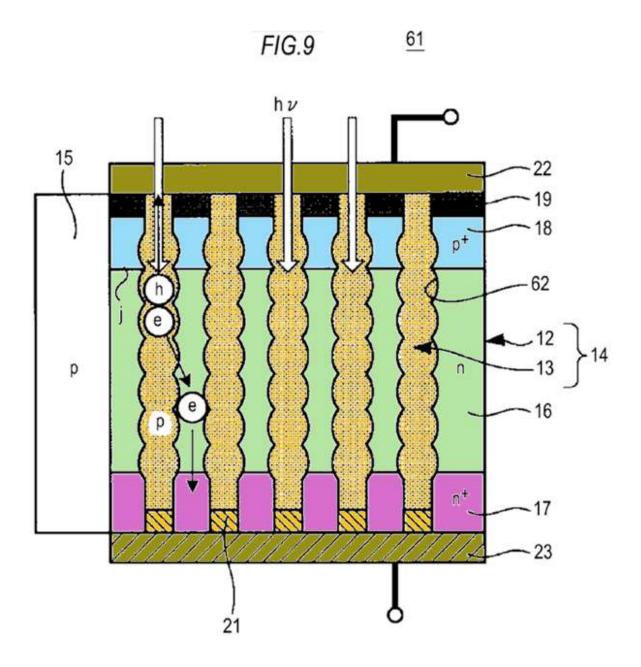

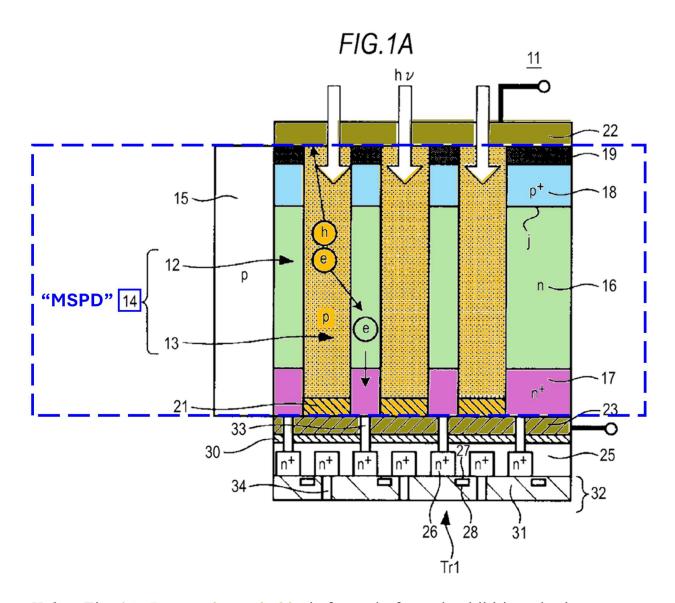

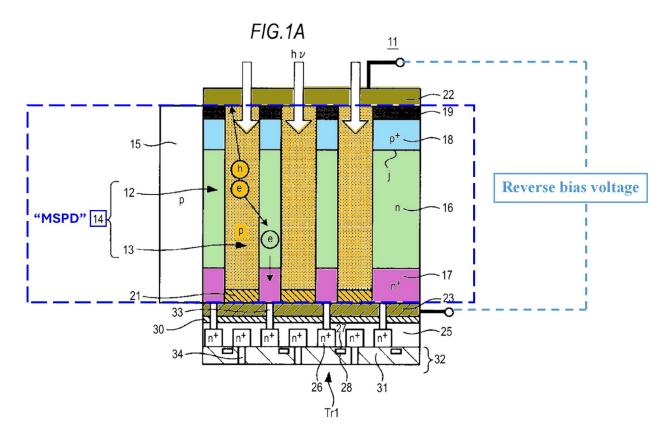

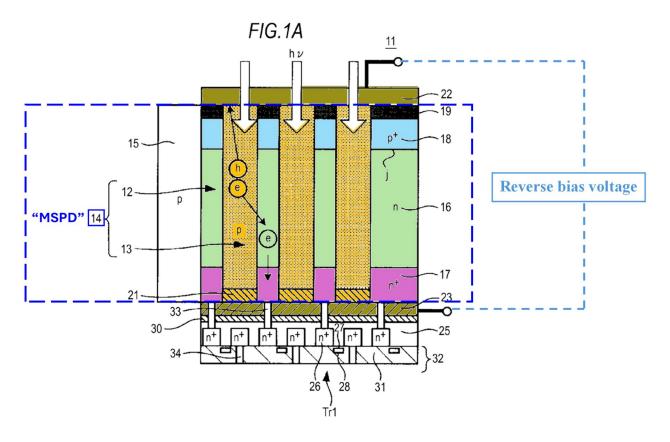

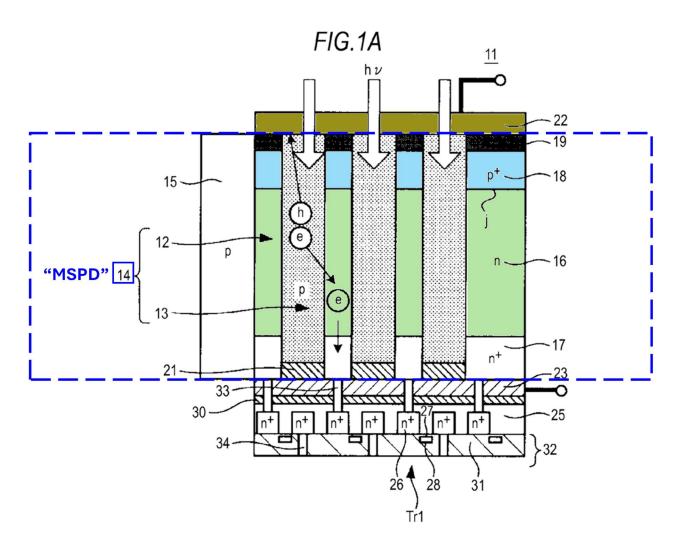

Figure 1A (below) illustrates a photoelectric conversion portion 14 in a pixel 11 that may be used in imaging device 201. *Kuboi*, ¶¶[48], [55]-[56]. *Kuboi* explains that pixel 11, including photoelectric conversion portion 14, can be utilized in imaging device 201. *Kuboi*, ¶¶[48], [55]; Lebby, ¶80.

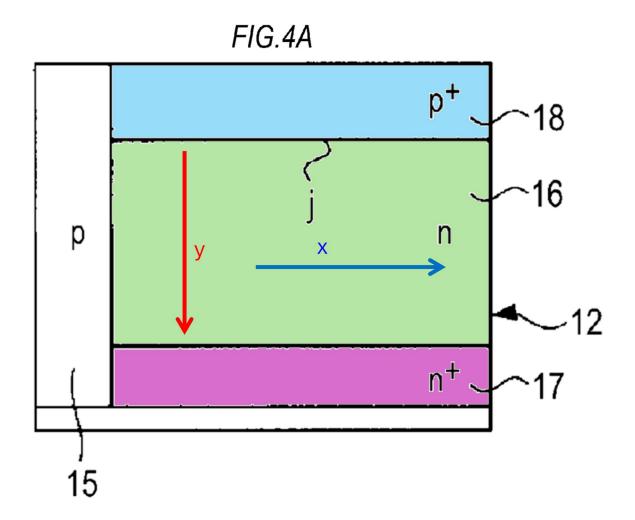

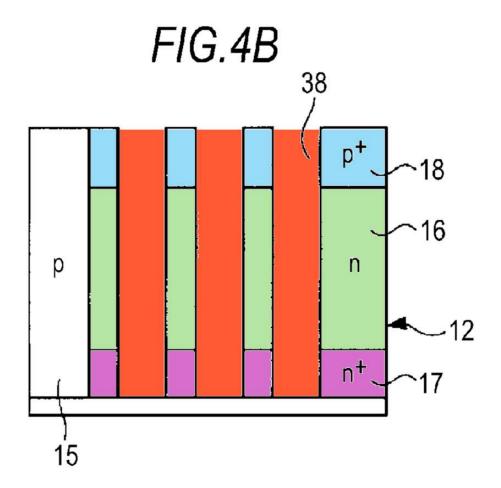

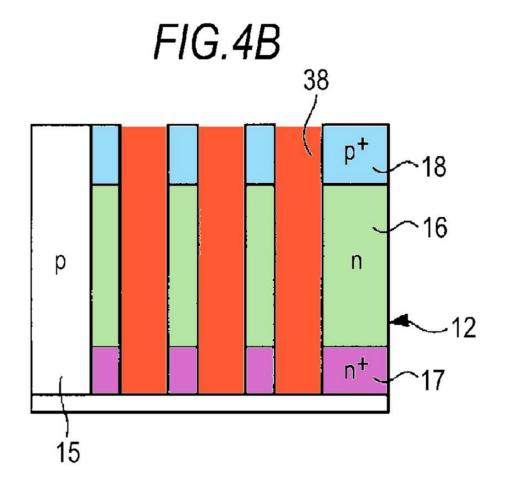

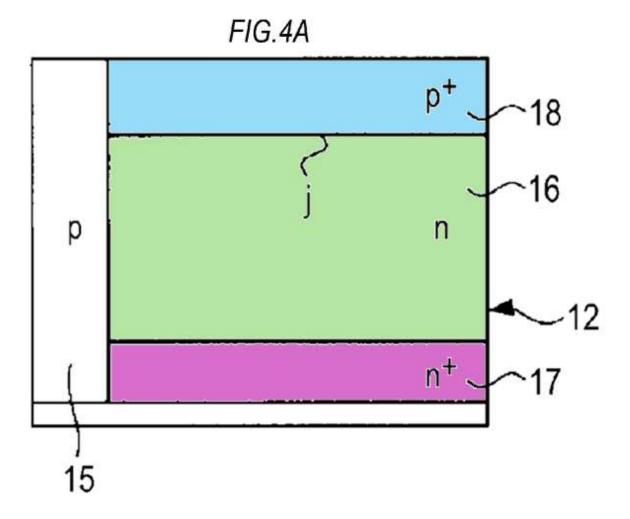

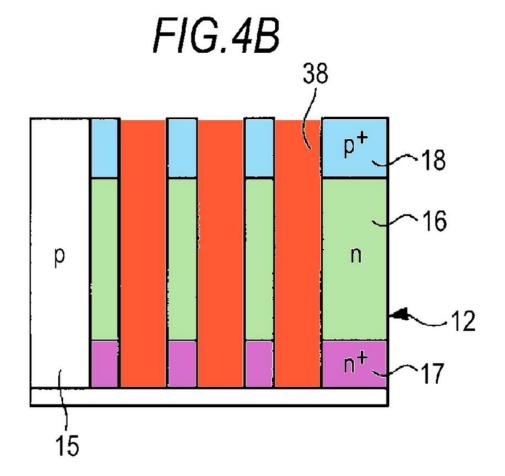

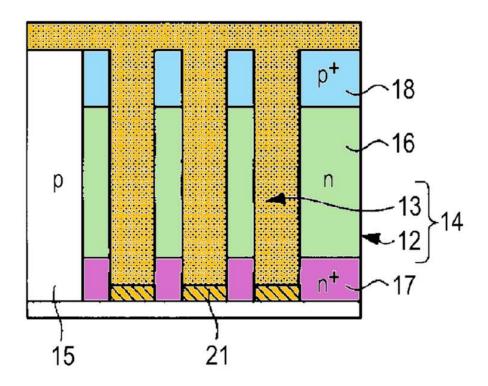

*Kuboi*, Fig. 1A. Photoelectric conversion portion 14 comprises a silicon semiconductor layer 12 that includes multiple embedded organic material layers 13. *Kuboi*, ¶[55]; Lebby, ¶81. Silicon semiconductor layer 12 is implanted with different impurities (or doped) to form an n-type semiconductor (or "intermediate") region 16 with a p<sup>+</sup>-type semiconductor region 18 on one side and

an n<sup>+</sup>-type semiconductor region 17 on the opposite side (i.e., stacked PiN regions). *Kuboi*, ¶¶[56], [71]; Lebby, ¶81. The doping of layer 12 is such that p<sup>+</sup>-type region 18 and n<sup>+</sup>-type region 17 have a higher concentration of impurities than n-type region 16. *Kuboi*, ¶[56].

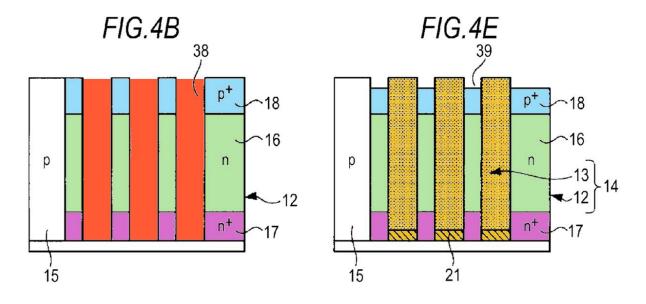

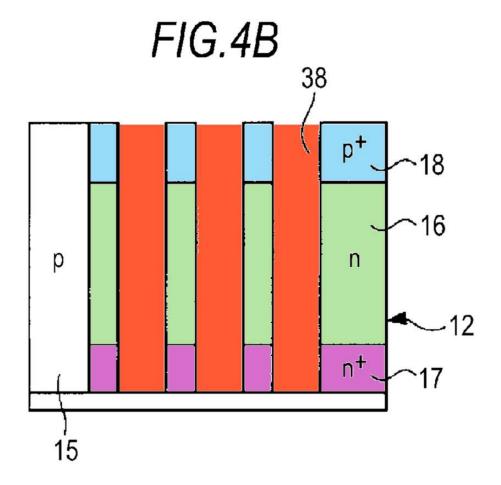

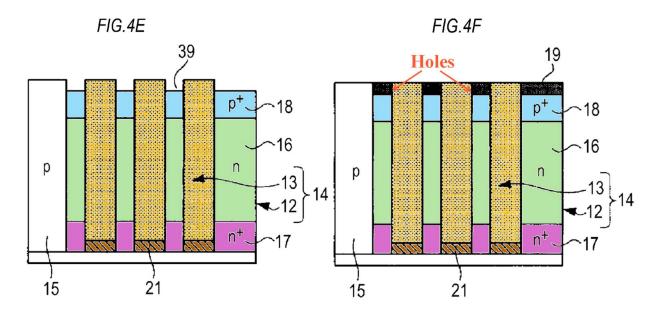

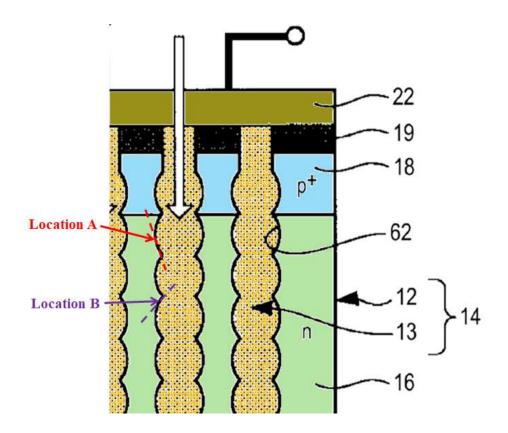

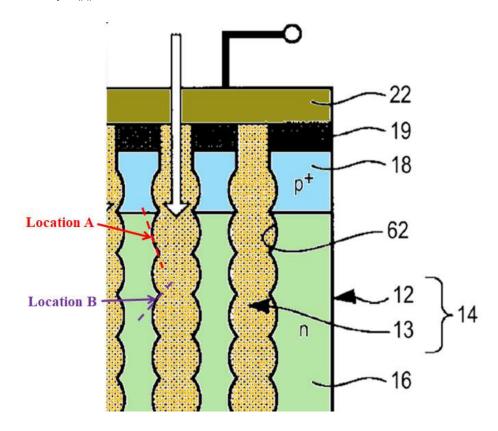

After forming regions 18, 16, and 17, vertical holes 38 extending from p<sup>+</sup>-type region 18 to n<sup>+</sup>-type region 17 are etched into the PiN regions (below left). *Kuboi*, ¶¶[71]-[72]; Lebby, ¶¶82-83.

*Kuboi*, Figs. 4B, 4E. Then, the organic material that forms photoelectric conversion film 13 is deposited in these holes 38 (above right). *Kuboi*, ¶¶[72]-[73].

A metal light shielding film 19 is then applied to the surface of p<sup>+</sup>-type region 18 such that only holes 38 containing films 13 are exposed to incident light (hv). *Kuboi*, ¶¶[59], [76], Figs. 1A, 4F; Lebby, ¶84. An upper electrode 22 and a lower electrode 23 are formed on opposite sides of the PiN regions, and a reverse

bias is applied. *Kuboi*, ¶¶[60], [64]. Photoelectric conversion of the incident light (hv) within films 13 (inside holes 38) generates electron-hole pairs that pass through the depleted semiconductor layer 12 into a charge accumulation region 26 of the transfer transistor (Tr1) of the corresponding pixel 11 (via conductors 33). *Kuboi*, ¶¶[62], [64]; Lebby, ¶84. After initial signal processing (e.g., amplification) by the pixel transistors, the electrical signals from pixel 11 are sent to the peripheral circuits for further processing. *Kuboi*, ¶¶[48]-[49], [61]-[62].

## 2. Independent Claim 1

a. [1pre(a)]: "A single-chip device comprising an integrated combination of a microstructure-enhanced photodetector (MSPD) configured for reverse-bias operation and an active electronic circuit,"

To the extent the preamble is limiting, *Kuboi* discloses this portion of it because its CMOS solid-state imaging device ("single-chip device") is a single chip that includes multiple pixels, with hybrid microstructure-enhanced photoelectric conversion portions ("MSPD") configured for reverse-bias operation, integrated with an active electronic circuit on a single semiconductor substrate 211. *Kuboi*, ¶¶[48], [64], Fig. 15; Lebby, ¶91.

*Kuboi* discloses the claimed "single-chip device" and "microstructure-enhanced photodetector (MSPD)." Lebby, ¶92. Imaging device 201 "include[s] a pixel region (so-called an imaging region) 203 and a peripheral circuit portion

which are provided on a semiconductor substrate 211 (e.g., a silicon substrate)." Kuboi, ¶[48]; Lebby, ¶92. This "single-chip device" is shown below:

*Kuboi*, Fig. 15. Pixel portion 203 includes a plurality of pixels 202 (elsewhere designated "pixel 11"), each of which includes a microstructure-enhanced

photodetector in the form of photoelectric conversion portion 14 ("MSPD"), regularly arranged in a two-dimensional array. *Kuboi*, ¶¶[48], [55]; Lebby, ¶93.

Figure 1A, reproduced below, illustrates exemplary pixel 11, including photoelectric conversion portion 14, that may be used in imaging device 201. *Kuboi*, ¶¶[48], [55]; Lebby, ¶94.

*Kuboi*, Fig. 1A. Photoelectric conversion portion 14 comprises a semiconductor layer 12 made of silicon and doped with different concentrations of impurities to form a p<sup>+</sup>-type region 18 and an n<sup>+</sup>-type region 17 on opposite sides of an n-type region 16 creating a PiN photodiode. *Kuboi*, ¶¶[55]-[56], [71], Fig. 4A; Lebby, ¶95.

Etching vertical holes 38 and embedding photoelectric conversion films 13 in photoelectric conversion portion 14 enhances the microstructure and improves light absorption of the pixel's photoelectric conversion portion. Lebby, ¶96; *Kuboi*, ¶¶[72], [80]-[84], [107]-[108]. Vertical holes 38 extending from p<sup>+</sup>-type region 18 to n<sup>+</sup>-type region 17 are dry-etched into semiconductor layer 12, and organic photoelectric conversion films 13 are embedded in holes 38. *Kuboi*, ¶¶[57]-[58], [71]-[75], Figs. 4A-4E. A metal light shielding film 19 is arranged on the surface of p<sup>+</sup>-type region 18 such that only the embedded photoelectric conversion films 13 are exposed to incident light (hv). *Kuboi*, ¶¶[57]-[59], [72]-[76]; Lebby, ¶96. Incident light enters photoelectric conversion films 13 and undergoes photoelectric conversion to generate electric charges corresponding to the amount of light received. *Kuboi*, ¶¶[51], [64]. *Kuboi* notes that embedding photoelectric conversion films 13 in holes in the PiN regions increases light absorption compared to photoelectric conversion portions without embedded films 13. Kuboi, ¶¶[12], [71]-[75], [80]-[82], [107].

Photoelectric conversion portion 14 is configured for "reverse-bias operation," as claimed. *Kuboi*, ¶¶[64], [87], [149], [171], [186], Fig. 1A; Lebby, ¶¶97-99. As shown below, an upper electrode 22 formed on top of metal film 19 of photoelectric conversion portion 14 makes electrical contact with p+-type region 18, and a lower electrode 23 is coupled to—and makes electrical contact with—the surface of n+-type region 17. *Kuboi*, ¶¶[59]-[60], [77], Fig. 1A. Lebby, ¶97.

*Kuboi*, Fig. 1A. A voltage bias is applied between these electrodes, causing upper electrode 22 to have a negative potential and lower electrode 23 to have a positive potential. *Kuboi*, ¶¶[64], [87]. This creates a depletion layer in semiconductor layer 12. *Kuboi*, ¶¶[64], [87]. A POSITA would have understood that applying a

voltage bias with a negative potential to p<sup>+</sup>-type region 18 and a positive potential to n<sup>+</sup>-type region 17 constitutes a reverse bias. Lebby, ¶¶98-99; *see also* Ex-1031, 3-5, 8 (explaining that reverse bias is "[t]he condition in which a positive voltage is applied to the n region with respect to the p region of a pn junction"); Ex-1032, 3-4.

Kuboi also discloses the claimed "active electronic circuit," which is integrated with photoelectric conversion portion 14. Lebby, ¶¶100-102. Imaging device 201 includes a peripheral circuit portion with "logical circuits" (logic circuits). Kuboi, ¶¶[48]-[49], [78], Fig. 15; Lebby, ¶100. The "logic[] circuits" of the peripheral circuit portion include a vertical driving circuit 204, multiple column signal processing circuits 205, a horizontal driving circuit 206, an output circuit 207, and a control circuit 208. Kuboi, ¶[49]; Lebby, ¶100. Each can be seen below.

*Kuboi*, Fig. 15. Vertical driving circuit 204 supplies pulses for activating the pixels in a selected row and channels pixel signals from each pixel to a corresponding column signal processing circuit 205, which performs signal processing tasks such as, e.g., signal amplification. *Kuboi*, ¶¶[51]-[52]. Horizontal driving circuit 206 sequentially selects a column signal processing circuit 205 and routes the

processed pixel signals from that circuit 205 to output circuit 207, which further processes the received signals and outputs the processed signals. *Kuboi*, ¶¶[53]-[54]. Meanwhile, control circuit 208 controls the other circuits of the peripheral circuit portion. *Kuboi*, ¶[50].

Each of these CMOS "logic[] circuits" of the peripheral circuit portion includes active components such as transistors, which activate circuits and amplify signals, thereby making them an active electronic circuit. Lebby, ¶¶101-102; Kuboi, ¶[49]; Ex-1019, 4 ("Complementary MOS (CMOS) refers to a complementary p-channel and n-channel MOSFET pair."); Ex-1017, 6 (describing amplifiers and logic circuits as "active circuits"), 7, 9 (describing transistors as the most important example of an "active' component[]"), 8 (describing circuits with transistors as "active circuits"); Ex-1019, 4 (describing logic circuits as including transistors); Ex-1018, 4, 5; see Ex-1026, 4. Thus, the logic circuits (vertical driving circuit 204, a column signal processing circuit 205, horizontal driving circuit 206, output circuit 207, and control circuit 208) of *Kuboi*'s peripheral circuit portion that process the signals from a pixel (pixel 11) and output it are the claimed active electronic circuit. Lebby, ¶102. The active electronic circuit is highlighted in the figure of imaging device 201 below.

Kuboi, Fig. 15 (identifying an active electronic circuit).

# b. [1pre(b)]: "both formed on or in a single substrate"

To the extent the preamble is limiting, *Kuboi* discloses this portion of it because imaging device 201's photoelectric conversion portions 14 and active electronic circuit are both formed on or in a single substrate. Lebby, ¶¶103-105.

In imaging device 201, pixels 11 (including photoelectric conversion portions 14) and the peripheral circuit portion (which includes an active electronic circuit) "are provided on ... semiconductor substrate 211." *Kuboi*, ¶¶[48], [78]-[79]; *see Kuboi*, Fig. 15; Lebby, ¶104. As shown below, the pixel region (including pixels 11) and the peripheral circuit portion (including circuits 204-208) "are provided on a semiconductor substrate 211." *Kuboi*, ¶¶[48]-[49].

*Kuboi*, Fig. 15. Indeed, consistent with the above figure's disclosure of a single substrate, *Kuboi* specifically outlines a method for fabricating the imaging device in which the "pixel and logical circuit portion ... [are] created in advance" and bonded to another substrate on which the pixel transistors are formed. *Kuboi*, ¶[78]; Lebby, ¶105. As Dr. Lebby explains, *Kuboi*'s disclosure, including

Figure 15 and its method of fabrication, shows that the pixels (including microstructure-enhanced photodetectors) and the peripheral circuit portion (which includes the active electronic circuit, VI.A.2.a ([1pre(a)]) are formed on a single substrate, substrate 211.4 Lebby, ¶105.

c. [1pre(c)]: "and configured to receive an optical input that in cross-section is substantially continuous spatially, convert the optical input to an electrical output, and process the electrical output into a processed output, wherein:"

To the extent the preamble is limiting, *Kuboi* discloses and renders obvious this portion of it because imaging device 201 and pixels 11 are configured to receive light (h $\gamma$ ) (the "optical input") that is substantially continuous in crosssection spatially, convert the received light to electrical charges, and process these electrical charges into a processed output. Lebby, ¶¶106-114.

Pixel 11 includes an on-chip microlens (not shown in the drawings) formed on transparent upper electrode 22. *Kuboi*, ¶¶[63]-[64]. A color filter is disposed between upper electrode 22 and the on-chip microlens. *Kuboi*, ¶¶[63], [90],

<sup>&</sup>lt;sup>4</sup> A drawing teaches all that it reasonably discloses and suggests to a POSITA. *In re Aslanian*, 590 F.2d 911, 914 (CCPA 1979); *see also Current Lighting Sols. LLC v. Jiaxing Super Lighting Elec. Appliance Co.*, IPR2023-00269, Paper 18, 22-26 (PTAB Aug. 16, 2023).

Figs. 6A-6B. As illustrated below, light that passes through the on-chip microlens and the color filter passes through transparent upper electrode 22 and enters photoelectric conversion film 13 of photoelectric conversion portion 14 for photoelectric conversion. *Kuboi*, ¶¶[63]-[64], Fig. 1A; Lebby, ¶107.

Kuboi, Fig. 1A.

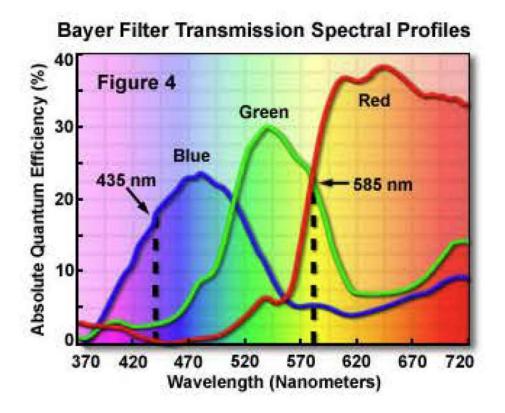

The light that passes through upper electrode 22 after passing through a color filter will have the same color (or wavelength) as the color filter. Kuboi, ¶¶[63]-[64], [90], Figs. 6A-6B; Lebby, ¶108. For instance, if a red filter is used, the wavelength of incident light will be about 650 nm; if a green filter is used, the wavelength will be about 540 nm, and so on. Lebby, ¶108; see Kuboi, ¶¶[6], [90]. Thus, the wavelength of light received by photoelectric conversion portion 14 is "substantially continuous spatially" in cross-section, as claimed. Lebby, ¶108; see Kuboi, Fig. 1A. Moreover, based on the structure of pixel 11, a POSITA would have understood that light is uniformly received spatially across the surface of photoelectric conversion portion 14 beneath upper electrode 22, rather than being limited to specific locations. Lebby, ¶108. Furthermore, based at least on the size of the arrows that illustrate incident light on the pixels, a POSITA would have recognized that the magnitude of the light received by photoelectric conversion portions 14 is substantially continuous spatially in cross-section. Lebby, ¶108; see *Kuboi*, Figs. 1A, 3, 5A, 6A, 8A, 9, 10A, 13.

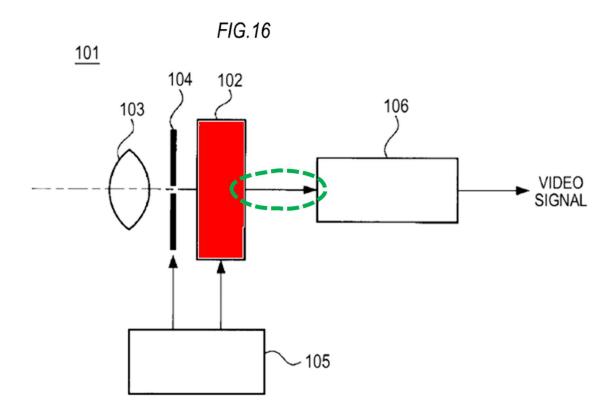

To the extent that *Kuboi* does not expressly disclose that light received by pixel 11 is substantially continuous in cross-section, this would have been obvious to a POSITA based on *Kuboi*. Lebby, ¶109. Imaging device 201 may be used in an imaging apparatus where light reflected from an object is guided to the pixels (including pixel 11) to capture an image of the object. *Kuboi*, ¶¶[191]-[192],

Fig. 16; Lebby, ¶109. A POSITA would have understood that each pixel receiving light that is substantially uniform in cross-section would assist in preserving the integrity of color reproduction and would enable the image sensor to produce sharper and more vivid images with reduced distortions. Lebby, ¶109; Ex-1015, 4-6 (discussing the impact of color variations and illumination levels on the pixels of an image sensor on the resulting image). A POSITA would thus have been motivated to configure imaging device 201 such that the light received by pixel 11 is substantially uniform in cross-section, ensuring that the images produced by imaging device 201 are sharp and vivid. Lebby, ¶110. Given that this is a well-understood image sensor feature, the results would have been entirely predictable and a POSITA would have had a reasonable expectation of success in carrying out this modification. Lebby, ¶110.

Photoelectric conversion portion 14 converts the received light into electrical charges ("convert the optical input to an electrical output") and outputs it.

Lebby, ¶¶111-112. As illustrated below, light that enters photoelectric conversion films 13 undergoes photoelectric conversion and generates electron-hole pairs.

Kuboi, ¶[64].

*Kuboi*, Fig. 1A. The highlighted arrows above show how the separated electrons (e), which serve as signal charges, move from photoelectric conversion films 13 through the interface and semiconductor layer 12, and are output from photoelectric conversion portion 14 to a charge accumulation region 26 of the pixel transistors via conductors 33. *Kuboi*, ¶¶[61], [62], [64], Fig. 1A; Lebby, ¶112.

Meanwhile, the holes (h) are discharged through upper electrode 22. *Kuboi*, ¶[64]. The signal charges that are generated based on the amount of light received by photoelectric conversion portion 14 are pixel 11's electrical output. *Kuboi*, ¶¶[51], [62]-[64]; Lebby, ¶112.

The peripheral circuit portion's logic circuits (that include circuits 204-208) process pixel 11's electrical output into a processed output. Lebby, ¶113-114. As indicated by the annotated red line below, vertical driving circuit 204 transfers the accumulated electrical output (via signal line 209) to the corresponding column signal processing circuit 205. *Kuboi*, ¶¶[51]-[52].

*Kuboi*, Fig. 15. This circuit performs signal processing tasks such as signal amplification and then outputs the amplified signals (via signal line 210) to output circuit 207, which conducts further signal processing and outputs the processed signals. *Kuboi*, ¶¶[52]-[54]; VI.A.2.m ([1j]), VI.A.2.n ([1k]); Lebby, ¶114.

d. [1a]: "the MSPD on or in said single substrate comprises an intermediate region, a first region at one side of the intermediate region, and a second region at an opposite side of the intermediate region, wherein:"

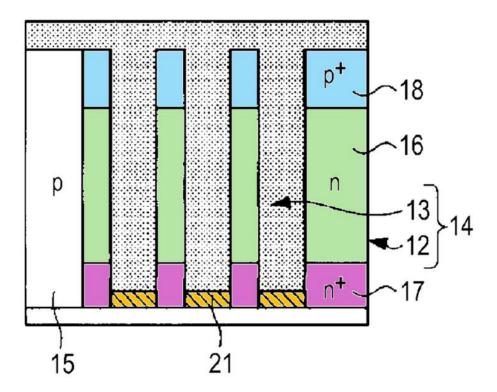

*Kuboi* discloses this limitation because semiconductor layer 12 of photoelectric conversion portion 14 ("MSPD") comprises an n-type region 16 ("intermediate region"), a p<sup>+</sup>-type region 18 ("first region") on one side of n-type region 16, and n<sup>+</sup>-type region 17 ("second region") on the opposite side of n-type region 16. *Kuboi*, ¶¶[55]-[56], [71], Figs. 3, 4A; Lebby, ¶¶115-117. These regions are illustrated below:

*Kuboi*, Fig. 4A. Silicon semiconductor layer 12 is implanted with impurities to form an "n<sup>+</sup>-type semiconductor region 17 (corresponding to the front surface side), a n-type semiconductor region 16 (corresponding to an intermediate region), and a p<sup>+</sup>-type semiconductor region [18] (corresponding to the rear surface side) ... in that order from the lower region of the drawing [of Figure 4A] in a region corresponding to one pixel." *Kuboi*, ¶¶[55]-[56], [71]; Lebby, ¶116.

As discussed for [1pre(b)], photoelectric conversion portion 14 ("MSPD") (including semiconductor layer 12 and the regions discussed above) is formed on substrate 211 (the "single substrate"). VI.A.2.b; Lebby, ¶117.

e. [1b]: "each of the regions comprises Silicon, Germanium, or an alloy thereof;"

Kuboi discloses this limitation because n\*-type semiconductor region 17 ("second region"), n-type semiconductor region 16 ("intermediate region"), and p\*-type semiconductor region 18 ("first region") are each formed by implanting "semiconductor layer 12 formed of silicon" with impurities. Lebby, ¶118; Kuboi, ¶¶[55]-[56], [71]. Since these regions are created by implanting impurities into silicon, each region will comprise silicon. Lebby, ¶118; Kuboi, ¶[3] ("an impurity-implanted crystalline silicon layer"); see also Kuboi, ¶¶[6], [66], [110]-[111].

f. [1c]: "at least one of said regions, and an optional overlying covering region, have holes intentionally formed therein"

*Kuboi* discloses this limitation because multiple vertical holes 38 ("holes intentionally formed") are dry-etched through the three regions of pixel 11's semiconductor layer 12: n<sup>+</sup>-type region 17, n-type region 16, and p<sup>+</sup>-type region 18. Lebby, ¶¶119-128; *Kuboi*, ¶¶[71]-[72], Fig. 4B. These holes 38 are illustrated below:

*Kuboi*, Fig. 4B. After regions 16, 17, and 18 are formed on semiconductor layer 12, "vertical hole[s] 38" "extending from the p<sup>+</sup>-type ... region 18 to the n<sup>+</sup>-type ... region [17] [are] formed in a region of the semiconductor layer 12 corresponding to one pixel by dry-etching." *Kuboi*, ¶¶[71]-[72]; Lebby, ¶120. These holes can be cylindrically shaped or may extend into the page to form a stripe shape in a plan view. *Kuboi*, ¶[57], Fig. 1B.

A light shielding film 19 ("overlying covering region"), which is formed on (and overlies) the light incident surface of p<sup>+</sup>-type region 18, also contains holes that align with the holes in the underlying PiN regions. *Kuboi*, ¶¶[76], [91], Fig. 1A; Lebby, ¶121.

*Kuboi*, Figs. 4E, 4F. After depositing photoelectric conversion films 13 into holes 38 formed through regions 16, 17, and 18, the surfaces of films 13 are

covered using a resist mask (not shown). *Kuboi*, ¶¶[73]-[75]. The exposed surface of p<sup>+</sup>-type region 18 is then etched back, causing the embedded films 13 to protrude from the surface of p<sup>+</sup>-type region 18. *Kuboi*, ¶[75], Fig. 4E. Then, a light shielding film 19 is applied on the etched surface of p<sup>+</sup>-type region 18 around protruding films 13 so that incident light only enters exposed films 13 (and not p<sup>+</sup>-type region 18). *Kuboi*, ¶¶[59], [76]. Applying light shielding film 19 around protruding films 13 results in holes being formed in light shielding film 19 around films 13. Lebby, ¶122.

*Kuboi* discloses that vertical holes 38 extending through the PiN regions may be dry-etched "using a CCP (Capacitive Coupled Plasma) etching apparatus" or other apparatuses. *Kuboi*, ¶¶[72], [95]. Therefore, a POSITA would have understood that these holes 38 are intentionally created. Lebby, ¶123. Since the holes in the overlying light shielding film 19 are formed by etching back p<sup>+</sup>-type region 18 around films 13 and forming light shielding film 19 around the protruding films 13, holes in light shielding film 19 are also intentionally created. *Kuboi*, ¶¶[72], [75]-[76]; Lebby, ¶123.

The adjective "optional" in the term "overlying covering layer" was introduced during prosecution to clarify that the overlying covering layer is not a mandatory feature and may or may not be included. Lebby, ¶124; Ex-1044, 124-25, 136. Originally, the claim stated: "overlying covering region that may be

present," resembling the language used in its direct predecessor, U.S. Patent No. 10,446,700 ("'700 Patent") (Ex-1001). Ex-1044, 632; '700 Patent, 118:39-40; Lebby, ¶¶69-72, 124. During prosecution of the '700 Patent, the Examiner clarified that the phrase "overlying covering region that may be present" does not mandate the presence of the overlying layer but instead "merely states the overlying layer as an optional component." Ex-1003, 387. Later, during prosecution of the '543 Patent, the same Examiner recommended modifying this language to explicitly state "optional overlying covering region" to address potential §112 enablement concerns with the original phrasing. Ex-1044, 124-125. Accordingly, based on the Examiner's suggestion, "overlying covering region that may be present" was amended to "optional overlying covering region." Ex-1044, 136 (emphasis added); Lebby, ¶124. Indeed, the '543 Patent employs the term "optional" to denote nonmandatory features that might or might not be present on the device. See, e.g., '543 Patent, 41:16-19, 41:59-61, 42:47-55, 44:14-22, 75:30-32; Lebby, ¶125.

Case law further supports this interpretation, since "[a]s a matter of linguistic precision, optional elements do not narrow the claim because they can always be omitted." *In re Johnston*, 435 F.3d 1381, 1384 (Fed. Cir. 2006); *see also Ericsson Inc. v. Intell. Ventures II LLC*, IPR2014-01412, Paper 8, 8-10 (PTAB Mar. 18, 2015) ("optional[]" elements in claims are not compulsory); *Butamax Advanced Biofuels LLC v. Gevo, Inc.*, IPR2014-00250, Paper 29, 6-7 (PTAB

Mar. 13, 2015). Consequently, an "overlying covering region" is not required to satisfy this claim limitation. Despite this, *Kuboi* satisfies this limitation, as its light shielding film 19 qualifies as an overlying covering region with deliberately created holes for the reasons discussed above. Lebby, ¶125.

Indeed, a POSITA would have understood that photoelectric conversion portion 14 ("MSPD") generates electrons (charge) through photoelectric conversion of light regardless of whether light shielding film 19 is present, so light shielding film 19 is optional in the same way that the overlying covering layer is optional in the '543 Patent. Lebby, ¶126-128. When light shielding film 19 covers the surface of semiconductor layer 12, light exclusively enters photoelectric conversion film 13, and, as a result, photoelectric conversion occurs solely within film 13. See Kuboi, ¶¶[59], [64]. A POSITA would understand that, in the absence of light shielding film 19, light would enter both film 13 and semiconductor layer 12, leading to photoelectric conversion occurring in layer 12 and film 13. Lebby,  $\P127-128$ ; see Kuboi,  $\P1[6]$ , [91]-[92], [94]; Ex-1045, 1-7. Consequently, light shielding film 19 is not essential to the operation of MSPD 14 as it remains functional even in its absence, albeit with a modified performance. Lebby, ¶128.

## g. [1d]: "each of the first and second regions comprises a doped material;"

*Kuboi* discloses this limitation because p<sup>+</sup>-type region 18 ("first region") and n<sup>+</sup>-type region 17 ("second region") of semiconductor layer 12 are formed by "implant[ing] ... impurities" in silicon semiconductor layer 12. *Kuboi*, ¶¶[55]-[56]; Lebby, ¶¶129-130.

According to *Kuboi*, "semiconductor layer 12 [formed of silicon] is implanted with impurities ... [to form] a[n] n<sup>+</sup>-type ... region 17 having higher concentration [of impurities] than the n-type ... region 16, and a semiconductor region 18 of second conductivity type (for example, p<sup>+</sup> type) having higher concentration [of impurities] than the n-type ... region 16." Kuboi, ¶¶[55]-[56]; see also Kuboi, ¶¶[7], [111], [151]. A POSITA would have understood that the process of implanting impurities into silicon material is known as "doping" the silicon material and the result is a "doped material," as claimed. Lebby, ¶130; Ex-1018, 3 (defining "doping" as "the process of introducing impurity atoms into pure silicon to change its electrical properties"); Ex-1019, 23 ("Impurity doping is the introduction of controlled amounts of impurity dopants into semiconductor materials."); Ex-1020, 4 ("A doped region is simply a section of the silicon into which impurity atoms have been purposely added to alter the electrical

properties."); *see* Ex-1026, 3. Therefore, *Kuboi*'s first and second regions comprise doped silicon. Lebby, ¶130.

h. [1e]: "the intermediate region comprises a material that is less doped than at least one of the first and second regions or is undoped, wherein the degree of doping is the same or different for different positions in the intermediate region;"

*Kuboi* discloses this limitation because its n-type region 16 ("intermediate region") comprises silicon that is less doped than both  $p^+$ -type region 18 ("first region") and  $n^+$ -type region 17 ("second region"). *Kuboi*, ¶[56]; Lebby, ¶131-138. And, in addition, the degree of doping is the same or different at different positions in n-type region 16. *Kuboi*, ¶[56]; Lebby, ¶131.

According to *Kuboi*, "semiconductor layer 12 [formed of silicon] is implanted with impurities ... [to form] a semiconductor region 16 of first conductivity type (for example, n type), a[n] n<sup>+</sup>-type semiconductor region 17 having higher concentration [of impurities] than the n-type semiconductor region 16, and a semiconductor region 18 of second conductivity type (for example, p<sup>+</sup> type) having higher concentration [of impurities] than the n-type semiconductor region 16." *Kuboi*, ¶¶[55]-[56]; *see also Kuboi*, ¶¶[7], [111], [151]. As explained for [1d], "the process of introducing impurity atoms into pure silicon" is doping the silicon material and results in a "doped material." Ex-1018, 3; Ex-1020, 4; VI.A.2.g. Thus, n-type region 16 comprises doped silicon with a concentration of

impurities (or degree of doping) less than that in  $p^+$ -type region 18 and  $n^+$ -type region 17. Lebby, ¶132.

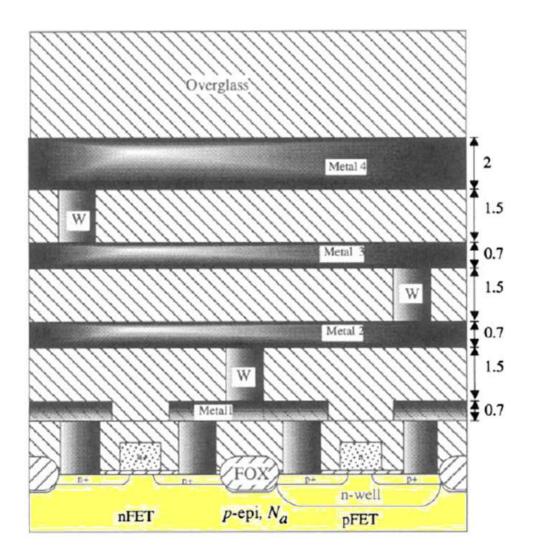

A POSITA would have understood that the degree of doping in n-type region 16 ("intermediate region") would either be the same or different at different positions, as no other possibilities exist. Lebby,  $\P133-138$ . *Kuboi* uses "ion implantation" for implanting impurities in semiconductor layer 12. *Kuboi*,  $\P\P[7]$ , [134]. After ion implantation, the dopant concentration varies with depth (x in the figure below) of the layer. Lebby,  $\P133-137$ ; Ex-1020, 4; Ex-1019, 23-24; Ex-1028, 1.

Fig. 1 Comparison of (a) diffusion and (b) ion-implantation techniques for selective introduction of dopants into the semiconductor substrate.

Ex-1019, 24 (Fig. 1 cropped). A POSITA would thus have recognized that the degree of doping in n-type region 16 ("intermediate region") will be different at different positions along the depth (along line y in the figure below) and the same for different positions along its width (along line x in the figure below). Lebby, ¶138.

*Kuboi*, Fig. 4A. Therefore, in *Kuboi*, "the degree of doping is the same or different for different positions in the intermediate layer," as claimed. Lebby, ¶138.

i. [1f]: "an input portion configured to concurrently receive at a plurality of said holes said optical input that has said substantially continuous cross-section; and"

*Kuboi* discloses and renders obvious this limitation because, as explained for **[1pre(c)]**, light ("optical input") that passes through transparent upper electrode 22 of pixel 11 is substantially continuous in cross-section (or this would have been

obvious), VI.A.2.c, and since light enters photoelectric conversion films 13 (extending through holes in semiconductor layer 12) through upper electrode 22, the holes are configured to concurrently receive light having substantially continuous cross-section. Lebby, ¶¶139-143.