SEVENTH EDITION

# Microelectronic Circuits

Adel S. Sedra

**University of Waterloo**

Kenneth C. Smith

**University of Toronto**

New York Oxford

OXFORD UNIVERSITY PRESS

Oxford University Press is a department of the University of Oxford. It furthers the University's objective of excellence in research, scholarship, and education by publishing worldwide.

Oxford New York

Auckland Cape Town Dar es Salaam Hong Kong Karachi Kuala Lumpur Madrid Melbourne Mexico City Nairobi New Delhi Shanghai Taipei Toronto

With offices in

Argentina Austria Brazil Chile Czech Republic France Greece Guatemala Hungary Italy Japan Poland Portugal Singapore South Korea Switzerland Thailand Turkey Ukraine Vietnam

Copyright © 2015, 2010, 2004, 1998 by Oxford University Press; 1991, 1987 Holt, Rinehart, and Winston, Inc.; 1982 CBS College Publishing

For titles covered by Section 112 of the US Higher Education Opportunity Act, please visit www.oup.com/us/he for the latest information about pricing and alternate formats.

Published in the United States of America by Oxford University Press 198 Madison Avenue, New York, NY 10016 http://www.oup.com

Oxford is a registered trade mark of Oxford University Press.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior permission of Oxford University Press.

#### Library of Congress Cataloging-in-Publication Data

Sedra, Adel S., author.

Microelectronic circuits / Adel S. Sedra, University of Waterloo, Kenneth C. Smith, University of Toronto. — Seventh edition.

pages cm. — (The Oxford series in electrical and computer engineering)

Includes bibliographical references and index.

ISBN 978-0-19-933913-6

1. Electronic circuits. 2. Integrated circuits. I. Smith,

Kenneth C. (Kenneth Carless), author. II. Title.

TK7867.S39 2014

621.3815—dc23

2014033965

Multisim and National Instruments are trademarks of National Instruments. The Sedra/Smith, *Microelectronic Circuits*, Seventh Edition book is a product of Oxford University Press, not National Instruments Corporation or any of its affiliated companies, and Oxford University Press is solely responsible for the Sedra/Smith book and its content. Neither Oxford University Press, the Sedra/Smith book, nor any of the books and other goods and services offered by Oxford University Press are official publications of National Instruments Corporation or any of its affiliated companies, and they are not affiliated with, endorsed by, or sponsored by National Instruments Corporation or any of its affiliated companies.

OrCad and PSpice are trademarks of Cadence Design Systems, Inc. The Sedra/Smith, *Microelectronic Circuits*, Seventh Edition book is a product of Oxford University Press, not Cadence Design Systems, Inc., or any of its affiliated companies, and Oxford University Press is solely responsible for the Sedra/Smith book and its content. Neither Oxford University Press, the Sedra/Smith book, nor any of the books and other goods and services offered by Oxford University Press are official publications of Cadence Design Systems, Inc. or any of its affiliated companies, and they are not affiliated with, endorsed by, or sponsored by Cadence Design Systems, Inc. or any of its affiliated companies.

Cover Photo: This 3D IC system demonstrates the concept of wireless power delivery and communication through multiple layers of CMOS chips. The communication circuits were demonstrated in an IBM 45 nm SOI CMOS process. This technology is designed to serve a multi-Gb/s interconnect between cores spread across several IC layers for high-performance processors.

(Photo Credit: The picture is courtesy of Professor David Wentzloff, Director of the Wireless Integrated Circuits Group at the University of Michigan, and was edited by Muhammad Faisal, Founder of Movellus Circuits Incorporated.)

Printing number: 987654321

Printed in the United States of America on acid-free paper

#### **EXERCISES**

3.7 Show that

$$V_0 = \frac{1}{2} \left( \frac{q}{\epsilon_s} \right) \left( \frac{N_A N_D}{N_A + N_D} \right) W^2$$

**3.8** Show that for a pn junction in which the p side is much more heavily doped than the n side (i.e.,  $N_A \gg N_D$ ), referred to as a  $p^+n$  diode, Eqs. (3.26), (3.27), (3.28), (3.29), and (3.30) can be simplified as follows:

$$W \simeq \sqrt{\frac{2\epsilon_s}{qN_D}V_0} \tag{3.26'}$$

$$x_n \cong W \tag{3.27'}$$

$$x_p \simeq W/(N_A/N_D) \tag{3.28'}$$

$$Q_{I} \simeq AqN_{D}W \tag{3.29'}$$

$$Q_{I} \simeq A\sqrt{2\epsilon_{s}qN_{D}V_{0}} \tag{3.30'}$$

3.9 If in the fabrication of the pn junction in Example 3.5, it is required to increase the minority-carrier concentration in the *n* region by a factor of 2, what must be done? **Ans.** Lower  $N_D$  by a factor of 2.

## 3.5 The pn Junction with an Applied Voltage

Having studied the open-circuited pn junction in detail, we are now ready to apply a dc voltage between its two terminals to find its electrical conduction properties. If the voltage is applied so that the p side is made more positive than the n side, it is referred to as a forward-bias  $^{6}$ voltage. Conversely, if our applied dc voltage is such that it makes the n side more positive than the p side, it is said to be a reverse-bias voltage. As will be seen, the pn junction exhibits vastly different conduction properties in its forward and reverse directions.

Our plan is as follows. We begin by a simple qualitative description in Section 3.5.1 and then consider an analytical description of the i-v characteristic of the junction in Section 3.5.2.

### 3.5.1 Qualitative Description of Junction Operation

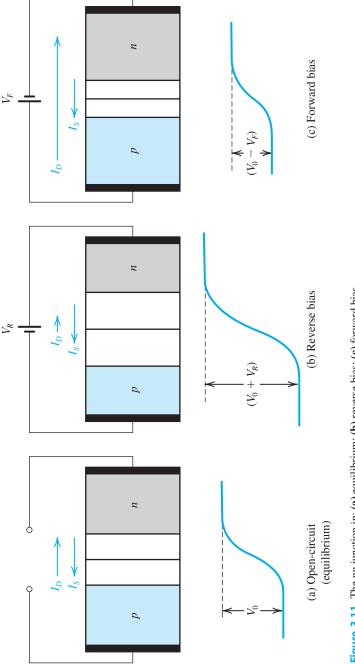

Figure 3.11 shows the pn junction under three different conditions: (a) the open-circuit or equilibrium condition studied in the previous section; (b) the reverse-bias condition, where a dc voltage  $V_R$  is applied; and (c) the forward-bias condition, where a dc voltage  $V_F$  is applied.

<sup>&</sup>lt;sup>6</sup>For the time being, we take the term *bias* to refer simply to the application of a dc voltage. We will see in later chapters that it has a deeper meaning in the design of electronic circuits.

Figure 3.11 The pn junction in: (a) equilibrium; (b) reverse bias; (c) forward bias.