# 2007 INTERNATIONAL IMAGE SENSOR WORKSHOP

June 7-10, 2007 The Cliff House Resort & Spa Ogunquit, Maine USA

## **Organized by:**

ImageSensors Inc. www.imagesensors.org

### **Technical Co-Sponsors:**

IEEE Electron Devices Society

Institute of Television Engineers of Japan (ITEJ)

Jet Propulsion Laboratory

Siimpel Corporation

Walter Kosonocky Award

### High Sensitivity of Dielectric films Structure for Advanced CMOS Image Sensor Technology

Chung-Wei Chang<sup>1, 2</sup>, Shou-Gwo Wuu<sup>1</sup>, Dun-Nian Yaung<sup>1</sup>, Chien-Hsien Tseng<sup>1</sup>, Han-Chi Liu<sup>1</sup>, David Yen<sup>1</sup>, Yi-Jiun Lin<sup>1</sup>, Chun-Ming Su<sup>1</sup>, Chun-Yao Ko<sup>1</sup>, C.Y. Yu<sup>1</sup>, C.H. Lo<sup>1</sup>, F.J.Hsiu<sup>1</sup>, C.S.Tsai<sup>1</sup>, Chung S. Wang<sup>1</sup>, Mingo Liu<sup>1</sup>, Chrong-Jung Lin<sup>2</sup>, Ya-Chin King<sup>2</sup>

<sup>1</sup>Taiwan Semiconductor Manufacturing Company, Hsin-Chu, Taiwan, R.O.C.

<sup>2</sup>Microelectronics Lab, Department of Electrical Engineering, National Tsing Hua University, Hsin-Chu, Taiwan, R.O.C. Tel:(886)35636688 Ext.7088150, Fax:(886)35784848, E-mail: <a href="mailto:cwchang@tsmc.com">cwchang@tsmc.com</a>T

#### **Abstract**

The optical effects of dielectric film properties and thickness are investigated for 0.18um enhanced CMOS image sensor. The spectral response degradation caused by destructive interference was observed in the photodiode under Si surface with thicker contact etch stop layer (CESL) and thicker oxide on Si surface. Investigations of optical effect on dielectric films show proper film structure and thickness that can result in higher quantum efficiency. In this paper, an low extinction coefficient (low-k) SIN for CESL combined with CESL/Oxide/Si films structure have been proposed by the experimental and simulation results of quantum efficiency. The spectral response can be improved and offer an optimized dielectric film thickness for CESL/Oxide/Si film structure. To improve photo-sensitivity, we also developed a high refraction-index (R.I.) inner microlens in CMOS image sensor, which result in increasing photo-sensitivity by 50% at least.

#### Introduction

There are several advantages for CMOS image sensor (CIS) compared to CCD image sensor. The CMOS image sensor (CIS) has the superior characteristics: low power consumption, selective read-out, and compatibility with CMOS logic technology and on-chip functionality [1-2]. Continuous pixel shrink has been created due to the strong demand for smaller chip size and high resolution of CIS[7-9]. As the pixel size is shrunk and CMOS technology is downscaled to deep sub-micron, the fabrication of high performance CIS will be limited by standard CMOS logic process, such as silicides and high refraction-index (R.I.) films [3-5]. An additional dielectric film as a CESL for borderless contact (BLC) has been widely used in CMOS technology to minimize the chip size by restricting the clearance of contact-to-silicon and contact-to-poly to zero [6]. The selective Co-silicide is only formed on poly-gate and Oxide is remained on S/D region and photo-diodes [7-9]. However, these additional layers will cause extra interference and reflection effect then impact the photo response of CIS. Several reports studied the optical effect on backend dielectrics structure for photosensitivity improvements [10-12]. In this paper, the actual optical response of photodiode for different film properties and thickness are proposed and lead to proper film structure, properties and thickness. In addition, the quantum efficiency (Q.E.) and reflectivity simulation show the relation between spectral response, reflectivity and dielectric films thickness to find the optimized dielectric properties for high photosensitivity. Moreover, a high R.I. inner microlens for CMOS image sensor is proposed to improve photosensitivity.

#### **Technology**

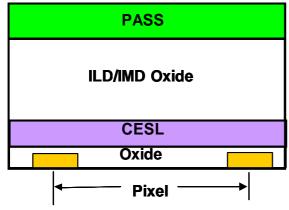

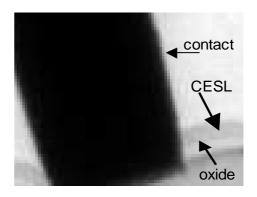

The basic technology is 0.18um enhanced CMOS image sensor technology, including shallow trench isolation (STI), retrograde channel doping, self-aligned silicide gate and S/D. Special process modifications such as non-silicide, optimized junction profile of floating node, thinner backend thickness, and shrunk contact/ well/ metal to 0.13um CIS design rule are implemented to improve pixel performance[7-9]. The advanced application software "Medici" for optical device was used to simulate the quantum efficiency of photodiodes with different dielectric films and thickness. Furthermore, in order to increase photo response when pixel size is scaled down to 2.2um, we have developed a high sensitivity of dielectric film structure, and a high refractive inner microlens for CMOS image sensor. Fig.1(a) shows the cross section of typical backend dielectric structure and photodiode under CESL/ Oxide/ Si structure for logic process. Fig.1(b) shows a cross sectional TEM picture of non-silicide S/D pixel. Co-silicide is only formed on poly-gate and oxide is remained on S/D region. Contact etch stop layer (CESL) is directly coated on Co-silicide and oxide. The n type sensor on p-sub will be dedicated for our study. The inner microlens structure was made on each pixel. The processes for inner microlens are compatible with standard CMOS logic process, just added to define inner microlens after passivation film deposition. The higher RI dielectric film for inner microlens, such SIN, enhanced the ability of inner microlens to focus the incident light.

#### **Experimental Results**

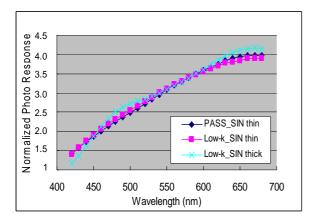

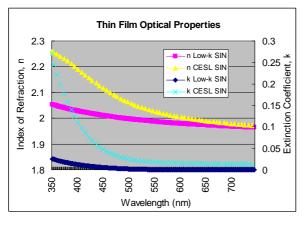

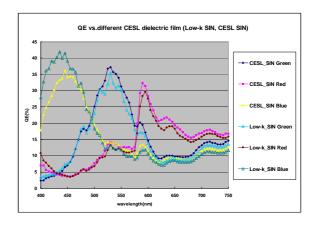

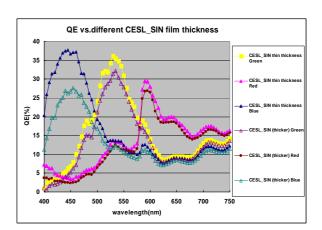

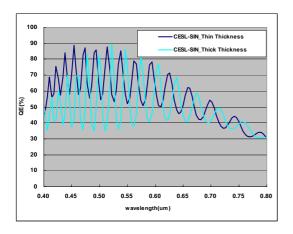

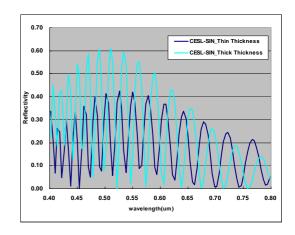

Fig.2 illustrates measured quantum efficiency with different passivation structure and thickness. Both PASS\_SIN and low-k\_SIN of passivation film show similar Q.E result, so we focused on CESL/ Oxide/Si dielectric structure in this paper. Fig.3 shows the measured quantum efficiency of photo diodes with different contact etch stop layer: (a) CESL\_SIN (b) low-k\_SIN . The low-k\_SIN shows better quantum efficiency than CESL\_SIN. It's attributed to low-k\_SIN dielectric film with low extinction coefficient (k) as Fig.4 presented. Fig.5 illustrates the measured quantum efficiency of photo diodes with different CESL\_SIN thickness at same oxide layer thickness. Increasing CESL\_SIN thickness, shows the worse quantum efficiency, especially for blue light (400nm~500nm). The simulated Q.E. of Fig.6 shows the similar results. Fig.7 plots on the reflectivity, different CESL\_SIN dielectric film thickness are interacted. The higher reflectivity and destructive interference is presented to degrade quantum efficiency of photo diodes by contact etch stop layer thickness increasing.

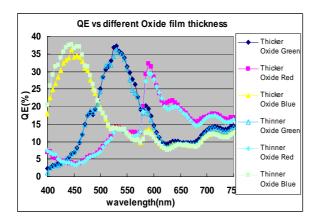

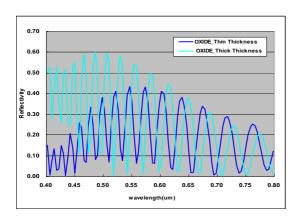

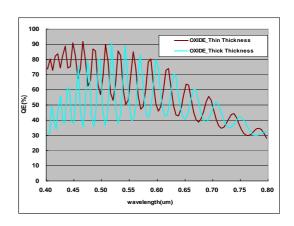

Fig.8 illustrates measured quantum efficiency of photo diodes with different oxide layer thickness at same contact etch stop layer CESL\_SIN. Increasing oxide thickness, shows the worse quantum efficiency, especially for blue light (400nm~500nm). The simulated Q.E. of Fig.9 shows the similar result, increasing oxide thickness degrades Q.E., which is more serious for short wavelength region. This higher reflectivity and destructive interference is presented when oxide thickness increasing as Fig.10 presented.

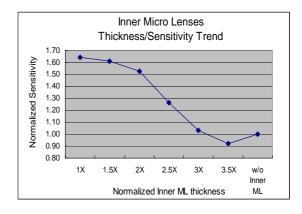

For the further improvement of sensitivity by collecting more incident light, we develop an additional dielectric inner microlens for each pixel. Fig.11 is the pixel sensitivity versus the inner microlens thickness, indicating that high photo-sensitivity is obtained for adding the inner microlens. There is more than 50% sensitivity enhancement compared with standard condition (without inner microlens). The spherical shape and curvature of inner microlens were split by dielectric thickness, the best sensitivity was performed on thinner inner microlens dielectric thickness.

#### Conclusion

The optical effects of of dielectric films structure and thickness variation have been investigated. The spectral response of photodiode is obviously dependent on dielectric film properties and thickness, especially for CESL\_SIN/Oxide/Si structure. By suppressing reflection and interference effects between CESL\_SIN/Oxide/Si structure can get the best performance. In addition, the higher sensitivity CESL dielectric film (low-k\_SIN), and high R.I inner microlens in CMOS image sensor has been successfully developed to increase photo-sensitivity further.

### Acknowledgements

The authors would like to thank R.D. McGrath, Hung Doan, Christopher. Parks, and Gang Shi of Eastman Kodak company for their valuable discussion.

#### Reference

- [1]R. M. Guidash, IEDM Tech. Dig., pp.927-929, 1997.

- [2] Sunetra K. Mendis, IEDM Tech. Dig., pp.583-586, 1993.

- [3] Hon-Sun Wong, IEDM ED, pp.2131-2142, 1996.

- [4]Hi-Deok Lee, IEEE ED, pp.1848-1850, 1998.

- [5] S. J. Park, ICVC on VLSI and CAD, pp.211-213, 1999.

- [6] W. C. Liu, IEEE EDL, pp.344-346, 2000

- [7] S. G. Wuu, IEDM Tech. Dig., pp.705-708, 2000.

- [8] H. C. Chien, IEDM Tech. Dig., pp.813-816, 2002

- [9] C.H.Tseng, IEDM Tech. Dig., pp.997-1000, 2004

- [10] Tohru Yamada, IEEE CCD&AIS workshop, pp. 131-135, 2003

- [11] T.H. Hsu, IEEE CCD&AIS workshop, pp., 2005

- [12] T.H. Hsu, IEEE EDL, pp.547-549, 2005

Fig.1(a) Cross section of typical backend dielectric structure of CIS

Fig.2 Photo response for different passivation dielectric film structure & thickness

Fig.4 Dielectric film n, k properties for contact etch stop layer

Fig.1(b) Cross sectional TEM photographs of pixel

Fig.3 Real Q.E for different CESL dielectric film structure

Fig.5 Real Q.E for different C.E.S.L dielectric film thickness

Fig.6 Simulated Q.E for different CESL\_SIN dielectric thickness

Fig.8 Real Q.E for different oxide film thickness

Fig.10 Simulated reflectivity for different oxide thickness

Fig.7 Simulated reflectivity rate for different CESL\_SIN thickness

Fig.9 Simulated Q.E for different oxide thickness

Fig.11 The inner microlens thickness and sensitivity in CMOS image sensor