# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD SAMSUNG ELECTRONICS CO., LTD., SAMSUNG ELECTRONICS AMERICA, INC., SAMSUNG SEMICONDUCTOR, INC., and SAMSUNG AUSTIN SEMICONDUCTOR LLC, Petitioner, v. W&WSENS DEVICES INC., Patent Owner.

DECLARATION OF DR. MICHAEL LEBBY, PH.D., IN SUPPORT OF PETITION FOR INTER PARTES REVIEW OF UNITED STATES PATENT NO. 10,468,543

Case IPR2025-00995 U.S. Patent No. 10,468,543

# **Table of Contents**

| I.    | INTR                         | RODUCTION                                                     | 1  |  |

|-------|------------------------------|---------------------------------------------------------------|----|--|

| II.   | SUM                          | MARY OF OPINIONS                                              | 1  |  |

| III.  | QUA                          | LIFICATIONS AND BACKGROUND                                    | 2  |  |

| IV.   | MAT                          | TERIALS CONSIDERED                                            | 11 |  |

| V.    | LEG                          | AL STANDARDS                                                  | 15 |  |

|       | A.                           | Level of Ordinary Skill                                       | 16 |  |

|       | B.                           | Prior Art                                                     | 17 |  |

|       | C.                           | Anticipation                                                  | 17 |  |

|       | D.                           | Obviousness                                                   | 18 |  |

| VI.   |                              | HNOLOGY BACKGROUND AND STATE OF THE PRIOR                     | 23 |  |

|       | A.                           | Photodetectors                                                | 23 |  |

|       | B.                           | Microstructure-Enhanced Photodetectors                        | 24 |  |

|       | C.                           | Photodetectors and Processing Circuitry on a Single Substrate | 27 |  |

| VII.  | THE                          | '543 Patent                                                   | 32 |  |

|       | A.                           | Alleged Invention of the '543 Patent                          | 32 |  |

|       | B.                           | Prosecution History                                           | 33 |  |

|       | C.                           | Claim Construction                                            | 37 |  |

| VIII. | SUM                          | MARY OF THE PRIOR ART                                         | 39 |  |

|       | A.                           | Kuboi                                                         | 39 |  |

| IX.   | LEV                          | EL OF ORDINARY SKILL IN THE ART                               | 45 |  |

| X.    | GROUNDS OF UNPATENTABILITY46 |                                                               |    |  |

| XI. |    |      |         | GED CLAIMS ARE UNPATENTABLE OVER Γ                                                                                                                                                                                                          | .47 |

|-----|----|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | A. | 24-2 | 6, 28-3 | Grounds 1A/1B: Claims 1-4, 7, 9-12, 16-17, 20-21, 80, 32, and 35 Are Anticipated by <i>Kuboi</i> (Ground ovious over <i>Kuboi</i> (Ground 1B)                                                                                               | 47  |

|     |    | 1.   | Inde    | pendent Claim 1                                                                                                                                                                                                                             | 47  |

|     |    |      | a.      | [1pre(a)]: "A single-chip device comprising an integrated combination of a microstructure-enhanced photodetector (MSPD) configured for reverse-bias operation and an active electronic circuit,"                                            | 47  |

|     |    |      | b.      | [1pre(b)]: "both formed on or in a single substrate"                                                                                                                                                                                        | 56  |

|     |    |      | c.      | [1pre(c)]: "and configured to receive an optical input that in cross-section is substantially continuous spatially, convert the optical input to an electrical output, and process the electrical output into a processed output, wherein:" | 59  |

|     |    |      | d.      | [1a]: "the MSPD on or in said single substrate comprises an intermediate region, a first region at one side of the intermediate region, and a second region at an opposite side of the intermediate region, wherein:"                       | 66  |

|     |    |      | e.      | [1b]: "each of the regions comprises Silicon,<br>Germanium, or an alloy thereof;"                                                                                                                                                           | 67  |

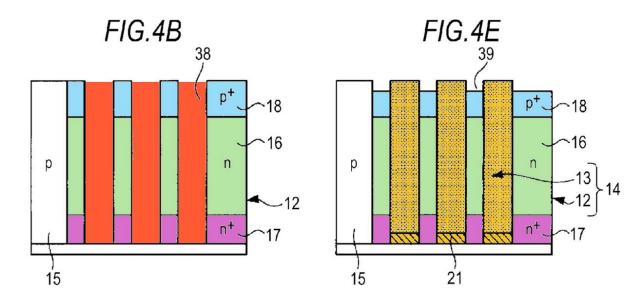

|     |    |      | f.      | [1c]: "at least one of said regions, and an optional overlying covering region, have holes intentionally formed therein"                                                                                                                    | 68  |

|     |    |      | g.      | [1d]: "each of the first and second regions comprises a doped material;"                                                                                                                                                                    | 75  |

|     |    |      | h.      | [1e]: "the intermediate region comprises a material that is less doped than at least one of the first and second regions or is undoped, wherein the degree                                                                                  |     |

2.

|       | positions in the intermediate region;"                                                                                                                                                                                             | 76  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| i.    | [1f]: "an input portion configured to concurrently receive at a plurality of said holes said optical input that has said substantially continuous cross-section; and"                                                              | 83  |

| j.    | [1g]: "an output portion configured to provide said electrical output from the MSPD;"                                                                                                                                              | 85  |

| k.    | [1h]: "the MSPD includes reverse-bias contacts coupled therewith to establish an electrical field therein when energized to thereby sweep in a selected direction electrical charges generated in the MSPD by said optical input;" | 87  |

| 1.    | [1i]: "the active electronic circuit on or in said single substrate is configured to process the electrical output from the MSPD by applying thereto:"                                                                             | 91  |

| m.    | [1j]: "amplification to form said processed output from the single-chip device;"                                                                                                                                                   | 93  |

| n.    | [1k]: "processing other than or in addition to amplification to form said processed output from the single-chip device; and"                                                                                                       | 96  |

| 0.    | [11]: "routing to one or more selected destinations; and"                                                                                                                                                                          | 97  |

| p.    | [1m]: "a communication channel on or in said single-chip device, configured to deliver the electrical output from the MSPD to the active electronic circuit."                                                                      | 101 |

| Clain | n 2                                                                                                                                                                                                                                | 103 |

| a.    | [2]: "The single-chip device of claim 1, in which said active electronic circuit at least partly extends beyond said substrate."                                                                                                   | 103 |

| 3. | Clain | n 3                                                                                                                                                                                        | 106 |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

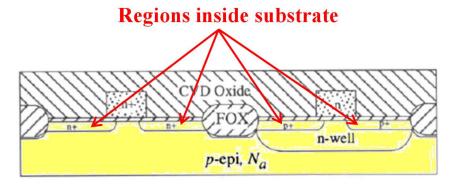

|    | a.    | [3]: "The single-chip device of claim 1, in which said active electronic circuit is at least partly inside said substrate."                                                                | 106 |

| 4. | Clain | n 4                                                                                                                                                                                        | 107 |

|    | a.    | [4]: "The single-chip device of claim 1, in which said overlying region is present as a superstrate at one side of said first, intermediate, and second regions, and contains said holes." | 107 |

| 5. | Clain | n 7                                                                                                                                                                                        | 109 |

|    | a.    | [7]: "The single-chip device of claim 1, further including a region of a dielectric material that covers the holes and is in the propagation path of said optical input."                  | 109 |

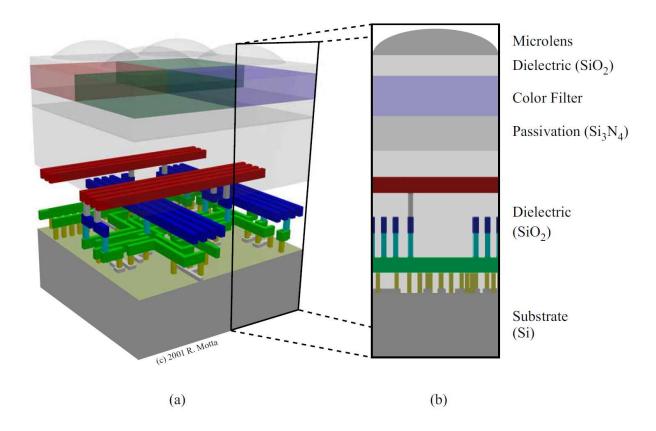

| 6. | Clain | n 9                                                                                                                                                                                        | 112 |

|    | a.    | [9]: "The single-chip device of claim 1, in which said holes are present in said intermediate region."                                                                                     | 112 |

| 7. | Clain | n 10                                                                                                                                                                                       | 114 |

|    | a.    | [10]: "The single-chip device of claim 1, in which said holes are present in said intermediate region as well as in at least one of the first and second regions."                         | 114 |

| 8. | Clain | n 11                                                                                                                                                                                       | 115 |

|    | a.    | [11]: "The single-chip device of claim 1, in which said holes are present in each of the first, second, and intermediate region."                                                          | 115 |

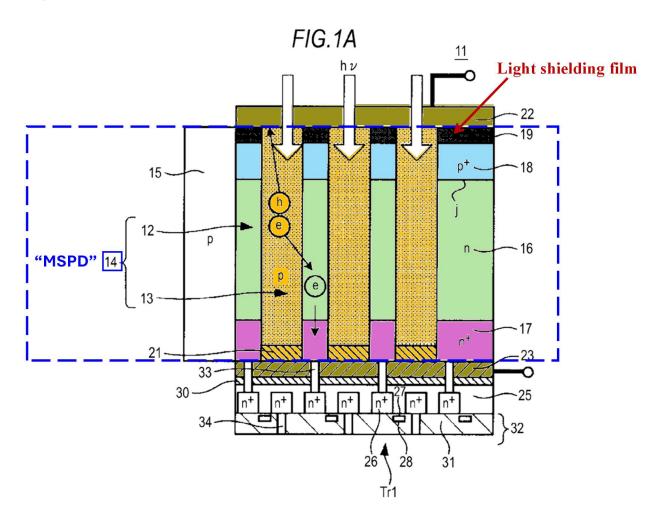

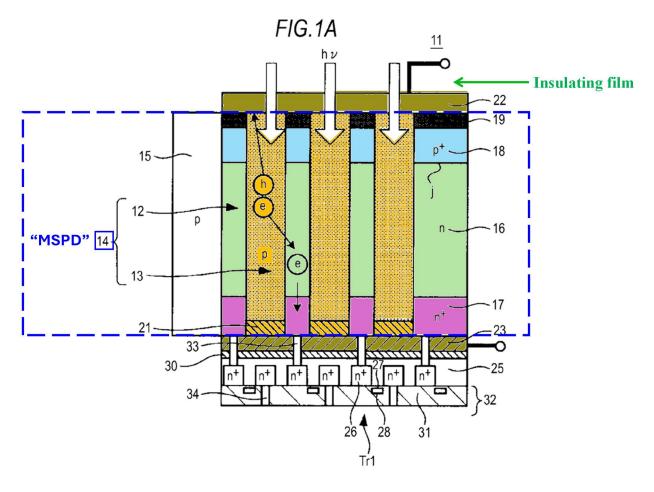

| 9. | Clain | n 12                                                                                                                                                                                       | 115 |

|    | a.    | [12]: "The single-chip device of claim 1, in which each of said first and second regions and said intermediate region has a thickness and at least                                         |     |

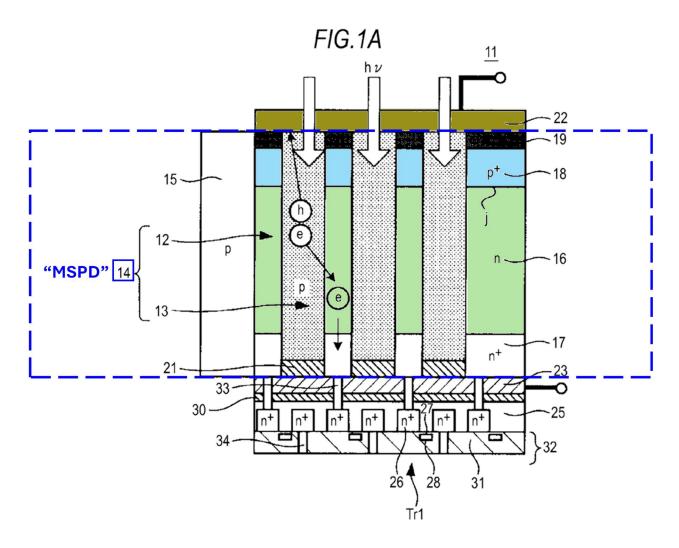

|     |       | some of said holes extend through the entire thickness of said intermediate region and of one of said first region and second region and through at least a part of the thickness of the other one of said first and second regions." | 115 |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10. | Claim | 16                                                                                                                                                                                                                                    | 119 |

|     | a.    | [16]: "The single-chip device of claim 1, in which at least some of said holes have sidewalls that slope in planes transverse to said regions."                                                                                       | 119 |

| 11. | Claim | 17                                                                                                                                                                                                                                    | 123 |

|     | a.    | [17]: "The single-chip device of claim 1, in which at least some of said holes have sidewalls with plural different slopes along the inside walls of the holes."                                                                      | 123 |

| 12. | Claim | ı 20                                                                                                                                                                                                                                  | 124 |

|     | a.    | [20]: "The single-chip device of claim 1, in which the holes are at least partly filled with a dielectric material."                                                                                                                  | 124 |

| 13. | Claim | ı 21                                                                                                                                                                                                                                  | 126 |

|     | a.    | [21]: "The single-chip device of claim 1, in which the holes are entirely filled with a dielectric material."                                                                                                                         | 126 |

| 14. | Claim | 1 24                                                                                                                                                                                                                                  | 129 |

|     | a.    | [24]: "The single-chip device of claim 1, in which said MSPD further comprises ohmic contacts configured for reverse-biasing the MSPD."                                                                                               | 129 |

| 15. | Claim | 1 25                                                                                                                                                                                                                                  | 131 |

|     | a.    | [25]: "The single-chip device of claim 1, in which the MSPD further includes ohmic contacts to said first and second regions, at least one of said ohmic contact[s] being through a via in said substrate."                           | 131 |

| 16. | Clain | 1 26                                                                                                                                                                                                                                                                                                                                                                            | 137 |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | a.    | [26a]: "The single-chip device of claim 1, further comprising a light guide to said MSPD for directing said optical input thereto,"                                                                                                                                                                                                                                             | 137 |

|     | b.    | [26b]: "and electrical contacts from the active electronic circuit configured to carry said processed output out of the single-chip device."                                                                                                                                                                                                                                    | 140 |

| 17. | Clain | n 28                                                                                                                                                                                                                                                                                                                                                                            | 142 |

|     | a.    | [28a]: "The single-chip device of claim 1, further comprising one or more additional MSPD on or in the same substrate,"                                                                                                                                                                                                                                                         | 142 |

|     | b.    | [28b]: "and respective different optical bandpass filters coupled with at least two of the MSPDs on or in said single substrate, whereby at least two of said MSPDs are configured to respond to different wavelength ranges that are within said optical input."                                                                                                               | 145 |

| 18. | Clain | n 29                                                                                                                                                                                                                                                                                                                                                                            | 147 |

|     | a.    | [29]: "The single-chip device of claim 1, further comprising one or more additional MSPDs on or in said single substrate, one or more additional active electronic circuits on or in the said single substrate, and one or more additional communication channels configured to supply electrical outputs from the MSPDs to the one or more of the active electronic circuits." | 147 |

| 19. | Clain | n 30                                                                                                                                                                                                                                                                                                                                                                            | 150 |

|     | a.    | [30]: "The single-chip device of claim 1, further comprising one or more additional active electronic circuits that are formed on or in the said single substrate."                                                                                                                                                                                                             | 150 |

| 20  | Clain | 1 32                                                                                                                                                                                                                                                                                                                                                                            | 151 |

|        |         | a.    | [32]: "The single-chip device of claim 1, further                                                                                                                                                                                            |     |

|--------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        |         |       | comprising one or more additional active                                                                                                                                                                                                     |     |

|        |         |       | electronic circuits that are formed on or in the said                                                                                                                                                                                        |     |

|        |         |       | single substrate and comprise one or more of                                                                                                                                                                                                 |     |

|        |         |       | CMOS, BiCMOS, and bipolar active devices."                                                                                                                                                                                                   | 151 |

|        | 21.     | Clair | m 35                                                                                                                                                                                                                                         | 152 |

|        |         | a.    | [35]: "The single-chip device of claim 1, further including a region of selected material that is over a side of one of the first and second regions facing away from the intermediate region and is configured to reduce sheet resistance." | 152 |

|        |         |       | configured to reduce sheet resistance                                                                                                                                                                                                        | 132 |

| XII. ( | CONCLUS | JON   |                                                                                                                                                                                                                                              | 154 |

### I. INTRODUCTION

- 1. I, Michael Lebby, Ph.D., have been retained as an independent expert by Samsung Electronics Co., Ltd.; Samsung Electronics America, Inc.; Samsung Semiconductor, Inc.; and Samsung Austin Semiconductor LLC (collectively, "Samsung" or "Petitioner") in connection with an *inter partes* review (IPR) of U.S. Patent No. 10,468,543 ("the '543 Patent") (Ex. 1042). I have prepared this declaration in connection with Samsung's Petition for *Inter Partes* Review.

- 2. Specifically, this document contains my opinions about the technology in claims 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35 of the '543 Patent and the grounds against these claims that have been asserted by Samsung. I was not asked to provide any opinions about the '543 Patent that are not expressed herein.

### II. SUMMARY OF OPINIONS

- 3. This declaration considers claims 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35 of the '543 Patent. Below, I set forth the opinions I have formed, the conclusions I have reached, and the bases for these opinions and conclusions. I believe the statements contained in this declaration to be true and correct to the best of my knowledge.

- 4. Based on my experience, knowledge of the art at the time of the applicable priority date (I was told to assume a priority date of May 22, 2013), it is

my opinion that claims 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35 of the '543 Patent would have been anticipated and/or obvious based on the asserted grounds discussed below.

5. I am being compensated for my time at my normal hourly rate. My compensation is in no way contingent upon the nature of my findings, the presentation of my findings in testimony, or the outcome of this proceeding.

### III. QUALIFICATIONS AND BACKGROUND

- 6. I believe that I am well qualified to serve as a technical expert in this matter based upon my qualifications, discussed in detail below. A copy of my curriculum vitae is attached as Appendix A to this declaration.

- 7. Based on my education, research, and work experience, I am knowledgeable about the subject matter of the '543 Patent and the related prior art.

- 8. In what follows, I provide a short summary of my qualifications.

- 9. I am an engineer with a Ph.D. in Electrical and Electronic Engineering and have worked extensively with optoelectronics, photonics, electrical and electronic circuits, optical systems, as well as integrated circuit semiconductors for both optoelectronic and electronic solutions. Overall, I have approximately 40 years of experience working in industry to develop new electronic, photonic, display, and optics-based products, which I have taken from research to manufacturing.

- 10. I received a Bachelor of Engineering degree in Electrical and Electronic Engineering in 1984 from the University of Bradford, United Kingdom. I also received a Ph.D. in Electrical and Electronic Engineering in 1987 from the University of Bradford, United Kingdom. I also received a second doctorate degree: a Doctor of Engineering degree (D.Eng) in electrical and electronic engineering in 2004 from the University of Bradford, United Kingdom.

- 11. I am currently Chief Executive Officer (CEO) and Chief Technology Officer (CTO) of GenusTechnik Inc., which is my consulting company, through which I engage in my expert witness work.

- 12. I recently retired in late 2024 as Chairman and CEO of Lightwave Logic Inc. (NASDAQ: LWLG), where I served as a Director of the Board of Directors since 2015.

- 13. I am a named inventor on over 225 U.S. utility patents. My work has also led to me either being an inventor or co-inventor in subjects such as: semiconductors, electronics, optics, displays, high frequency optical and electronic products such as lasers and LEDs, as well as photonic integrated circuits. I am the author of more than 60 publications.

- 14. I am a Fellow grade of three professional organizations: IEEE (Institute of Electrical and Electronic Engineers), NAI (National Academy of Inventors), and Optica (Optical Society of America).

- As described in this Section, and further detailed in my curriculum 15. vitae (Appendix A) over the course of my 40-year career in electronics and optoelectronics, I have worked in nearly every aspect of the electronic, semiconductor, and optoelectronics business, ranging from wafers to components, to modules, displays, optics, connectors and cable technology. At the wafer level, I have experience in epitaxial wafer growth (compound semiconductors). I also have experience in electrical and optoelectronic device and circuit design, using modeling and simulation, electrical and optoelectronic device and component fabrication, testing, and qualification, implementation of devices such as laser diodes, light emitting diodes, photodetectors etc., into packages, connectors, and panels, both hermetic and non-hermetic, as well as analysis of package/panel materials such as plastics (including plastic housings such as resin-packaged lead frame housings), optical plastics, metallic-based packages, semiconductor-based packages, and ceramic-based packages for fiber optics, displays, and datacommunications industries. I have also designed device packages (through-pin, surface mount, flip-chip, and various combinations thereof) for printed circuit board mounting as well as electrical and optical components for various industrial

and environmental applications. Many of the designed components were implemented into technology applications both as manufactured products as well as components for testing, characterization and analysis of qualified products for volume scaling. The components were designed to work at both at optical and RF frequencies that include both optical and RF wireless as well as fiber-optics based applications. I have also worked in commercially based industrial research-and-development laboratories to bring new high-performance optoelectronic- and photonic-based technologies from the research proof-of-concept phase through prototyping up to and including qualified manufacturing for volume release. This has included both transfer of as well as the design of optics and optical systems for various commercial systems.

- 16. I have been both an entrepreneur (*e.g.*, Ignis Optics Inc, One Chip Photonics, Lightwave Logic Inc.), as well as an intrapreneur (*e.g.*, Motorola, Intel, TE Connectivity (previously Tyco Electronics), AT&T Bell Labs), creating innovative new high technology programs, both as venture backed start-ups as well as corporate funded divisions. I have built these entities to develop optical, electronic, optoelectronics, and photonics technology from the laboratory and fabrication clean room to production factories.

- 17. My career started in the late 1970s at the Ministry of Defense in the United Kingdom where I spent time at a number of their R&D facilities including

Malvern (RSRE – Royal Signals and Radar Establishment). There, I worked on electronic and optoelectronic semiconductor device design, as well as basic and high frequency telecommunications and data-communications electronics for module, cable, connector, and circuit implementation. My research work in electronics then took me to AT&T Bell Laboratories in 1985, where I pursued research in novel electronic and optoelectronic semiconductor material systems that included laser diodes, LEDs, photodetectors, optical waveguides, optics, and standard electronic devices as well as the processing and fabrication for such devices. The devices researched at Bell Labs became in part the subject of my Ph.D. thesis for which I was granted a doctoral degree in 1987.

18. I moved to Motorola in 1989 to further develop my skills in consumer commercial application of technology and focused on optoelectronics, and semiconductor engineering and development. I became a Research and Development Manager in Motorola, until I left the company in 1998. During my time at Motorola, I worked on many photonic, electronic, and optical technology projects that included projection, display, optics, LEDs, OLEDs, laser diodes, phosphors, cameras, as well as the packaging and reliability of mobile product prototypes. At that time, I was particularly interested in miniaturization of electronics, optics, and optoelectronics, and worked on novel optical designs that included portable heads-up displays, optical heads for storage, and various light-

based prototypes as well as advanced prototypes of futuristic communications and consumer hardware and cameras.

- 19. The research work at Motorola also included work on displays and in particular, miniature displays, arrays, imagers, projection systems, and optics for pagers, clam-shell phones, and head-mounted displays that included mounting onto eyeglasses (similar in concept to Google glass<sup>TM</sup>) as well as techniques for electrical and optical connections in these applications.

- 20. I also initiated Motorola's work in optical interconnect (Optobus<sup>™</sup>) technology, that incorporated both transfer and injection molded optical parts and included the design of electrical and optical connector technology. This project involved the research and development of a multi-channel electronic IC chip for parallel optical interconnects as well as optical simulations of performance.

- 21. I was one of Motorola's most prolific inventors, having over 150 issued utility patents as an inventor or a co-inventor by the late 1990s. Many of the photonics and optical prototypes with which I was involved were subject to reliability and stress testing as well as optical measurement analysis. These consumer products all were driven using standard electronic ICs and electronic signaling where I had a role in design and simulation of these circuits.

- 22. Between 1998 and 1999, I worked as the Director of Technology/BD (Fiber Optics) for Tyco Electronics (previously AMP). I joined Tyco Electronics as a business development director and director of advanced technology for the telecommunications and data-communications industries. I was responsible for growing the optical and optoelectronic technology business through external interactions that included mergers, acquisitions, strategic alliances, and technical strategic planning as well as leading new technology projects.

- 23. In 1999, I left Tyco and started employment at Intel. At Intel, I was involved heavily in photonic technology, especially technology that supported silicon photonic device platforms with different types of displays and optical systems. As a culmination of this work, I was one of Intel's founders of its silicon photonics division in the year 2000, and worked to set up a fabrication facility in South San Jose, California, USA. The work involved integrating silicon FET electronics with optoelectronics and optics onto the same silicon semiconductor wafer. This included CMOS detectors and arrays. I was also part of Intel Capital's optical investment team, and participated in over 30 photonics investment projects into photonics, optics, and optoelectronics. My focus included optical devices, packaging and modules for optical storage, consumer applications such as displays, cameras, projection, communications, and sensing. The technologies that I

investigated included lasers, LEDs, optics, LCDs, optical waveguides, cameras, imagers, and optical displays.

- 24. At the end of 2000, I left Intel and raised venture capital funding for a company called Ignis Optics Inc. The main goal of the company was to design and manufacture, in high volume, very high-performance optoelectronic modules. These fiber optic transceiver modules have the capability of transmitting and receiving optical signals that are controlled using programmable electronics and packaged optoelectronics chips, such as laser diodes, optical lenses, and photodetectors.

- 25. In 2005, I took up employment for a trade association, based in Washington, D.C., called IEEE Optoelectronics Industry Development Association (OIDA). As head of this trade association, and with electronics, photonics and optics manufacturers that included manufacturers of projection displays, optical systems, fiber optics, display, cameras, sensing, defense, aerospace, LED lighting, and automotive vendors as members, I was responsible, in part, for industry-based technology roadmaps; and I implemented common industry roadmap methodologies with common features such as "Red Brick Walls" and transferred them into technology roadmaps for the industry in which displays, optics, optical sensors, telecommunications cables, fiber-optic cables, fiber, cameras, and their

associated technology platforms, were featured. OIDA roadmaps featured purple brick walls, to show differentiation from the semiconductor industry.

- 26. In 2010, I became the General Manager and CTO of Translucent, Inc., a high-tech start-up company which developed and manufactured silicon and rare earth oxide based epitaxial semiconductor wafers. I patented a number of optoelectronic and electronic device designs using rare earth oxides and phosphors while employed at Translucent.

- 27. Throughout my career, I have also had an active role in a number of technical professional organizations, including, among others, IEEE Components, Packaging, and Manufacturing Technology (CPMT), IEEE Electronic Components and Technology Conferences (ECTC); IEEE TC-10 (Technical Committee on Optoelectronics), and IEEE Optoelectronics Industry Development Association (OIDA). Through these organizations, I have consistently been a part of committees, events, and workshops relating to semiconductor, optoelectronics, electronics, and packaging technology.

- 28. I also serve as a Technical Expert/Consultant for the European Commission. In my work at the European Commission, I review and advise on general optics, photonics, electronics, telecommunications, semiconductors, optoelectronics, imaging, sensing, cameras, display (*e.g.*, LCD, LED, OLED, etc.), and related Information and Communications Technology (ICT).

29. A full list of my patents and journal publications in addition to my academic and industrial experience is further detailed in my curriculum vitae, which is attached to this declaration as Appendix A.

### IV. MATERIALS CONSIDERED

30. In forming my opinions, I have analyzed the materials listed in the Table below. My opinions are based on my experience, knowledge of the relevant art, the documents identified in the Table below, as well as the documents directly cited to in this declaration.

| Exhibit  | Description                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1001 | U.S. Patent No. 10,446,700 to Wang et al. ("'700 Patent")                                                                         |

| Ex. 1003 | Prosecution History of the '700 Patent (downloaded from Public PAIR)                                                              |

| Ex. 1004 | U.S. Patent Application Publication No. 2012/0049044 A1 to Kuboi (" <i>Kuboi</i> ")                                               |

| Ex. 1005 | U.S. Patent Application Publication No. 2012/0033119 A1 to Shinohara ("Shinohara")                                                |

| Ex. 1006 | European Patent Application EP 2 172 974 A1 to NXP B.V. ("NXP")                                                                   |

| Ex. 1007 | U.S. Patent Application Publication No. 2008/0259981 A1 to Wang et al. ("Wang")                                                   |

| Ex. 1008 | U.S. Patent Application Publication No. 2009/0133741 A1 to Higuchi et al. ("Higuchi")                                             |

| Ex. 1009 | Tapan K. Gupta, <i>Copper Interconnect Technology</i> , (Springer Science+Business Media, LLC 2009), pp. 67-71.                   |

| Ex. 1010 | Zhihong Huang et al., <i>Microstructured silicon photodetector</i> , Applied Physics Letters, Vol. 89 (2006), pp. 033506-1 to -3. |

| Exhibit  | Description                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1011 | Richard A. Myers et al., Enhancing near-infrared avalanche photodiode performance by femtosecond laser microstructuring, Applied Optics, Vol. 45, No. 35 (Dec. 2006), pp. 8825-31.                                                                                                                                                                                                |

| Ex. 1012 | Abbas El Gamal et al., <i>CMOS Image Sensors</i> , IEEE Circuits & Devices Magazine (2005), pp. 6-20.                                                                                                                                                                                                                                                                             |

| Ex. 1013 | Eric R. Fossum, <i>CMOS Image Sensors: Electronic Camera-On-A-Chip</i> , IEEE Transactions on Electron Devices, Vol. 44, No. 10 (Oct. 1997), pp. 1689-98.                                                                                                                                                                                                                         |

| Ex. 1014 | Sunetra Mendis et al., <i>CMOS Active Pixel Image Sensor</i> , IEEE Transactions on Electron Devices, Vol. 41, No. 3 (Mar. 1994), pp. 452-53.                                                                                                                                                                                                                                     |

| Ex. 1015 | Renato Turchetta et al., <i>Introduction to CMOS Image Sensors</i> , Molecular Expressions <sup>TM</sup> Optical Microscopy Primer: Digital Imaging in Optical Microscopy - Introduction to CMOS Image Sensors (July 16, 2004), pp. 1-9, <i>available at</i> https://web.archive.org/web/20120508153832/https://micro.magne t.fsu.edu/primer/digitalimaging/cmosimagesensors.html |

| Ex. 1016 | Ming-Dou Ker et al., <i>Investigation on Device Characteristics of MOSFET Transistor Placed Under Bond Pad for High-Pin-Count SOC Applications</i> , IEEE Transactions on Components and Packaging Technologies, Vol. 27, No. 3 (Sept. 2004), pp. 452-60.                                                                                                                         |

| Ex. 1017 | Paul Horowitz et al., <i>The Art of Electronics</i> (Cambridge University Press, New York 3d ed. 2016), pp. 1, 11, 52, 71.                                                                                                                                                                                                                                                        |

| Ex. 1018 | Electrical Engineering Dictionary - CRCnetBase (Phillip A. Laplante editor-in-chief, CRC Press LLC 2000), pp. 1-6.                                                                                                                                                                                                                                                                |

| Ex. 1019 | S.M. Sze et al., <i>Semiconductor Devices Physics and Technology</i> , (John Wiley & Sons, Inc. 3d ed. 2012), pp. 205-10, 325-26, 392-400, 416-417, 466-67.                                                                                                                                                                                                                       |

| Ex. 1020 | John P. Uyemura, <i>CMOS Logic Circuit Design</i> (Kluwer Academic Publishers 2002), pp. 64, 74-102, 315-17, 458-60.                                                                                                                                                                                                                                                              |

| Ex. 1021 | Khalil Jumah Tawfiq Hamam, Organic Solar Cells Based on High Dielectric Constant Materials: An Approach to Increase Efficiency (June 2013) (Ph.D. dissertation, Western Michigan University), pp. 1-122.                                                                                                                                                                          |

| Exhibit  | Description                                                                                                                                                                                      |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1022 | P. Kalugasalam et al., <i>Dielectric and AC Conduction Studies of Lead Phthalocyanine Thin Film</i> , Chalcogenide Letters, Vol. 6, No. 9 (Sept. 2009), pp. 469-76.                              |

| Ex. 1023 | Gopal G. Pethuraja et al., <i>Current-Voltage Characteristics of ITO/p-Si and ITO/n-Si Contact Interfaces</i> , Advances in Materials Physics and Chemistry, Vol. 2 (2012), pp. 59-62.           |

| Ex. 1024 | Giampiero de Cesare et al., Electrical Properties of ITO/Crystalline-Silicon Contact at Different Deposition Temperatures, IEEE Electron Device Letters, Vol. 33, No. 3 (Mar. 2012), pp. 327-29. |

| Ex. 1025 | Wen-Jang Jiang et al., <i>The effect of indium tin oxide as an ohmic contact for the 850 nm GaAs oxide-confined VCSELs</i> , Solid-State Electronics, Vol. 46 (2002), pp. 1945-48.               |

| Ex. 1026 | <i>IEEE 100 - The Authoritative Dictionary of IEEE Standards Terms</i> , IEEE (7th ed. 2000), pp. 333, 1205.                                                                                     |

| Ex. 1027 | Christian C. Fesenmaier et al., <i>Optical confinement methods for continued scaling of CMOS image sensor pixels</i> , Optics Express, Vol. 16, No. 25 (Dec. 2008), pp. 20457-70.                |

| Ex. 1028 | Leonard Rubin et al., <i>Ion Implantation in Silicon Technology</i> , Industrial Physicist, 9(3), (Jun/July 2003), pp. 12-15.                                                                    |

| Ex. 1029 | Jurgen Michel et al., <i>Advances in fully CMOS integrated photonic devices</i> , Proceedings of SPIE, Vol. 6477 (2007), pp. 64770P-1 to -11.                                                    |

| Ex. 1030 | Mark Beals et al., <i>Process Flow Innovations for Photonic Device Integration in CMOS</i> , Proceedings of SPIE, Vol. 6898 (2008), pp. 689804-1 to -14.                                         |

| Ex. 1031 | Donald A. Neaman, <i>Semiconductor Physics and Devices – Basic Principles</i> (McGraw Hill 3d ed. 2003), pp. 247-50, 260-61.                                                                     |

| Ex. 1032 | Adel S. Sedra et al., <i>Microelectronic Circuits</i> (Oxford University Press 7th ed. 2015), pp. 155-56.                                                                                        |

| Ex. 1033 | Chung-Wei Chang et al., High Sensitivity of Dielectric films<br>Structure for Advanced CMOS Image Sensor Technology, 2007                                                                        |

| Exhibit  | Description                                                                                                                                                                                                                                      |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | International Image Sensor Workshop, IEEE Electron Devices Society (2007), pp. 207-10.                                                                                                                                                           |

| Ex. 1034 | Matthew Sauceda, <i>Porphyrin Thin Film Dielectrics</i> , SUNFEST Technical Report TR-CST01NOV04, Center for Sensor Technologies, Univ. of Pennsylvania, Philadelphia, PA (2004), pp. 181-98.                                                    |

| Ex. 1035 | N. Venkatramaiah et al., <i>Spectroscopic and dielectric studies of meso-tetrakis(p-sulfonatophenyl) porphyrin doped hybrid borate glasses</i> , Journal of Alloys and Compounds, Vol. 509 (2011), pp. 2797-803.                                 |

| Ex. 1036 | Tom J. Savenije, <i>Photogeneration and transport of charge carriers in a porphyrin p/n heterojunction</i> , Physical Review B, Vol. 55, No. 15 (Apr. 1997), pp. 9685-92.                                                                        |

| Ex. 1037 | Ümit Salan et al., Synthesis, characterization, electrical and dielectric permittivity measurements of 2,9,16,23-tetra(4-ferrocenylimino-3-nitrophenoxy)phthalocyanines, Journal of Porphyrins and Phthalocyanines, Vol. 10 (2006), pp. 1263-70. |

| Ex. 1038 | Teresa M. Figueira-Duarte et al., <i>Pyrene-Based Materials for Organic Electronics</i> , Chemical Reviews, Vol. 111 (2011), pp. 7260-314.                                                                                                       |

| Ex. 1039 | Handbook of Wafer Bonding (Peter Ramm et al. eds., Wiley-VCH Verlag & Co. KGaA 2012), pp. 52-54, 63-64, 112-15.                                                                                                                                  |

| Ex. 1042 | U.S. Patent No. 10,468,543 B2 to Wang et al. ("'543 Patent")                                                                                                                                                                                     |

| Ex. 1044 | Prosecution History of the '543 Patent (downloaded from Public PAIR)                                                                                                                                                                             |

| Ex. 1045 | J. W. Levell et al., A hybrid organic semiconductor/silicon                                                                                                                                                                                      |

|          | photodiode for efficient ultraviolet photodetection, Optics Express, Vol. 18, No. 4 (2010), pp. 3219-3225.                                                                                                                                       |

| Ex. 1046 | W&Wsens Devices Inc. v. Samsung Electronics Co. Ltd. et al.,<br>Case No. 2:24-cv-00854, Plaintiff's Infringement Contentions,<br>Appendix C-1 (Jan. 7, 2025)                                                                                     |

| Exhibit  | Description                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1047 | W&Wsens Devices Inc. v. Samsung Electronics Co. Ltd. et al.,<br>Case No. 2:24-cv-00854, Plaintiff's Infringement Contentions,<br>Appendix C-2 (Jan. 7, 2025) |

### V. LEGAL STANDARDS

- 31. I am not a lawyer. My understanding of the legal standards to apply in reaching the conclusions in this declaration is based on discussions with counsel for Petitioner, my experience applying similar standards in other patent-related matters, and my reading of the documents submitted in this proceeding. In preparing this declaration, I have tried to faithfully apply these legal standards to the challenged claims.

- 32. I have been informed that there are two ways in which prior art may render a patent claim unpatentable. First, I have been informed that the prior art can "anticipate" a claim. Second, I have been informed that the prior art can render a claim "obvious" to a person of ordinary skill in the art. I understand that a claim is patentable if it was not anticipated and would not have been obvious by the prior art at the effective filing date of the patent.

- 33. I have been informed that a dependent claim is a patent claim that refers back to another patent claim. I have been informed that a dependent claim includes all of the limitations of the claim to which it refers.

- 34. I have been asked to provide my opinions as to whether the cited prior art teaches or renders obvious claims 1-4, 7, 9-12, 16-17, 20-21, 24-26, 28-30, 32, and 35 of the '543 Patent from the perspective of a person of ordinary skill in the art at the '543 Patent's earliest claimed priority date (May 22, 2013), as described in more detail below.

- 35. I have been informed that in *inter partes* review proceedings, such as this one, the party challenging the patent bears the burden of proving unpatentability by a preponderance of the evidence. I understand that a preponderance of the evidence means "more likely than not."

- 36. For purposes of this declaration, I have been asked to provide my opinions on issues regarding unpatentability. I have been informed of the following legal standards, which I have applied in forming my opinions.

## A. Level of Ordinary Skill

37. I have been informed that a person of ordinary skill in the art is determined by considering several factors, including the (i) type of problems encountered in the art; (ii) prior art solutions to those problems; (iii) rapidity with which innovations are made; (iv) sophistication of the technology; and (v) educational level of active workers in the field.

38. I have been instructed to assume a person of ordinary skill in the art is not a specific real individual, but rather a hypothetical individual having the qualities reflected by the factors discussed above.

### B. Prior Art

39. I have been advised and understand the information used to evaluate whether an invention was new and not obvious when made is generally referred to as "prior art." I understand that prior art includes patents and printed publications that existed before the earliest claimed priority date or the earliest filing date of the patent (which I have been informed is also called the "effective filing date"). I have been informed and understand that a patent or published patent application is prior art if it was filed before the earliest filing date of the claimed invention and that a printed publication is prior art if it was publicly available before the earliest filing date.

### C. Anticipation

40. I have been informed that under 35 U.S.C. § 102, a patent claim is unpatentable for anticipation if it is not novel, including if the claimed subject matter was patented or described in a printed publication before the effective filing date of the claimed invention. I have been informed that this is referred to as unpatentability by anticipation. I have been informed that a patent claim is

anticipated under § 102 if a single prior art reference discloses all limitations of the claimed invention.

### D. Obviousness

- 41. I have been informed that under 35 U.S.C. § 103, a patent claim is unpatentable if the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious to a person having ordinary skill in the art to which said subject matter pertains at the time the invention was made. I have been informed that this is referred to as unpatentability by obviousness.

- 42. I have been informed that a proper obviousness analysis includes the following:

- a. Determining the scope and content of the prior art;

- b. Ascertaining the differences between the prior art and the claims at issue;

- c. Resolving the level of ordinary skill in the pertinent art; and

- d. Considering evidence of secondary indicia of nonobviousness (if available). I am not aware of any evidence of

secondary considerations that would support a determination of non-obviousness of the claimed subject matter in the '543 Patent.

- 43. I have been informed that the relevant time for considering whether a claim would have been obvious to a person of ordinary skill in the art is the time of invention. For my obviousness analysis, counsel for Petitioner instructed me to assume that the date of invention for the Challenged Claims is May 22, 2013. My opinions would not change if I assumed a later date of invention.

- 44. I have been informed that a reference may be modified or combined with other references or with a person of ordinary skill in the art's own knowledge if the person would have found the modification or combination obvious. I have also been informed that a person of ordinary skill in the art is presumed to know all the relevant prior art, and the obviousness analysis may take into account the inferences and creative steps that a person of ordinary skill in the art would employ.

- 45. I have been informed that whether a prior art reference renders a patent claim obvious is determined from the perspective of a person of ordinary skill in the art. I have also been informed that, while there is no requirement that the prior art contain an express suggestion to combine known elements to achieve the claimed invention, and while a suggestion to combine known elements to achieve the claimed invention may come from the prior art as a whole or

individually and may consider the inferences and creative steps a person of ordinary skill in the art would employ, as filtered through the knowledge of one skilled in the art, obviousness grounds cannot be sustained by mere conclusory statements and must include some articulated reasoning with some rational underpinning to support the legal conclusion of obviousness.

- 46. In determining whether a prior art reference could have been combined with another prior art reference or other information known to a person having ordinary skill in the art, I have been informed that the following principles may be considered:

- a. A combination of familiar elements according to known

methods is likely to be obvious if it yields predictable results;

- b. The substitution of one known element for another is likely to be obvious if it yields predictable results;

- c. The use of a known technique to improve similar items or methods in the same way is likely to be obvious if it yields predictable results;

- d. The application of a known technique to a prior art reference that is ready for improvement to yield predictable results;

- e. Any need or problem known in the field and addressed by the reference can provide a reason for combining the elements in the manner claimed;

- f. A person of ordinary skill often will be able to fit the teachings of multiple references together like a puzzle; and

- g. The proper analysis of obviousness requires a determination of whether a person of ordinary skill in the art would have a "reasonable expectation of success"—but not "absolute predictability" of success—in achieving the claimed invention by combining prior art references.

- 47. I have been informed that, when a work is available in one field, design alternatives and other market forces can prompt variations of it, either in the same field or in another. I have been informed that if a person of ordinary skill in the art could have implemented a predictable variation and would have seen the benefit of doing so, that variation is likely to have been obvious. I have been informed that, in many fields, there may be little discussion of obvious combinations, and in these fields market demand—not scientific literature—may drive design trends. I have been informed that, when there was a design need or market pressure and there are a finite number of predictable solutions, a person of

ordinary skill in the art would have had a good reason to pursue those known options.

- 48. I have been informed that the law permits the application of "common sense" in examining whether a claimed invention would have been obvious to a person skilled in the art. For example, I have been informed that combining familiar elements according to known methods and in a predictable way may suggest obviousness when such a combination would yield nothing more than predictable results. I understand, however, that a claim is not obvious merely because every claim element is disclosed in the prior art and that a party asserting obviousness must still provide a specific motivation to combine or modify the references as recited in the claims and explain why one skilled in the art would have reasonably expected to succeed in doing so.

- 49. I have been informed that there is no rigid rule that a reference or combination of references must contain a "teaching, suggestion, or motivation" to combine references. But I also understand that the "teaching, suggestion, or motivation" test can be a useful guide in establishing a rationale for combining elements of the prior art. I have been informed that this test poses the question as to whether there is an express or implied teaching, suggestion, or motivation to combine prior art elements in a way that realizes the claimed invention, and that it seeks to counter impermissible hindsight analysis.

50. I have been informed that, in an obviousness analysis, prior art must be analogous prior art to the patent being considered. I have been informed that a prior art reference is considered to be analogous, or in the same field of art, if the reference is either (1) in the same field of endeavor as the challenged patent, regardless of the problems the challenged patent and the prior art address, or (2) reasonably pertinent to the particular problem being solved by the challenged patent.

### VI. TECHNOLOGY BACKGROUND AND STATE OF THE PRIOR ART

### A. Photodetectors

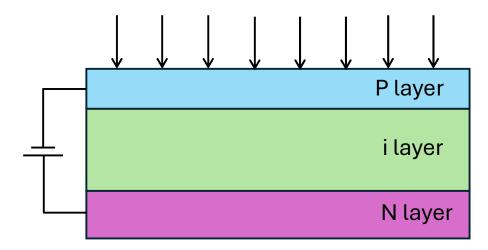

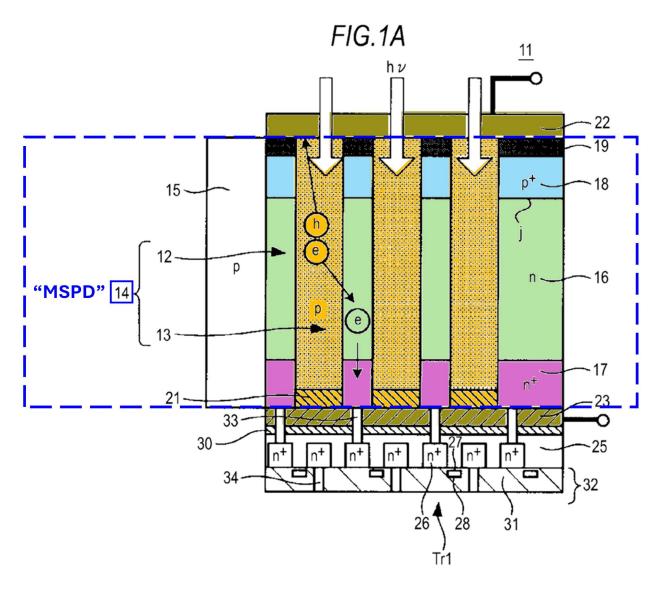

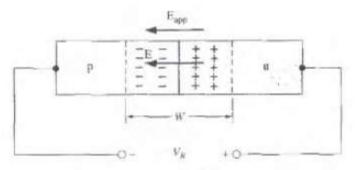

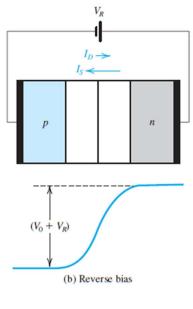

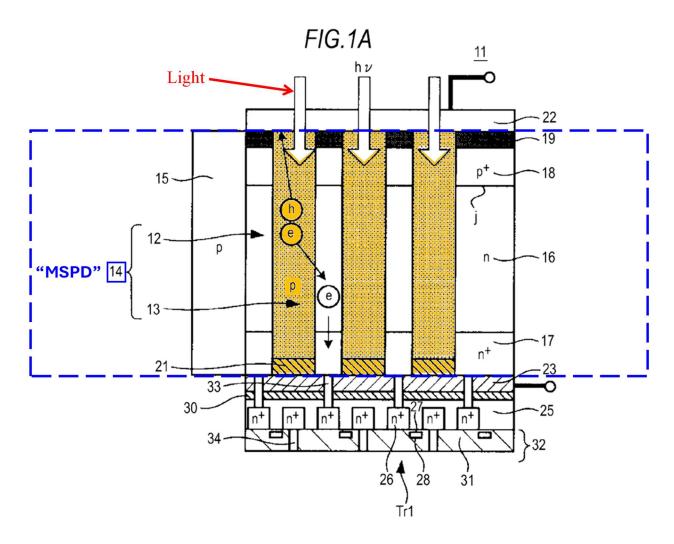

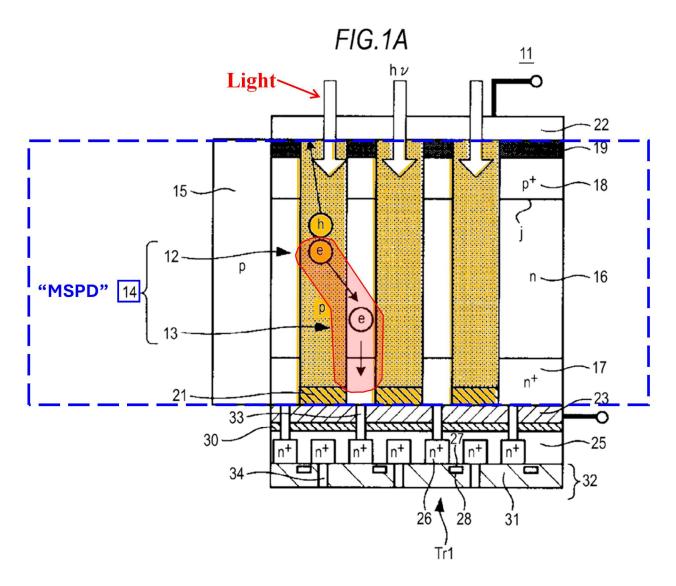

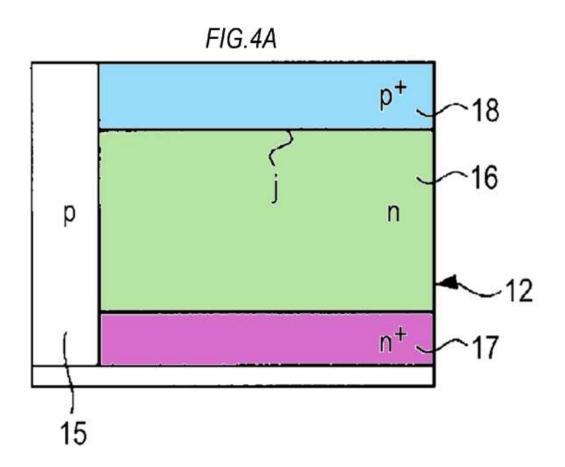

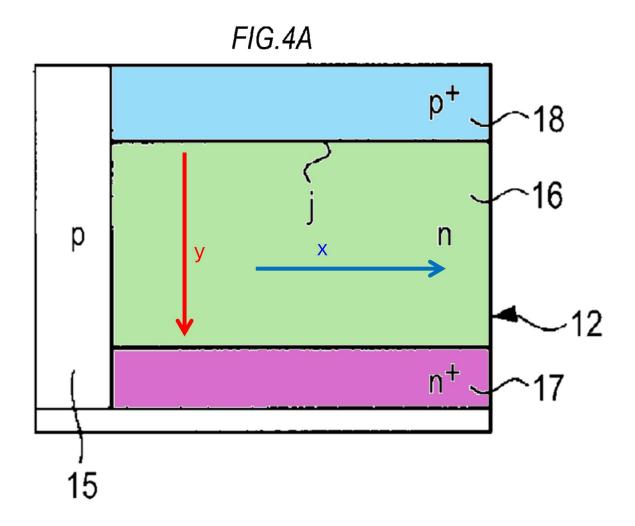

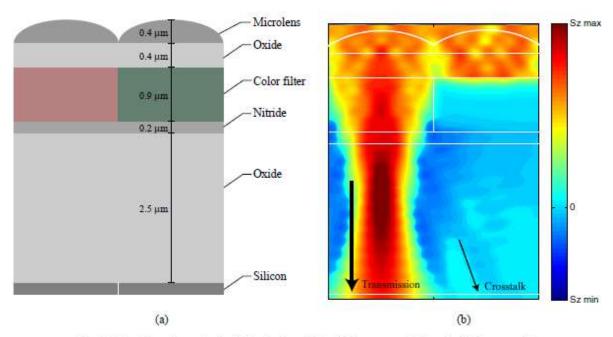

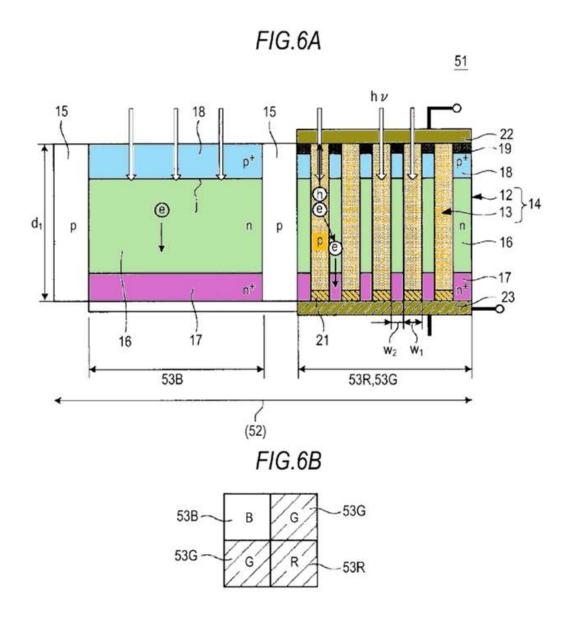

51. A photodetector is a semiconductor device that transforms photons into electrical signals, enabling electrical circuits to detect and measure incident light. As illustrated below, a PiN photodetector is a specific type of photodiode characterized by an intrinsic (undoped) layer positioned between highly doped P-type and N-type semiconductor layers (hence the name "PiN"):

52. When light enters the photodetector, photons are absorbed in the intrinsic layer, generating electron-hole pairs. Applying a negative bias across the photodetector causes the separated electrons to move towards the N-type layer and the holes towards the P-type layer, producing a measurable photocurrent.

### **B.** Microstructure-Enhanced Photodetectors

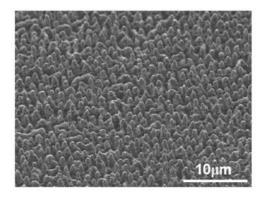

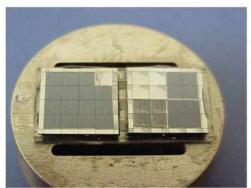

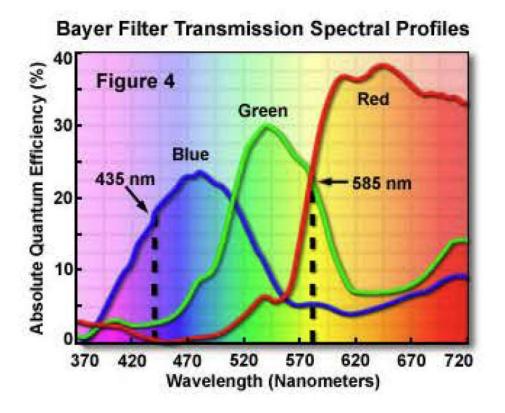

53. Conventional silicon photodetectors exhibit high responsivity at wavelengths of light less than about 850 nm. Ex. 1010, 1. The prior art recognized that tailoring the microstructure of silicon can extend the operability of these photodetectors to longer wavelengths, such as infrared. For instance, etching the surface of a silicon photodetector to create micron-sized pillars or grooves was known to enhance a photodetector's responsiveness at longer wavelengths. Ex. 1010, 1-2; Ex. 1011, 1-6. The images below illustrate photodiodes with laser-etched microstructures designed to enhance their responsiveness at longer wavelengths.

FIG. 1. Scanning electron micrographs of microstructured Si surface.

Fig. 1. (Color online) Picture of two microstructured APD arrays prior to packaging. Structuring was performed with an 800 nm fs laser operating at a fluence of  $3.5 \, \mathrm{kJ/m^2}$  in an atmosphere of SF<sub>6</sub>. The array on the right had four different structured regions with a pulse number ranging from 0 to 300. The shiny area is the bare

Ex. 1010, 1 (left); Ex. 1011, 2 (right).

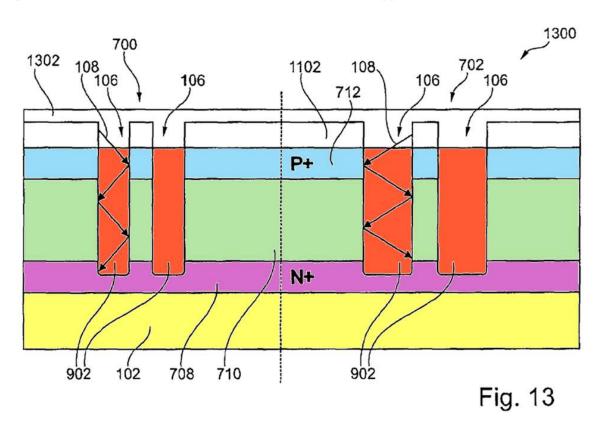

54. Photodetectors featuring microstructures enhanced by etched holes were widely known and utilized well before the purported invention. For example, *NXP* (Ex. 1006) discloses a single-chip device 1300 where a silicon PiN photodiode is integrated with CMOS signal processing circuitry (not shown in Figure 13 below) on the same substrate 102. *NXP*, ¶¶[15], [32], [42], [85].

*NXP*, Fig. 13.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> All color and colored annotations in the figures of this Declaration have been added.

- 55. The PiN photodiode above includes an intrinsic layer 710 disposed between an N<sup>+</sup> layer 708 and a P<sup>+</sup> layer 712 and holes or pores 106 formed on the PiN layers by etching. *NXP*, ¶¶[77]-[78]. *NXP* discloses that the presence of pores 106 in the PiN photodiode increases the quantum efficiency of the photodiode. *NXP*, ¶¶[13], [15], [38]. Quantum efficiency is a measure of how effectively the photodiode converts incoming optical energy into electrical signals. *See* Ex. 1012, 4; Ex. 1013, 4.

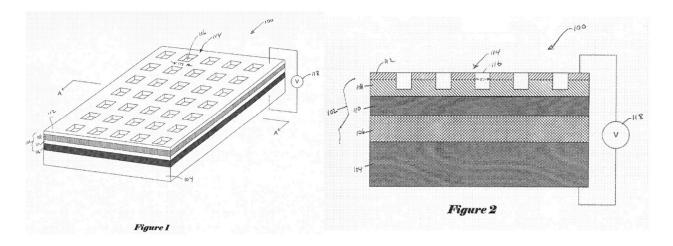

- 56. As another example, *Wang* (Ex. 1007) discloses a photonic device 100 comprising a PiN structure with a stacked p-semiconductor region 108, intrinsic semiconductor region 110, and an n-semiconductor region 106. *See Wang*, ¶[28], Figs. 1-2. A thin doped region 112 overlays the surface of the p-region 108, and a periodic array of holes or recesses 116 extends into the PiN structure through the overlying region 112. *Wang*, ¶¶[29]-[32].

Wang, Figs. 1, 2.

# C. Photodetectors and Processing Circuitry on a Single Substrate

- 57. The integration of photodetectors and signal processing circuitry on a single substrate to form a single-chip device was known long before the purported invention date of the '543 Patent. Ex. 1012, 1-14; Ex. 1013, 1-8; Ex. 1014, 1-2. For instance, *NXP* teaches that integrating signal processing circuitry and the photodiode on the same substrate "may be more reliable than a discrete solution" and result in a smaller package, which is advantageous for mobile applications. *NXP*, ¶¶[16], [32], [37].

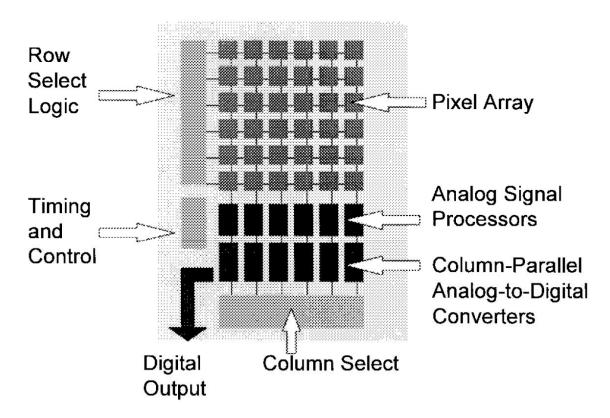

- 58. Beginning in late 1980s, advancements in CMOS technology enabled the fabrication of both photodetectors and signal processing electronics on the same substrate. Ex. 1012, 2-3, 10. For example, researchers at NASA's Jet Propulsion Laboratory developed the CMOS active pixel sensor ("APS"), which integrated a photodiode, amplifier, and signal processing circuitry within each pixel of an image sensor. Ex. 1012, 2-3. This allowed for on-chip conversion of light to electrical signals and immediate processing. Ex. 1012, 2-3; Ex. 1013, 4. This CMOS APS is shown below:

Fig. 2. CMOS APS integrates timing and control, ADC, and other circuitry on the same chip.

Ex. 1013, 3.

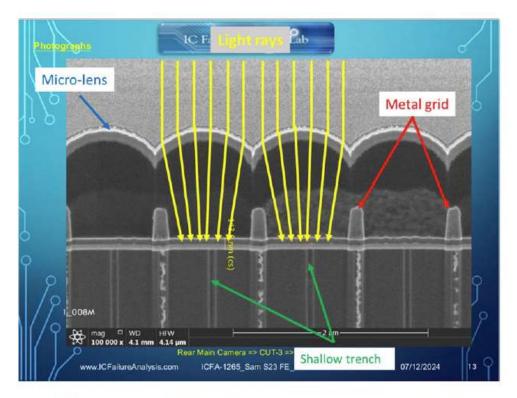

- 59. The integration of the photodiode and processing circuitry on the same chip reduced power consumption, lowered manufacturing costs, and allowed for smaller, more efficient imaging devices. Ex. 1012, 3, 10, 12; Ex. 1013, 8.

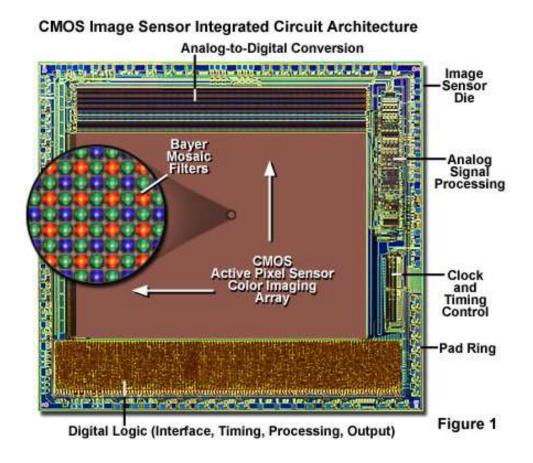

- 60. By the early 2000s, APS technology was prevalent in consumer electronics such as digital cameras, smartphones, and webcams. Ex. 1012, 1-3; Ex. 1015, 9. An image of a CMOS APS image sensor die is shown below.

Ex. 1015, 1.

- 61. This image sensor die includes an array of photodiodes (640 x 480 pixels) located in the large reddish-brown central area of the chip and analog signal processing circuitry to collect and interpret the signals generated by the photodiode array. Ex. 1015, 2-3, Fig. 1.

- 62. A three-dimensional cutaway drawing of the above image sensor is shown below, illustrating a single photodiode and associated transistors that process the signals produced by the photodiode on a single substrate. Ex. 1015, 3-5.

Figure 3

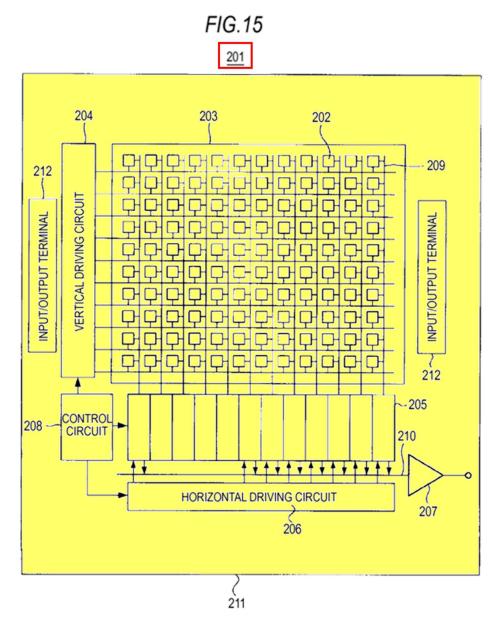

# Amplifier Transistor Column Bus Transistor Silicon Substrate Potential Well

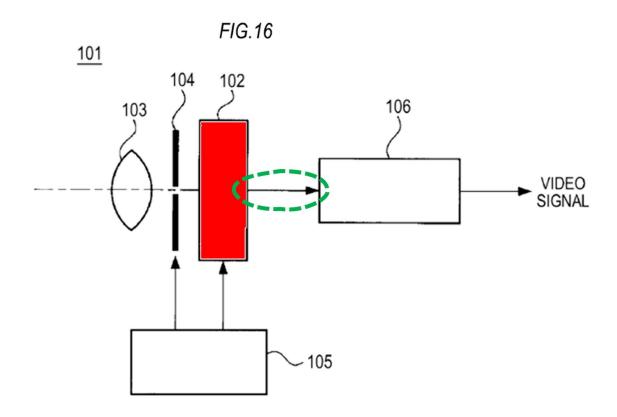

Ex. 1015, 3.

- 63. To focus the incident light on the photodiode, the photodiode is positioned beneath a microlens and a color filter to capture color information from the incident light. Ex. 1015, 3-4, Fig. 3.

- 64. Well before the purported invention date of the '543 Patent, numerous published references disclosed single-chip devices integrating photodetectors and signal processing circuitry on a single substrate. For example, *Kuboi* (Ex. 1004), discussed below, describes such a device. *Infra* VIII.A. Moreover, *Kuboi* discloses all features of the challenged claims. *Infra* XI.A. *Shinohara* (Ex. 1005) discloses a

similar single-chip device incorporating photodetectors and signal processing circuitry. *See Shinohara*, Figs. 1-2, ¶¶[51]-[63].

Shinohara, Figs. 1, 2.

65. Like *Kuboi*'s imaging device 201 (*see Kuboi*, Fig. 15, ¶¶[48]-[54]), *Shinohara*'s imaging device 1 features a pixel region 3 with a two-dimensional pixel array 2 and a peripheral circuit portion integrated on the same semiconductor substrate 11. *See Shinohara*, ¶[51]; *see infra* VIII.A. In *Shinohara*, each pixel 2 contains a photoelectric conversion portion and four pixel transistors, similar to *Kuboi*. *Shinohara*, ¶[51]; *see Kuboi*, ¶[48]; see *infra* VIII.A. Additionally, akin to *Kuboi*, *Shinohara*'s peripheral circuit portion includes various logic circuits, such as a vertical drive circuit 4, a column signal processing circuit 5, a horizontal drive

circuit 6, an output circuit 7, and a control circuit 8. *Shinohara*, ¶[52]; *see Kuboi*, ¶[49]; see *infra* VIII.A. In *Shinohara*'s imaging device 1, the photodiode-based photoelectric conversion portion and pixel transistors are formed on a single semiconductor substrate (substrate 22), along with the logic circuits of the peripheral circuit portion. *See Shinohara*, ¶¶[3]-[4], [58], [81].

### VII. THE ' 543 Patent

- A. Alleged Invention of the '543 Patent

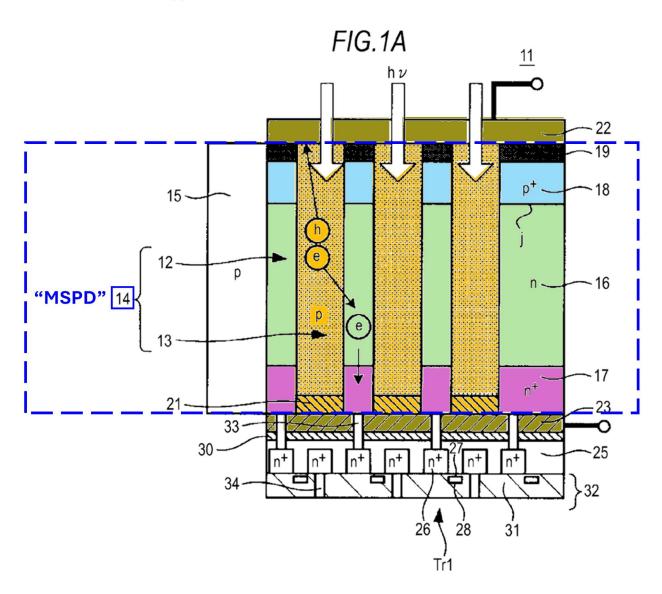

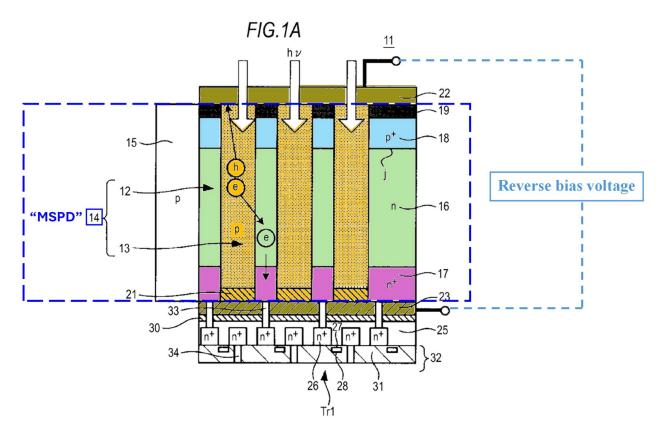

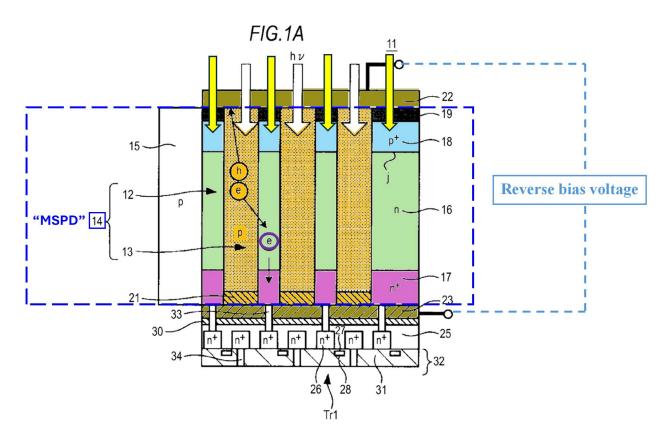

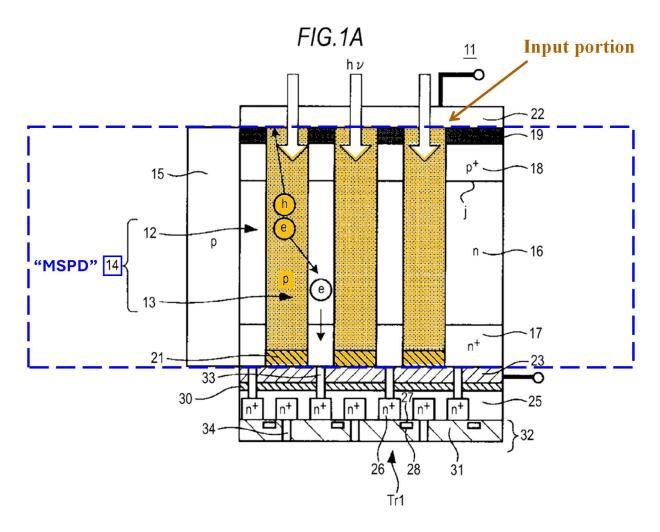

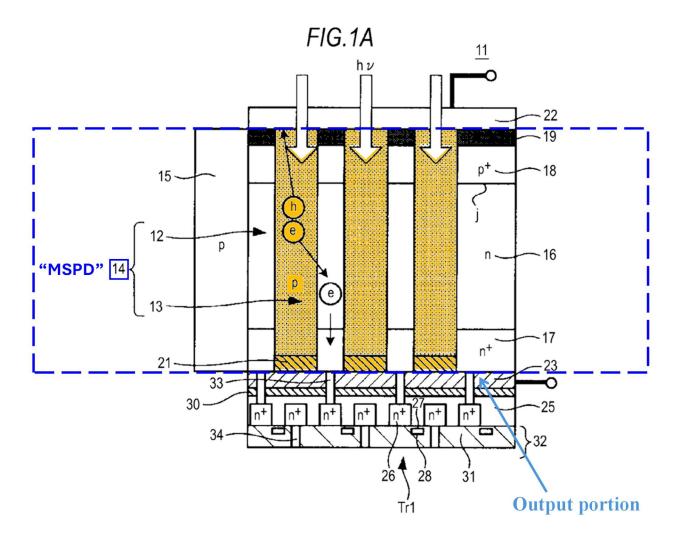

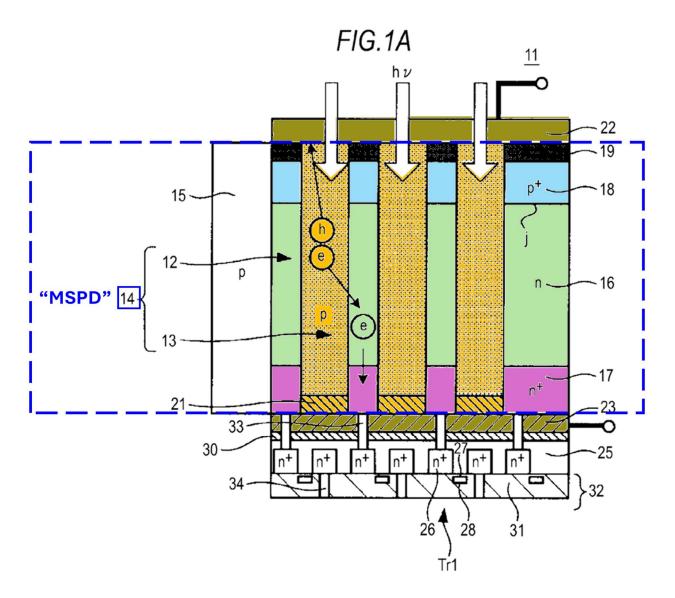

- 66. The '543 Patent details a single-chip device that integrates photodetectors (referred to as MSPDs and MSAPDs) with CMOS active electronic circuits on a single substrate. '543 Patent, 2:64-67, 4:65-5:5, 6:24-29.

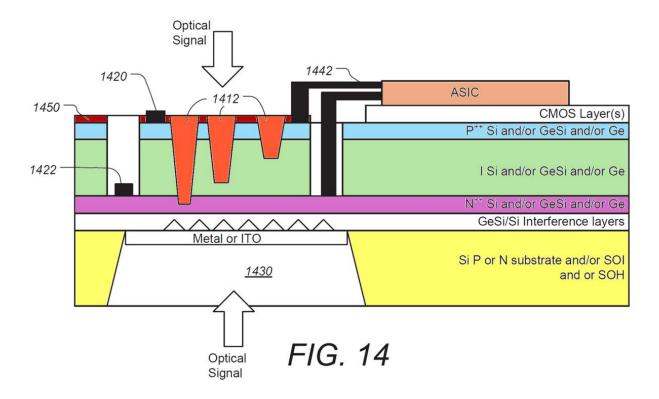

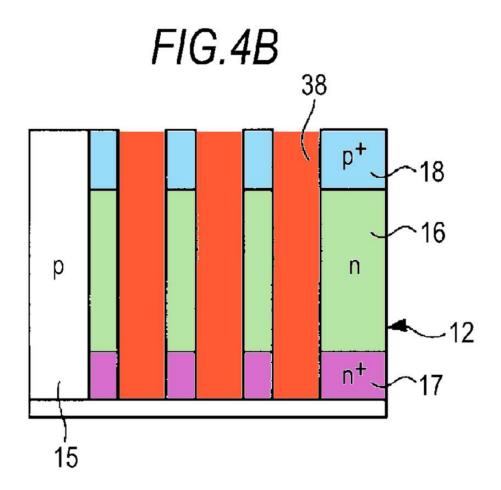

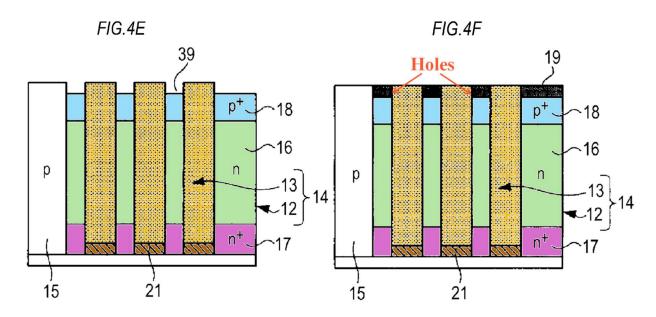

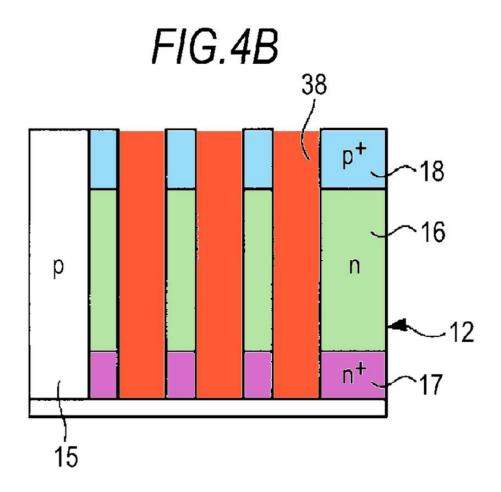

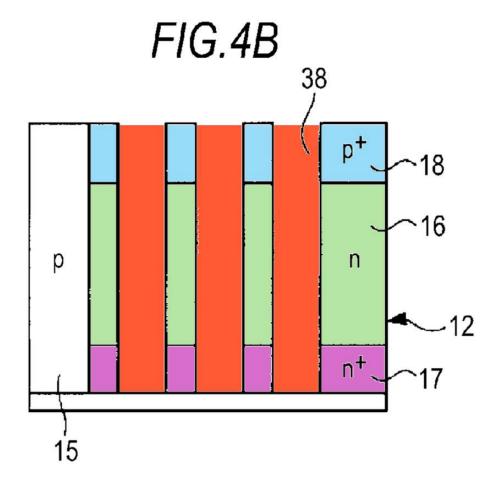

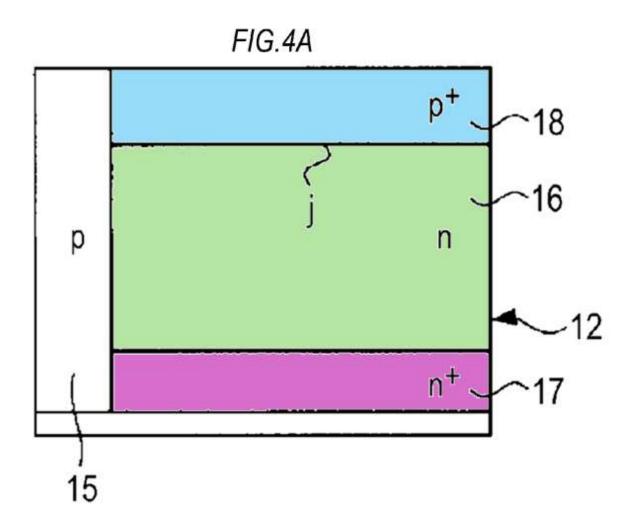

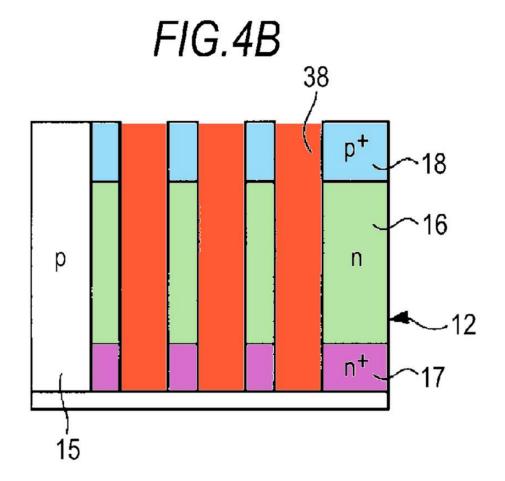

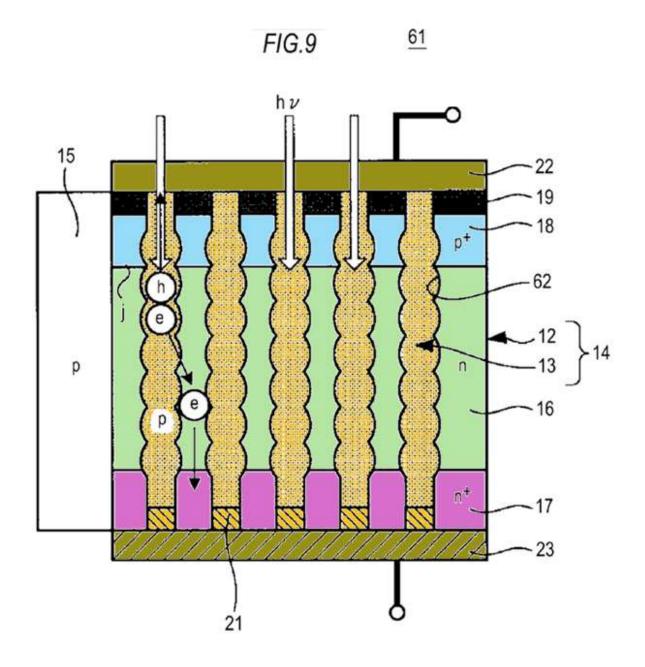

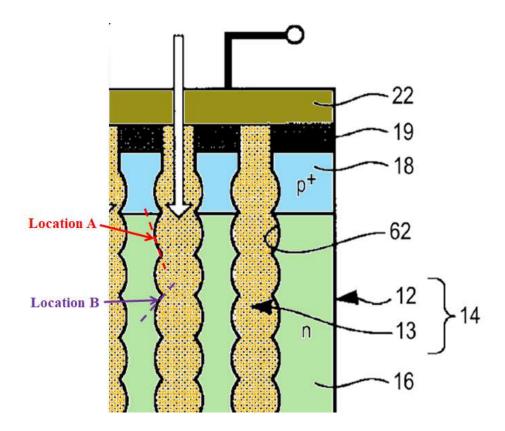

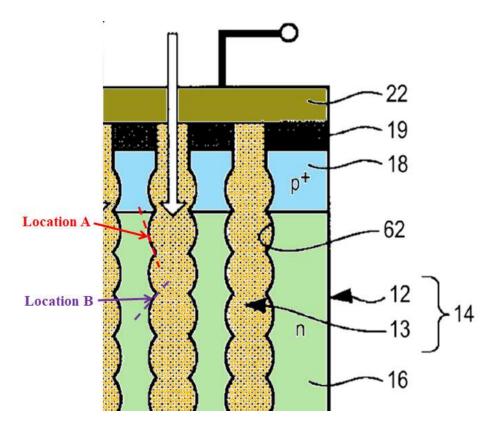

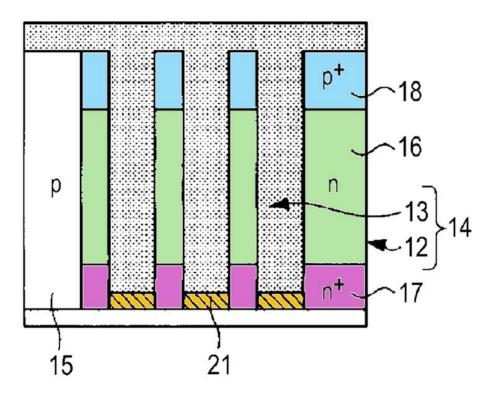

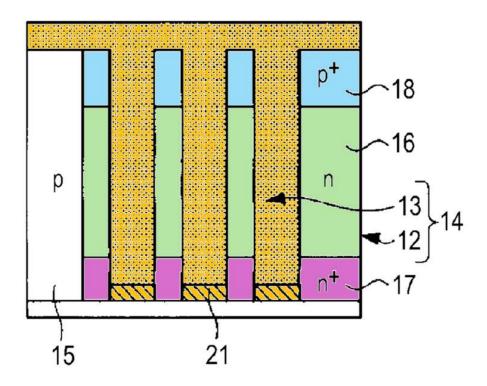

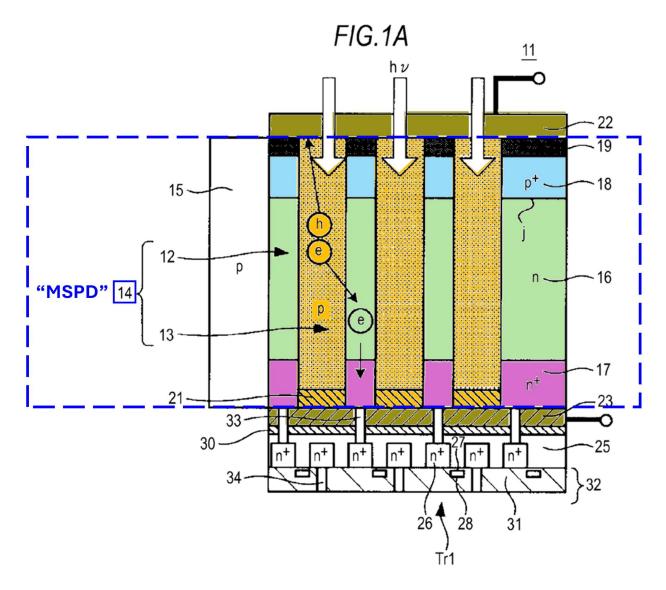

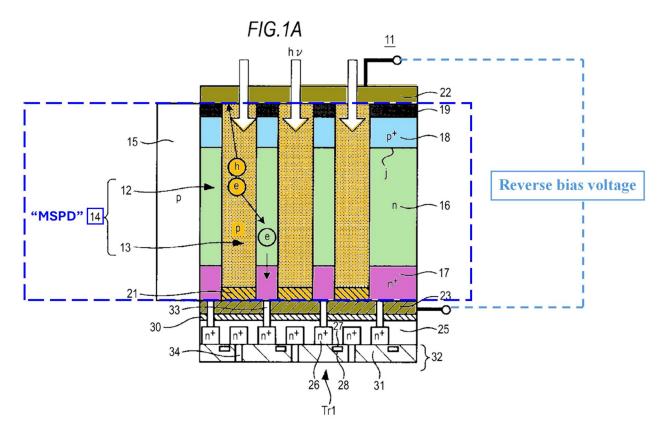

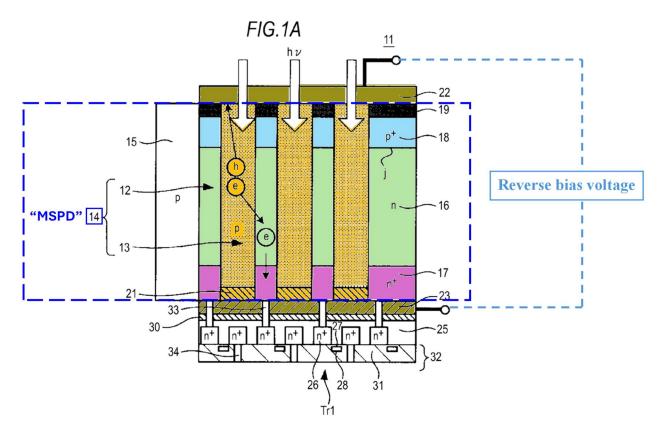

- 67. The photodetectors disclosed by the '543 Patent include a silicon substrate with a first layer (a P layer), a very low doped N or P layer called the intermediate layer (or i layer), and a second layer (an N layer) with holes etched in one or more of the PiN layers. '543 Patent, 22:9-41, 16:38-42, 26:29-27. The '543 Patent discloses that optical signals impinge on the top and/or bottom surfaces of the photodetectors. '543 Patent, 16:23-27. According to the '543 Patent, because of the holes, light interacts with the absorbing layer(s) for a longer length of time, resulting in enhanced light absorption and a larger external quantum efficiency over a similar structure without holes. '543 Patent, 15:48-56. Figure 14, which is shown below, depicts the photodetector disclosed by the '543 Patent:

'543 Patent, Fig. 14, 10:60-62, 26:42-44.

68. The photodetector of the '543 Patent is monolithically integrated with signal processing circuits (such as ASIC) on the same substrate to form a single-chip device. '543 Patent, 19:2-6, 23:43-46, 26:42-44. Notably, the '543 Patent recognizes that it was well known to integrate photodetectors with signal processing circuits on a single silicon substrate to reduce cost and improve performance. '543 Patent, 28:58-29:3, 32:50-67, 47:11-21.

# **B.** Prosecution History

69. The application that resulted in the '543 Patent (or the "'543 application") was filed on March 8, 2019, as a continuation application of the '700

Patent, and claiming priority to several patent applications, the earliest of which was filed on May 22, 2013. Ex. 1044, 257-638.

- 70. The originally-filed claims of the '543 application closely resemble those issued in the '700 Patent (Ex. 1001). *See* Ex. 1044, 632-633; '700 Patent, 118:25-119:4. Originally filed independent claim 113 of the '543 application—now independent claim 1 of the '543 Patent—is presented below, with changes from the independent claim of the '700 Patent indicated using underlines and strikethroughs.

- 113. A single-chip device comprising an integrated combination of a microstructure-enhanced photodetector (MSPD) configured for reverse-bias operation and an active electronic circuit, both formed on or in a single substrate and configured to receive an optical input that in cross-section is substantially continuous <u>spatially</u>, convert the optical input to an electrical output, and process the electrical output into a processed output, wherein:

the MSPD on or in said single substrate comprises an intermediate layer region, a first layer region at one side of the intermediate layer region, and a second layer region at an opposite side of the intermediate layer region, wherein:

each of the <u>layers regions</u> comprises Silicon, Germanium, or an alloy thereof;

at least one of said <u>layers regions</u>, or an overlying covering <u>layer</u>

<u>region</u> that may be present, has holes intentionally formed therein,

<u>extending in directions transverse to the layers</u>;

each of the first and second layers regions comprises a doped material;

the intermediate <u>layer region</u> comprises a material that is less doped than at least one of the first and second <u>layers regions</u> or is undoped, wherein the degree of doping is the same or different for different positions in the intermediate <u>layer region</u>;

an input portion configured to concurrently receive at a plurality of said holes said optical input that has said substantially continuous cross-section; and

an output portion configured to provide said electrical output from the MSPD;

the MSPD includes reverse-bias <u>electrodes</u> <u>contacts</u> coupled therewith to establish an electrical field therein when energized to thereby

sweep in a selected direction electrical charges generated in the MSPD by said optical input;

said reverse-bias electrodes being free of a pattern of openings that matches said holes; and

the active electronic circuit on or in said single substrate is configured to process the electrical output from the MSPD by applying thereto:

amplification to form said processed output from the singlechip device;

processing other than or in addition to amplification to form said processed output from the single-chip device; and

routing to one or more selected destinations; and a communication channel on or in said single-chip device, configured to deliver the electrical output from the MSPD to the active electronic circuit.

Compare Ex. 1044, 632-633, with '700 Patent, 118:25-119:4.

71. Regarding the limitation highlighted in the red box above, during prosecution of the '700 Patent, the Examiner indicated that the phrase "overlying covering layer that may be present ... merely states [that] the overlying layer [is] an optional component," and does not require the presence of this overlying layer. Ex. 1003, 387. Later, during prosecution of the '543 Patent, the same Examiner

noted this claim limitation could introduce "potential 112 scope of enablement issues" as it might be interpreted to restrict the presence of holes solely to the covering region, an interpretation unsupported by the disclosure. Ex. 1044, 124-125. To address this concern, the Examiner proposed—and the Patent Owner agreed—to amend "overlying covering region that may be present" to "optional overlying covering region." Ex. 1044, 124-125, 136. Thus, in my opinion, the Examiner viewed the "*optional* overlying covering region" to be an "overlying covering region that may be present" without mandating its presence.

72. The claims were then allowed with the Examiner noting that the "prior art discloses a single chip device comprising a microstructure enhanced photodetector and an electronic circuit, but fails to disclose the specific characteristic recited in the claims." Ex. 1044, 135-137. However, the Examiner did not consider *Kuboi*, which teaches all of these characteristics and renders the challenged claims unpatentable.

### C. Claim Construction

73. I have been instructed that the "intrinsic record" includes the patent itself, including the claims, description, and figures (Ex. 1042), and the patent's prosecution history (Ex. 1044)—i.e., the record of proceedings at the U.S. Patent and Trademark Office ("Patent Office") concerning the patent. I understand that, like the claims and written description, the prosecution history provides evidence

to a person of ordinary skill in the art of how the inventor intended his patent to be understood, and how the Patent Office understood the patent. I understand that the inventor is permitted to apply a special definition to the terms or to limit the scope of claim terms in his patent claims, which may differ from the term's plain and ordinary meaning. That special definition or limitation on scope may be provided in the patent's written description, the patent's prosecution history, or both.

- 74. I understand that claim interpretation may also be informed by "extrinsic evidence" (that is, evidence outside of the patent record itself). I have been informed that extrinsic evidence may include dictionaries, technical treatises, and other materials evidencing the meaning of a claim term and the understanding held by a person of ordinary skill in the art (POSITA) in the relevant time period.

- 75. I have been asked for purposes of this declaration to apply the plain and ordinary meaning of the claim terms as they would have been understood by a person of ordinary skill in the art at the earliest claimed priority date of the '543 Patent. Based on my review of the materials and my personal knowledge and experience, I have considered each term of the '543 Patent as it would have been understood by a person of ordinary skill in the art at the earliest claimed priority date of the '543 Patent (May 22, 2013).

### VIII. SUMMARY OF THE PRIOR ART

### A. Kuboi

- 76. *Kuboi*, titled Solid-State Imaging Device, Manufacturing Method Thereof, and Electronic Apparatus, was filed on August 19, 2011, and published as U.S. Patent Publication No. 2012/0049044 on March 1, 2012. I understand that *Kuboi* is prior art to the '543 Patent.

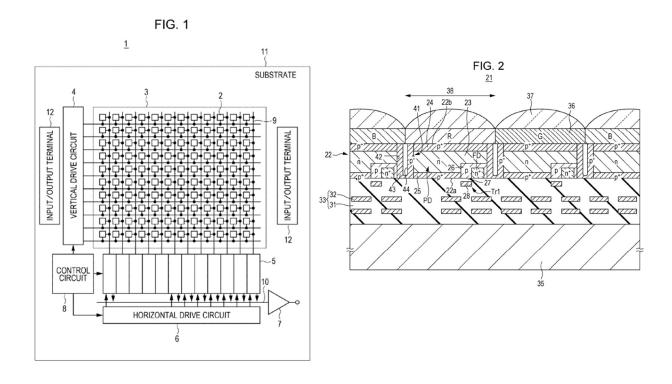

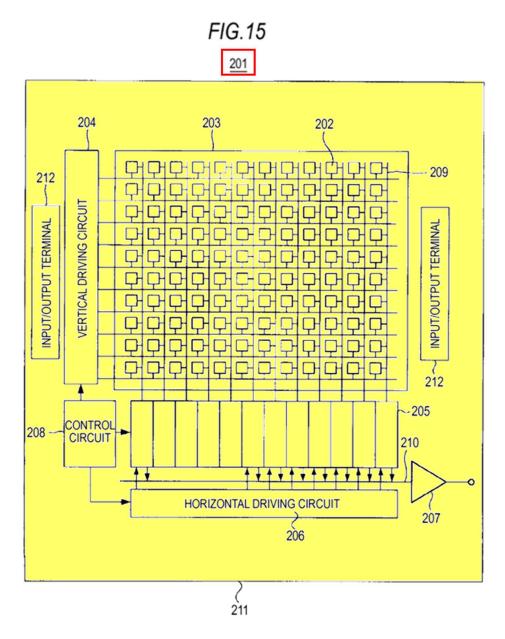

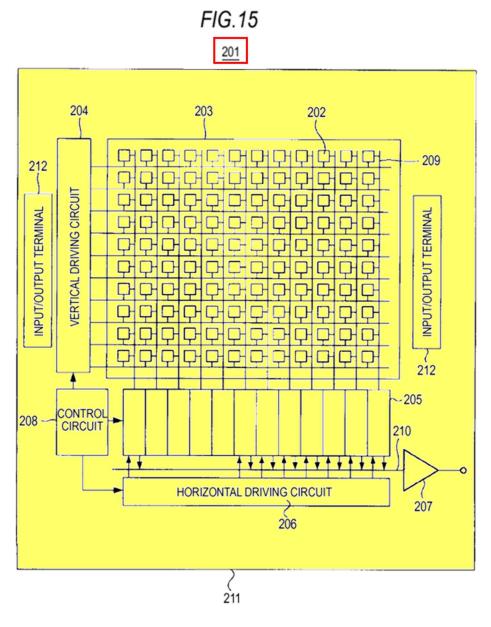

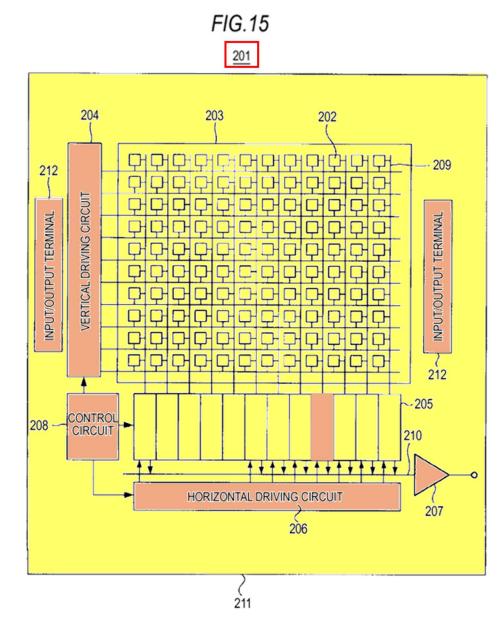

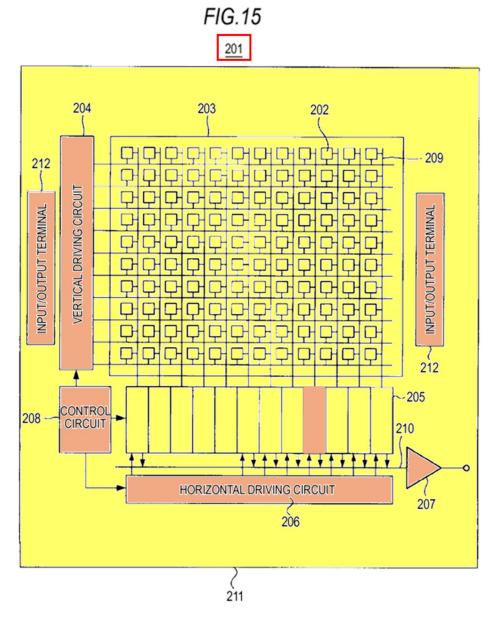

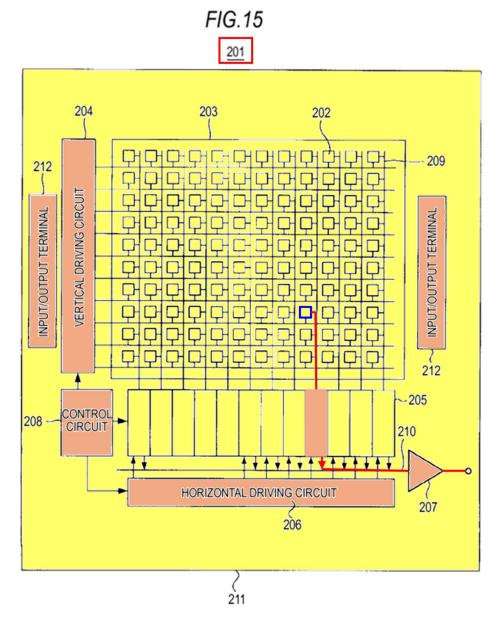

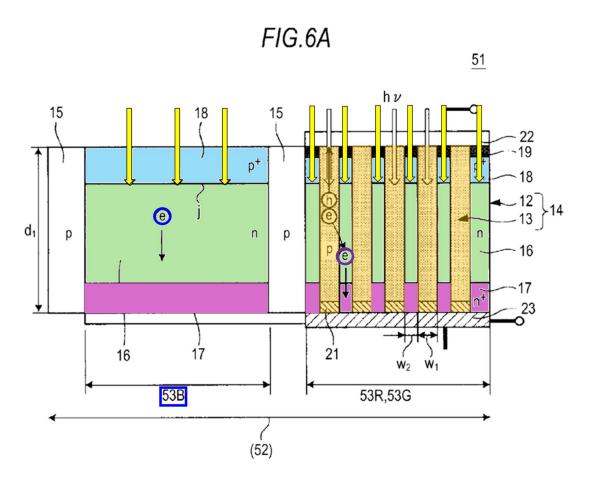

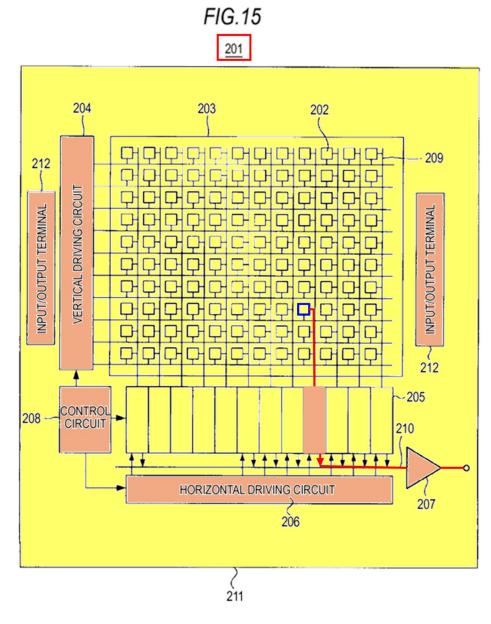

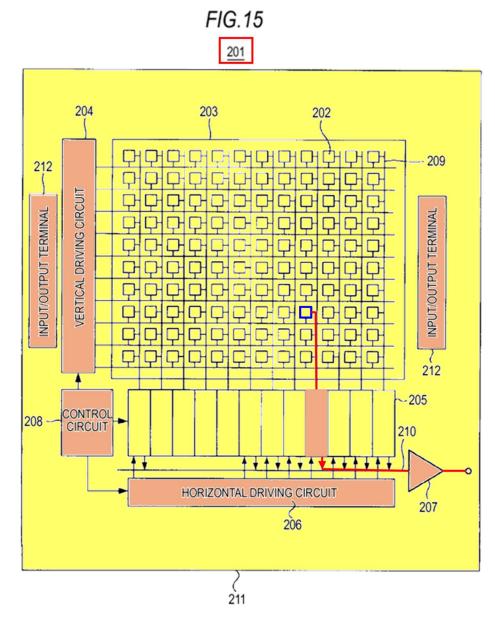

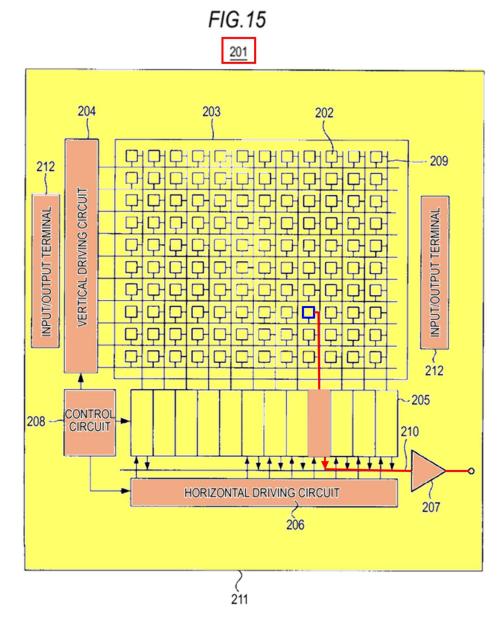

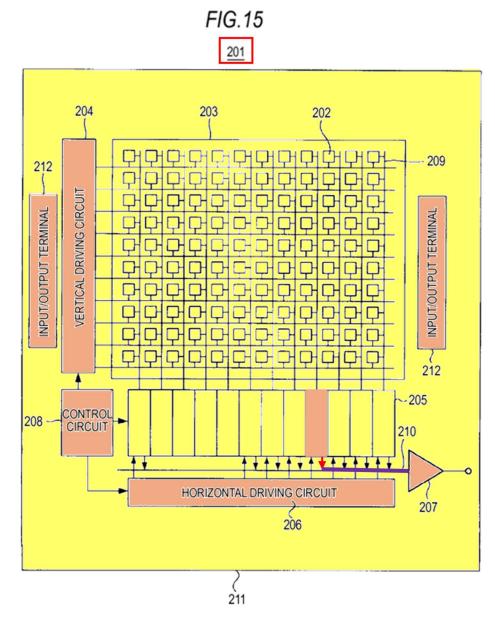

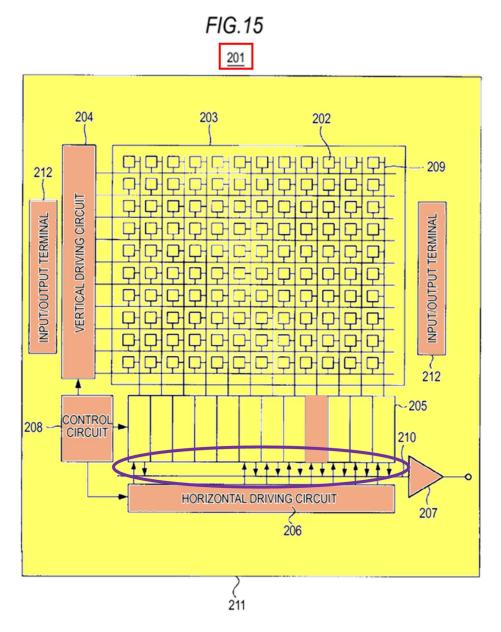

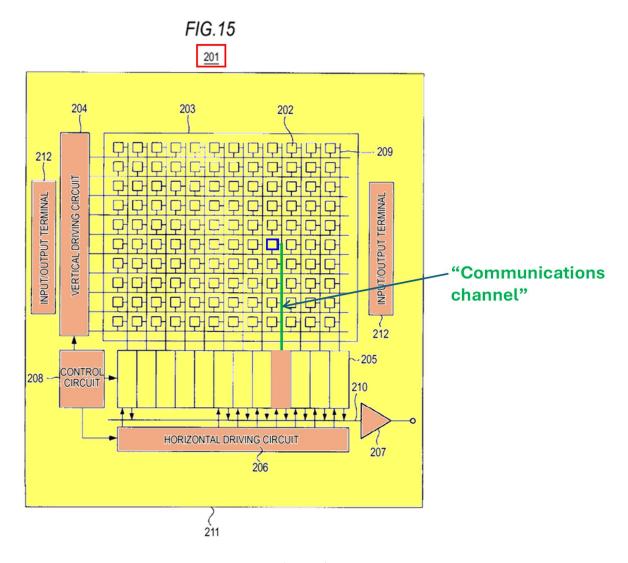

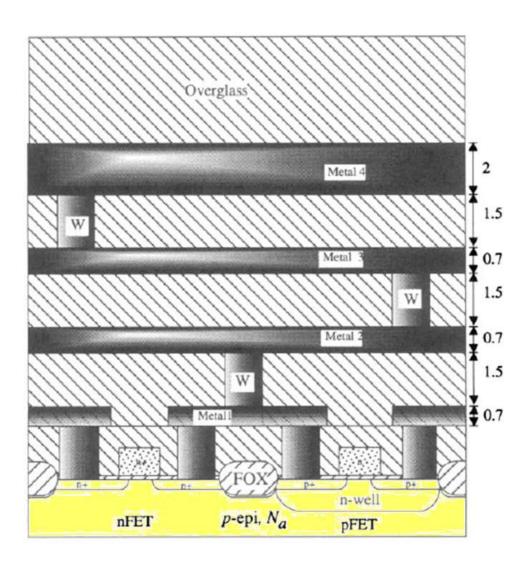

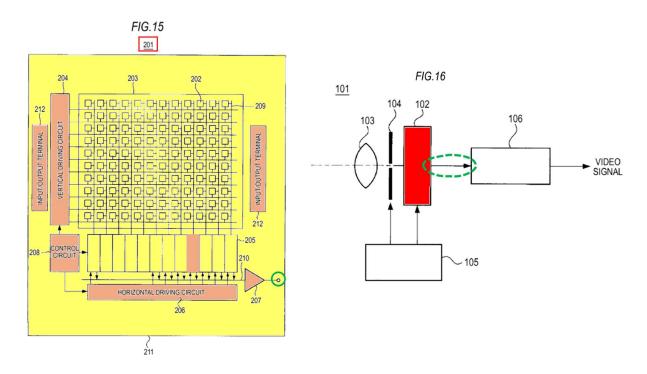

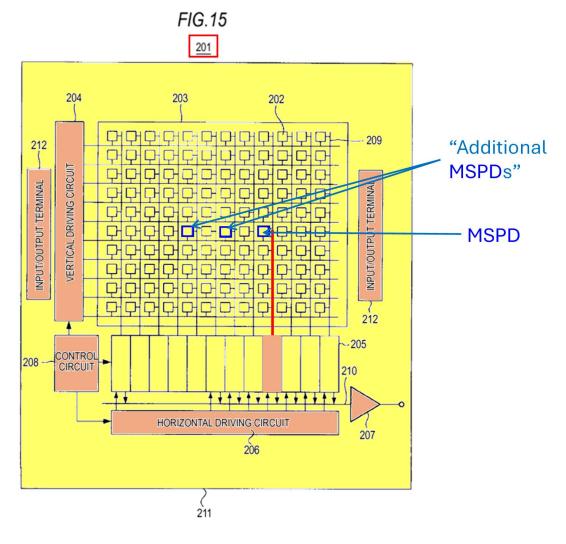

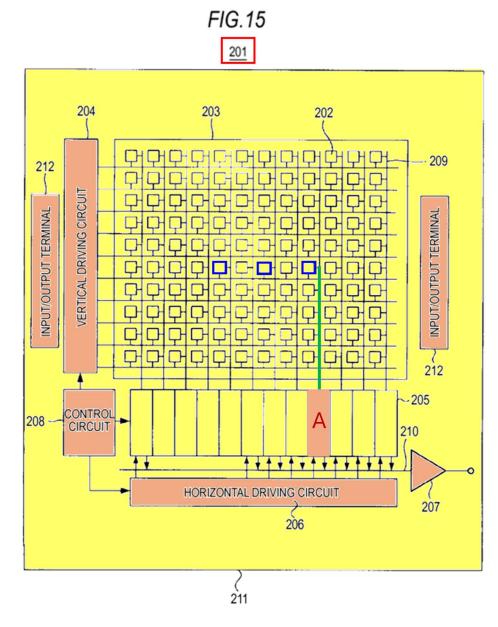

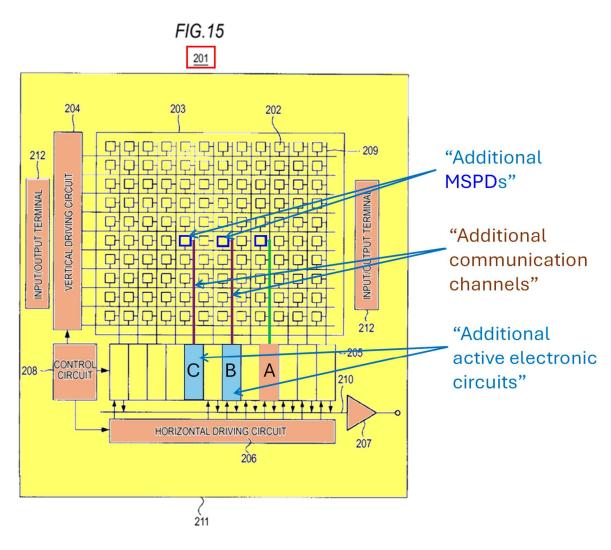

- 77. *Kuboi* discloses a CMOS solid-state imaging device 201 that includes a pixel region 203 and a peripheral circuit portion on a single semiconductor substrate 211. *Kuboi*, ¶[48], Fig. 15.

Kuboi, Fig. 15.